CN1004307B - 动态分配局部/全局存贮器系统 - Google Patents

动态分配局部/全局存贮器系统 Download PDFInfo

- Publication number

- CN1004307B CN1004307B CN85107534.7A CN85107534A CN1004307B CN 1004307 B CN1004307 B CN 1004307B CN 85107534 A CN85107534 A CN 85107534A CN 1004307 B CN1004307 B CN 1004307B

- Authority

- CN

- China

- Prior art keywords

- memory

- address

- processor

- node

- access

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired

Links

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/0223—User address space allocation, e.g. contiguous or non contiguous base addressing

- G06F12/0292—User address space allocation, e.g. contiguous or non contiguous base addressing using tables or multilevel address translation means

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/06—Addressing a physical block of locations, e.g. base addressing, module addressing, memory dedication

- G06F12/0646—Configuration or reconfiguration

- G06F12/0692—Multiconfiguration, e.g. local and global addressing

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

Abstract

动态地把存贮器系统划分为可被多个与网络相联的处理器有效存取的全局存贮器和可被单个处理器有效存取的局部存贮器的设备,包括用一个处理器交错存取存贮器引用的装置,受每个处理器控制的,用以控制交错存取存贮器引用的装置的装置,和动态地把存贮器引用指向存贮器第一和第二部分的装置。

Description

本发明与数据处理器存贮器系统有关,更具体地说,与用于多处理器系统的动态存贮器系统有关。

美国专利4,365,295表明了一种含有一个存贮器系统的多处理器系统,其中每个处理器模块的存贮器被划分成四个逻辑地址区。这个存贮器系统包括一个变址图(map),该变址图把逻辑地址变换为物理地址,当需要实现一个虚拟存贮器系统时,该变址图与多处理器系统一起运行,把页面从辅助存贮器导入到主存贮器之中。

这个专利说明了一种传统的存贮器变址系统,它并未阐述出单个的或多个处理器对于存贮器的有效存取,这种有效存取包括用某个处理器交错存取引用那些存贮器,以及动态地将存贮器引用指向每个存贮器模块的全局或局部部分。

美国专利4,228,496表明了一种含有上述存贮器系统的多处理器系统,以完成一种虚拟存贮器系统。

然而,这个专利描述了一种传统的存贮器变址系统,它并未阐述单个或多个处理器对于存贮器的有效存取,这种有效存贮包括用某个处理器交错存取引用那些存贮器。并且动态地将存贮器引用指向每个存贮器模块的全局或局部部分。

美国专利4,174,514表明了一种对于图象处理等方面的数据矩阵进行领域变换(neighborhood transfor-mations)的装置,通过使用多个串联的领域处理器(这些处理器同时对某一单个数据矩阵的相邻的分隔部分起作用),在经济地使用存贮器的同时,达到了比串联处理器还高的处理速度。

这个专利表明的多处理器系统没提供任何措施使所有的处理器对一个共同的全局存贮器进行存取。

美国专利4,121,286表明了一种在一个多处理器环境中对存贮器空间进行分配和再分配的装置。

这个专利描述了一种传统的存贮器变址系统,它并未阐述出单个的或多个处理器对于存贮器的有效存取,这种有效存取包括用某个处理器交错存取引用那些存贮器,并且动态地将存贮器引用指向每个存贮器模块的全局或局部部分。

美国专利3,916,383表明了一种资源分配电路,它以时间片为基础有选择地启动单个的处理器,在这儿,一个时间片大约等于系统的存贮时间。这种资源分配电路包括一个优先级网络,它接收根据单个处理器的需要而从处理器发来的实时公共资源使用请求,指定所接收请求的优先级别,然后相应于此优先权级别,改变处理器的其它的顺序启动。这个专利表示了一种在一个中心处理器内具有几个独立的数据处理器的系统,在通常的概念中,它不是一个真实的多处理器系统。

本发明涉及一种系统,它具有一个或多个独立的处理器,形成一个多处理器,其中的存贮器系统被动态地划分为全局存贮器和局部存贮器。

美国专利3,820,079表明了一种多处理器计算机,它以围绕着一个公共控制和数据总线的模块形式构成。对于各个模块的控制功能被分布在这些模块之中,使系统更加具有灵活性。这个专利所表示的系统包括了传统的存贮器变址和交错存取。

与本发明不同的是,这种存贮器变址不对交错存取进行控制,而且对于所有数据而言,该交错存取在所有模块上是一样的。

美国专利3,641,505表示了一种多处理器计算系统,其中若干个处理单元、程序存贮器单元、可变化的存贮器单元和一些输入/输出单元可以有选择地被结合在一起,形成一个或多个独立的数据处理系统。分离成大于一个独立系统的系统或者被手动开关控制或被程序发出的划分信号控制。

这个专利描述了一种传统的存贮器变址系统,它并未阐述出单个或多个处理器对于存贮器的有效存取,这种有效存取包括用某个处理器交错存取引用那些存贮器,并且动态地把存贮器引用指向每个存贮器模块的全局或局部部分。

美国专利3,601,812表明了一种存贮器系统,它用于在几个计算机和一个中央存贮器单元之间进行缓冲,或者在一个计算机和几个小存贮器单元与一个为了更有效地使用该小存贮器单元而设的划分地址表之间进行缓冲。该地址的二进制数字被分解成两个不相交的子集,一个子集被用作为一个缓冲器地址,另一个子集与数据字一起存贮起来,以实现它们的识别。

这个专利讨论了多处理器中对存贮器数据的缓冲,它并未提出一种动态划分的存贮器系统,这种动态划分的存贮器系统包括用一个处理器交错存取引用那些存贮器,并且动态地把存贮器引用指向存贮器的全局或局部部分。

上述的现有技术即没有指示也没有建议出在此所公开的并要求保护的本发明的技术方案。

本发明的一个目的是把一个存贮器系统动态地划分为一个可以被多个处理器有效地存取的全局存贮器和可以被单个处理器有效地存取的局部存贮器,完成此功能所用的方法和设备包括:用一个处理器交错存取存贮器引用的装置;处于每个处理器的控制下的用于控制上述装置(即交错存取存贮器引用的装置)的装置;动态地把存贮器引用指向存贮器的第一或第二部分的装置。

本发明的另一目的是动态地划分如上所述的存贮器系统,完成此功能所用的方法和设备进一步包括:把存贮器的第一部分指定给一个引用处理器,存贮器的第二部分指定给其它的处理器。

本发明的另一目的是动态地划分如上所述的存贮器系统,所用的方法和设备进一步包括以页面为单位分配存贮器的第一装置。

本发明的另一目的是动态地划分如上所述的存贮器系统,所用的方法和设备进一步包括用于以可变段为单位动态地分配存贮器的第二装置。

本发明的另一目的是动态地划分如上所述的存贮器系统,所用的方法和设备进一步包括用所说的控制存贮器分配的第一和第二装置去控制存贮器交错存取的装置。

本发明的另一目的是动态地划分如上所述的存贮器系统,所用的方法和设备进一步包括用一个因子实现交错存取存贮器的装置,该因子等于2的从0到系统的处理结点数目之间的任意次幂。

本发明的另一目的是动态地划分如上所述的存贮器系统,所用的方法和设备进一步包括一个可变宽度位段(Variable-Widthbit-field means)的右旋可变量的装置。该装置用于把存贮器模块(在这些模块上执行交错存取)限定到小于预定最大值的数量。

本发明的另一目的是动态地划分如上所述的存贮器系统,所用的方法和设备进一步包括对跨存贮器的交错存取扫描进行再变址(re-map)的装置,以便对不同的连续的交错存取扫描提供不同顺序的存贮器存取。

因此,本发明包括的方法与设备可以动态地把一个存贮器系统划分为一个全局存贮器和一个局部存贮器,该全局存贮器可以被若干个与网络相连的处理器有效地访问,该局部存贮器可以被单个处理器有效地访问;本发明还包括由一个处理器交错存取存贮器引用的装置;受到每个处理器控制的、用于控制上述装置(即交错存取存贮器引用的装置)的装置;以及动态地把存贮器引用指向存贮器第一或第二部分的装置。

前面所述的以及其它的本发明的目的、特点和优点,可以通过本发明的最佳实施方案的具体叙述和附图的说明得到更清楚的了解。

附图的简要说明如下:

图1是根据本发明的一个多处理器系统的方框图;

图2是根据本发明的一个处理节点的方框图;

图3是一个网络地址图,表示了根据本发明的地址结构;

图4是根据本发明的一页连续变址的地址的图示;

图5是根据本发明的一页交错存取变址地址的图示;

图6表示了局部和全局存贮器的页交错存取;

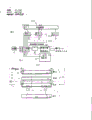

图7是根据本发明的图2所示的一个变址/交错存取块的方框图;

图8是根据本发明的图2所示的一个网络/存贮器接口块的方框图。

在图中,同样的部分被指定以同样的参考号,在不同的具体实施例中的一致的部分被指定以一致的参考号。

本发明允许在运行期间把主存贮器动态地划分为每个处理器的局部存贮器和能被所有的处理器全局存取的存贮器。

现有技术中的多处理器系统提供了:

(1).仅有局部存贮器,而无全局存贮器;

(2).仅有全局存贮器,而无局部处理器;

(3).全局存贮器和固定数量的局部存贮器。

类型(2)中的一些系统有一个固定数量的高速缓冲存贮器形成的局部存贮器,能有效地减少全局存贮器的等待时间,以后将可以看到,本发明不排除使用一个高速缓冲存贮器,总的讲,不排除使用存贮器分级结构。

与上述系统不同,此处所述的本发明的系统允许对存贮器结构动态地进行变更,以适应用户的需要,结果便在更宽的应用范围中实质性地改善了其性能。本发明同样也支持了处理器之间的信息的有效传送,而这种功能在上述第(1)种类型的系统中是由特殊的硬件实现的。

如图1所示,所需要的机器结构包括N个处理结点20,它们与某种通讯网络10相连。在这些结点中包含有处理器和系统的主存贮器,(见图2)。可以使用任何能为在所有结点之间提供通信的网络。

图1中表示了一个互连网络(ICN)10,它与各种结点20连接在一起。本发明不需要任何特殊的互连网络设计,但是所用的网络至少必须有下述功能:

(a).发生在任何一个结点20的信息要能通过网络10,可靠地发送到任何其它的结点20。

(b).信息的发送基于包含在该信息的“结点#”字段(Node#field)中的地址信息。

当与那些各种结点20耦合时,互连网络ICN10的这种信息发送功能必须使任一处理器仅仅通过指定正确的绝对地址,对在任一结点20的任何存贮单元进行访问。本发明的存贮器变址机构(memory-mappingmechanisms)给每个处理器提供了产生这种绝对地址的功能。

图2表示出了某个结点的内容。变址/交错存取(MAP/INTERLEAVE)(M/I)24对处理器(PROC)22发出的存贮器引用的地址按下述方式进行地址变换。

在变址之后使用一个高速缓冲存贮器26以满足一些存贮器引用。此处叙述的本发明不需要使用一个高速缓冲存贮器,它也不限制该高速缓冲存贮器的位置。例如,高速缓冲存贮器26可以位于处理器22和M/I块24之间。

网络/存贮器接口(NET/STORE INTF(NSI))28把高速缓冲存贮器26所不满足的那些引用(假如没有高速缓冲存贮器,则把所有的引用)指向在该结点中的主存贮器30部分,或者通过网络10,指向其它的结节的存贮器30。

网络/存贮器接口NSI28还从其它结点接收引用请求,并且把它们指向将被满足的一个结点的存贮器。这样就有效地使结点存贮器30具有双重端口能力(dual-ported)。通过局部地交错存取一个结点的存贮器30并且重迭(overlapping)这个交错存取请求处理过程,可以以较低的成本得到几乎同样的效率的增长。

变址/交错存取(M/I)24执行通常的两级段/页(segment/page)变址;即:在主存贮器30中存贮的某些形式的段/页表的指导下完成把处理器22所产生的虚拟地址变换为真实地址的操作。所产生的真实地址唯一地确定了所有结点存贮器中的每个字或字节;高位二进制数确定结点号,低位二进制数确定结点存贮器中的字或字节。图3表明了这种情况。

在本实施例中,变址/交错存取M/I24还执行一种地址的交错存取转换。一个附加的字段来规定变址/交错存取24是否执行此功能,该附加的字段被加到段和/或页表中的项目上,这是本实施例所独有的。这种转换的效果使真实存贮器的一页成为完全包含在一个结点中的一个连续的地址块(见图4);或者使一页真实地址成为一个被散布在几个结点存贮器上的地址块(见图5)。

这样便可以保证一个连续的页面处于一个结点自己的存贮器30之中,对于处理器22而言,它是局部的,并且可以快速存取,提供了一个局部存贮器的功能。由于一个交错存取的页面被散布在许多存贮器块上,当多个处理器访问它时,则大大地减少了存贮器冲突的可能性,还提供了有效的全局可存取存贮器。

为了进一步减少冲突的可能性,该交错存取转换还可以“散列”(hash)地址的结点号部分,例如把地址的结点号数部分和其它地址的二进制数进行“异或”操作XOR(exclusive-OR-ing)。这样可以减少以正常方式访问存贮器时冲突的可能性。

所使用的交错存取度(一个交错存取的页面被散布其上的结点的个数)可以由附加的字段来确定,该字段是附加在段和/或页表上的。这个字段还可以确定所用的“散列法”的特点。

通过对一些页面进行连续变址,而对一些页面进行交错存取变址,部分的主存贮器30可以是局部的而部分主存贮器30是全局的。存贮器变址表控制着局部对全局的数量,在运行期间,这是可以变化的,以适应应用的要求。

图6表明了一个主存贮器应用的例子,本发明使这类的主存贮器应用成为可能。图6表明从所有的结点存贮器30的一端分配的全局存贮器和从另一端分配的局部存贮器。但是这并不是使用此处叙述的本发明的唯一方式,它只是表明本发明如何允许在连续的运行过程中去改变用来作为全局存贮器和局部存贮器的存贮器比例。

除了由全局存贮器所承担的通信功能外,本发明还支持处理器之间直接地信息传送(direct interprocessor message passing):直接主存贮器数据移动指令(例如“MVCL”IBM370操作原理)可以被用来把数据从一个处理器的一个连续页面移动到另一个处理器的一个连续页面上,而不扰乱或不需要使用任何其它的结点存贮器。

变址/交错存取M/I使用存贮器变址表。这些变址表用以确定由变址/交错存取M/I完成的在处理器发生的地址和进入存贮器的地址之间所执行的变址操作。具体地说,本实施例所独有的是:这些变址表确定了一种交错存取转换是否将被应用到一个地址上,并且可以确定在有此种交错存取转换时将应用什么样的交错存取转换。这些表可能驻存在交址/交错存取M/I自身之中;或驻存在由变址/交错存取M/I所访问的系统主存贮器中(或者是全局存贮器,或者是局部存贮器);或既驻存在变址/交错存取M/I中又存在系统的主存贮器中。无论它们驻存在什么地方,系统处理器所运行的软件都可以对其进行修改。通过扩展这种地址表的常规内容,使其包括至少一位的含有确定交错存取和/或再变址信息的一个字段,可以很方便地把这些表中的交错存取定义与某种形式的虚拟存贮器变址结合起来。这些形式可以是页面变址、段变址或两级段页变址(参考文件见计算机科学出版社出版的,贝·J著的“计算机系统结构”一书,原文为:Baer·j·,“Camputer Systems Architecture”,Computer Science Press,Rockville,MD,1980)。上述的结合在此处说明的最佳实施方案中已经被完成,但本发明并不要求这种结合,本发明仅仅要求由每个处理器来控制交错存取的存在和/或其量。做此工作的其它方法包括:扩展处理器的指令组,以得到交错存取的和非交错存取的数据存取指令;通过指令组的扩展或输入/输出指令控制,得到一些这样的指令,它们使对于数据和/或指令获取的交错开始或停止。

图7表示了在存贮器变址和低位再变址(loworder remapping)二者被结合起来的情况下变址/交错存取(M/I)的工作情况。图的顶部表示从处理器接收到且存贮在VAR242中的一个虚拟地址。如图所示,它被分为一个段和/或页索引(S/PI)244、一个页内地址(offset)PO246和一个字节地址WD248。在存贮器变址系统中,这些字段具有传统的意义。WO用来指定在编址的字中的哪一个字节(或较大的最小编址单元的字)将被访问到,该WO穿过整个变址过程而保持不变(如图所示),下面将不对其进行进一步说明。

如图所示,以传统方法使用S/PI,将其作为进入存贮器变址表的一个索引。从这个存贮器变址表中,通过表查找操作以传统方式获得实际的段/页地址(S/PO)250,以形成一个真实地址,如图所示,本实施例所独有的是:表查找还产生出一个与每个段和/或页相关联的交错存取量,该段和/或页在存贮器变址表中被确定。

在得到真实地址之后,可以应用低位再变址252在RAR254中产生一个再变址地址。低位再变址对可变量的可变宽右旋的那部分也适用(下面还要说明),也可以将其省略,在这种情况下,真实地址保持不变地传送到下个阶段。低位再变址利用真实地址的其余部分(HR字段)对一个字段LR进行操作,以产生相同宽度的一个新地址字段LR′,如图所示。LR(以及LR′)的宽度可以是两个极值之间的任何值:最大时,其宽度等于页内地址(PO);最小时,等于最大允许的交错存取量,即:如果宽度等于N,则存贮器模块的最大数为2N。图7表示了这两个极值之间中点的情况。低位再变址的目的是对将在存贮器模块的子集合上被交错存取的连续地址进行随机化处理,以不同顺序存取。这样当被存取的数据的结构的大小等于对所有存贮器的一个交错存取的扫描中存贮器量的整倍数时,便降低了许多处理器同时访问同一个存贮器模块的可能性。LR的最大宽度应能保持页面在连续编址块(Conti-guously-addressed blocks)中被寻址;最小尺寸等于有效地执行上述功能所需要的最小值。低位再变址是1对1,就是说,LR的每一个可能的值必须被变换为LR′的一个不同的值。一种可能的低位再变址如下:从右到左将LR的各个位命名为LR0、LR1……LRn;同样,HR和HR′的各个位也被类似地命名。然后,利用“xor”代表传统的异或逻辑功能,一个适用的低位再变址则为:LR0′=LR0 xor HRO;LR′=LR1 xor HR1;……LRn′=LRnxor HRn。

之后,在一个可变宽位段装置256上,由一种可变量右旋执行实际的交错存取转换,产生出用来访问系统存贮器模块的实际绝对地址。这种交错存取转换使用先前所得到的交错存取量。并且在再变址(假如有再变址)之后,对除字节地址(WO)外的真实地址进行处理。将要被循环的字段的宽度和字段中将被循环的量是由交错存取量所确定的。右旋操作如下:象上述的LR一种对HS进行编号,给定一个交错存取量Q,将被循环的字段宽度是由LSO开始到HSq-1。被循环的字段的位数等于Q。这就意味着在2a个结点中或存贮模块中对一页作交错存取。换句话说,就是把一页划分为2a个块,把每块指定给一个不同的结点。如图7所示,交错存取量是“查表272”所提供的。“查表272”可以从为VAR242中的虚拟地址所访问的存贮器变址表270中的一个表项目得到该交错存取量。该表项目可以包括一个字段,它用来指示是否需要进行交错存取变换,以及交错存取量的大小。如果该字段指出应当进行交错存取,“查表272”则把交错存取量送到可变宽位段装置256,在此,地址位HSq-1到LSO被右旋Q位。很明显,通过这种右旋操作,从LSq-1到LSO的低位Q个比特便代替了从HSq-1到HSO的高位Q个比特,于是便完成了交错存取变换。可以使用一种传统的方法对结合的Hs、Cs和Ls字段按位循环Q位,而不用可变量可变宽右旋。但是,该方案允许系统结构具有比处理结点的最大数目要少一些的处理结点,这是因为在绝对地址寄存器258中,它保持了高位(最左位)的0不变,那些高位的0出现在RAR254中再变址的地址中。传统的循环不会这样,因此,必须允许LS的所有的可能值这样一个事实便强制访问所有可能的结点。

在绝对地址中,最后的HS′字段指定处理结点,该结点的存贮器模块包含要被存取的数据(结点Node#);相结合的CS和LS′字段指示在那个将找到数据的存贮器模块中的位移地址(存贮器内地址)WO字段指示需要哪一个字节或子字。

要注意的是,当交错存取量等于0时,可变量可变宽右旋使HS′等于HS,而LS′等于LS,这使得绝对地址与再变址的地址相同,于是提供了直接的连续寻址。这提供了上述的连续寻址。存贮器变址表中适当的值使得这些连续地址可以是属于产生地址的结点的局部存贮器,或是完全被包含在其它节点中的存贮器(对于信息传送和其它操作来说,后者是很有用的)。

还要注意的是,使用小于最大可能的交错存取有效地限制一些处理器(全局存贮器被分配在这些处理器上)。这可以在几个方面得到应用,例如:(a)假如由于存贮器模块有故障,网络有故障等,能允许系统继续工作,尽管此时工作在降低性能的方式;(b)能有效地划分系统,允许一些部分有它们自己的、独立于其它部分的全局和局部存贮器分配,这便减少了这些部分之间的干扰:既能进行几个独立问题,又可运动一个适当地划分开的单个问题。

上述的发明可以与一个自用的高速缓冲存贮器26一起运行,也可以没有它。该高速缓冲存贮器26的位置可以如图2所示,或位于处理器与M/I之间。高速缓冲存贮器的功能是去减少那些在时间上或在相邻地址上反复出现的存贮器存取的访问时间。对于保持在多处理器结构中的高速缓冲存贮器的一致性而言,这种高速缓冲存贮器需要有一种附加的能力,而在单一处理器的高速缓冲存贮器上平常不具备这种能力。例如:假如一个处理器可以大致上在另一处理器在一个存贮单元上写入的同时,在同一单元读出存贮器,则要求在其自己的高速缓冲存贮器中哪一个处理器也不满足这样的存贮器基准。这种附加能力可以由各种不同的方式提供,例如:不同的高速缓冲存贮器之间的交叉讯问(cross-int-errogation),或者通过指定某些存贮器位置,使其不可进行高速缓存(non-cacheable)。本发明可以结合使用任何此种高速缓冲存贮方案(或者根本不用)。

本发明包括一个网络/存贮器接口(NSI)28,图8说明了它的操作原理。对于本发明的正常运行而言,这个单元的路径选择功能(下文还要解释)是必需的。本发明中可以使用提供这种相同的信息路径选择功能的任何硬件结构,任何技术领域中的熟练技术人员对于它的工作情况是很明确的。这种单元与每个处理结点合在一起,如图2所示。该单元的功能是在相联的处理器,相联的存贮器控制器和网络的其它处理器结点之间安排路线发送信息,所发送的信息类型包括(但不限于):

(a).本地处理器发出的装入请求。

(b).本地处理器发出的存贮请求。

(c).本地高速缓冲存贮器发生的高速缓冲存贮器流装入请求,这是本地处理器发出的存贮请求与高速缓冲存贮器失配(cache-misses)的结果。

(d).本地高速缓冲存贮器发出的高速缓冲存贮器流存贮请求,这是本地处理器发出的存贮请求与高速缓冲存贮器失配的结果。

(e).对于本地处理器和/或高速缓冲存贮器发出的存贮器装入或存贮请求的响应。

(f).其它处理器或高速缓冲器发出的存贮器装入或存贮请求,包括包含在本地处理器节点的存贮器中的存贮单元。

(g).对其它处理器或高速缓冲存贮器发出的存贮请求的响应,它们从本地处理节点的存贮器返回。

(h).从本地处理器到远程处理器的信息,或从远程处理器节点到本地处理器的信息。

(i).本地处理器发出的同步请求(诸如测试与置位test-and-set等),在本地存贮器或远程存贮器位置执行这些请求。

(j).对于同步请求的响应。

所有这些信息必须包含足以识别信息类型的数据。

另外,所有到达NSI28的这种信息必须包含这样的数据,它能足够地确定这些信息是否要被发送到本地处理器/高速缓冲存贮器26、本地存贮器30或互连网络10。在处理器或高速缓冲存贮器发出存贮请求的情况下,这种信息被包含在存贮器地址的“节点#”字段中(Node#)。如果“节点#”字段值与本地结点的数相符,则这种请求便发送到本地存贮器30;否则便发送到互连网络10。上述的存贮器变址方案使所需的交错操作的执行有所保证。同样,对存贮请求的响应或者被发送到本地处理器22,或者被发送到互连网络10,以便回到发出该信息的处理器。其它信息也必须包含“节点#”字段和信息类型识别码,它们唯一地识别这种信息,以便由NSI28正确地发送。根据包含在信息中的字段中的信息,NSI能够把信息从三个源中任一个发送到两个其它的输出端的任一个。特别地,图中所示的装置可以执行下述的发送功能:

(a).PE发送器(PERTE)282从PE22接收信息。如果“节点#”字段指示当前节点,则PERTE282通过本地存贮器集中器(LMCON)把信息送到本地存贮器30,否则,则通过网络集中器(NETCON)286把它送到网络。

(b).本地存贮器发送器(LM RTE)288从本地存贮器30接收响应信息。如果“节点#”指示当前节点,LM RTE288则通过PE集中器(PE CON)290把信息发送到本地PE22,否则,通过网络集中器(NET CON)286把它送到网络。

(c).网络发送器(NET PRE)292从网络接收信息,并且根据每个信息的类型确定它是不是:1)对本地存贮器模块访问的另一处理器所给出的请求;或2)来自另一个节点的回答,它包含有当前节点所请求的,来自其它节点本地存贮器的数据。如果是1)的情况则通过LM CON284把信息发送到本地存贮器,否则,通过PE CON290把它送到本地PE22。

(d).网络集中器286或者通过PE RTE282从PE22,或者通过LM RTE288从LM30接收信息(或者是请求,或者是回答)。根据信息的“节点#”它把两者送到网络10,从发送到另一节点。

(e).PE集中器290或者通过LM RTE288从本地存贮器30,或通过NET RTE292从网络器接收回答信息,它把这些信息送往PE22(和/或高速缓冲存贮器26)。

(f).本地存贮器集中284或者通过PE RTE282从本地PE22,或通过NET RTE292从网络10接收请求信息。它把这些信息送往本地存贮器30。

除了数据通信的通路之外,上述发送器和集中器必须与控制信息通信,这些控制信息指定什么时候数据有效(从发送器到集中器),并指定什么时候可以被接收(从集中器到发送器)。

可以使用一个两端口存贮器而不用LM RTE288和LM CON284装置。

这样参照最佳实施方案叙述了本发明,本领域熟练的技术人员能理解到,在形式上和细节上可以做出各种改变而不离开本发明的范围。

Claims (5)

1、在一个包括有产生具有实地址的存贮器引用请求的多个处理器、用来保持所说真实地址的第一寄存器装置以及由多个存贮器模块构成的一个系统存贮器的多处理器系统中。一装置的特征为:

与所说的第一寄存器装置相连的交错存取变换装置,用于将所说的实地址转变为相应的绝对地址,每一个绝对地址指定所说的一个存贮器模块以及模块中的存贮位置,所说的绝对地址即为在所说的处理器装置的控制下,对不同数量的存贮器模块进行交错存取;

用于接收所说的绝对地址的第二寄存器装置;以及

根据所说的绝对地址将所说的存贮器引用请求导向各被指定的存贮器模块及存贮单元的装置,借助于此,在所说的处理器装置的控制下,绝对地址可以动态地交错访问不同数量的所说的存贮器模块。

2、根据权利要求1的装置,进一步的特征为,通过旋转确定其高位毕特来实现所说绝对地址的交错访问。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US06/664,131 US4754394A (en) | 1984-10-24 | 1984-10-24 | Multiprocessing system having dynamically allocated local/global storage and including interleaving transformation circuit for transforming real addresses to corresponding absolute address of the storage |

| US664,131 | 1984-10-24 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN85107534A CN85107534A (zh) | 1987-04-15 |

| CN1004307B true CN1004307B (zh) | 1989-05-24 |

Family

ID=24664672

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN85107534.7A Expired CN1004307B (zh) | 1984-10-24 | 1985-10-14 | 动态分配局部/全局存贮器系统 |

Country Status (11)

| Country | Link |

|---|---|

| US (2) | US4754394A (zh) |

| EP (1) | EP0179401B1 (zh) |

| JP (1) | JPS61103258A (zh) |

| KR (1) | KR910001736B1 (zh) |

| CN (1) | CN1004307B (zh) |

| CA (1) | CA1236588A (zh) |

| DE (1) | DE3586389T2 (zh) |

| GB (1) | GB2165975B (zh) |

| HK (2) | HK23690A (zh) |

| IN (1) | IN166397B (zh) |

| PH (1) | PH25478A (zh) |

Families Citing this family (136)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4811216A (en) * | 1986-12-22 | 1989-03-07 | American Telephone And Telegraph Company | Multiprocessor memory management method |

| US5093913A (en) * | 1986-12-22 | 1992-03-03 | At&T Laboratories | Multiprocessor memory management system with the flexible features of a tightly-coupled system in a non-shared memory system |

| US5136706A (en) * | 1987-04-30 | 1992-08-04 | Texas Instruments Incorporated | Adaptive memory management system for collection of garbage in a digital computer |

| US5111389A (en) * | 1987-10-29 | 1992-05-05 | International Business Machines Corporation | Aperiodic mapping system using power-of-two stride access to interleaved devices |

| JPH063589B2 (ja) * | 1987-10-29 | 1994-01-12 | インターナシヨナル・ビジネス・マシーンズ・コーポレーシヨン | アドレス置換装置 |

| US5226039A (en) * | 1987-12-22 | 1993-07-06 | Kendall Square Research Corporation | Packet routing switch |

| US5251308A (en) * | 1987-12-22 | 1993-10-05 | Kendall Square Research Corporation | Shared memory multiprocessor with data hiding and post-store |

| US5761413A (en) * | 1987-12-22 | 1998-06-02 | Sun Microsystems, Inc. | Fault containment system for multiprocessor with shared memory |

| US5341483A (en) * | 1987-12-22 | 1994-08-23 | Kendall Square Research Corporation | Dynamic hierarchial associative memory |

| US5055999A (en) * | 1987-12-22 | 1991-10-08 | Kendall Square Research Corporation | Multiprocessor digital data processing system |

| US5276826A (en) * | 1988-01-04 | 1994-01-04 | Hewlett-Packard Company | Apparatus for transforming addresses to provide pseudo-random access to memory modules |

| JPH0291747A (ja) * | 1988-09-29 | 1990-03-30 | Hitachi Ltd | 情報処理装置 |

| JPH0833799B2 (ja) * | 1988-10-31 | 1996-03-29 | 富士通株式会社 | データ入出力制御方式 |

| US5117350A (en) * | 1988-12-15 | 1992-05-26 | Flashpoint Computer Corporation | Memory address mechanism in a distributed memory architecture |

| AU615084B2 (en) * | 1988-12-15 | 1991-09-19 | Pixar | Method and apparatus for memory routing scheme |

| FR2642252A1 (fr) * | 1989-01-26 | 1990-07-27 | Centre Nat Rech Scient | Unite d'interconnexion entre circuits, notamment du type crossbar procede de mise en oeuvre d'une unite d'interconnexion entre circuits, et utilisations d'une unite d'interconnexion entre circuits |

| IT1228728B (it) * | 1989-03-15 | 1991-07-03 | Bull Hn Information Syst | Sistema multiprocessore con replicazione di dati globali e due livelli di unita' di traduzione indirizzi. |

| EP0389151A3 (en) * | 1989-03-22 | 1992-06-03 | International Business Machines Corporation | System and method for partitioned cache memory management |

| US5072369A (en) * | 1989-04-07 | 1991-12-10 | Tektronix, Inc. | Interface between buses attached with cached modules providing address space mapped cache coherent memory access with SNOOP hit memory updates |

| US5144692A (en) * | 1989-05-17 | 1992-09-01 | International Business Machines Corporation | System for controlling access by first system to portion of main memory dedicated exclusively to second system to facilitate input/output processing via first system |

| US5301327A (en) * | 1989-06-30 | 1994-04-05 | Digital Equipment Corporation | Virtual memory management for source-code development system |

| JPH03150637A (ja) * | 1989-11-08 | 1991-06-27 | Oki Electric Ind Co Ltd | パイプライン対応のレジスタ割付け方式 |

| US5715419A (en) * | 1989-12-05 | 1998-02-03 | Texas Instruments Incorporated | Data communications system with address remapping for expanded external memory access |

| US5682202A (en) * | 1989-12-08 | 1997-10-28 | Fuji Photo Film Co., Ltd. | Apparatus for recording/reproducing video data in a memory card on a cluster basis |

| EP0460192A1 (en) * | 1989-12-26 | 1991-12-11 | Eastman Kodak Company | Image processing apparatus having disk storage resembling ram memory |

| EP0509055A4 (en) * | 1990-01-05 | 1994-07-27 | Maspar Computer Corp | Parallel processor memory system |

| US5161156A (en) * | 1990-02-02 | 1992-11-03 | International Business Machines Corporation | Multiprocessing packet switching connection system having provision for error correction and recovery |

| US5153595A (en) * | 1990-03-26 | 1992-10-06 | Geophysical Survey Systems, Inc. | Range information from signal distortions |

| JP2653709B2 (ja) * | 1990-04-20 | 1997-09-17 | 富士写真フイルム株式会社 | 画像・音声データ再生装置 |

| JPH0418638A (ja) * | 1990-05-11 | 1992-01-22 | Fujitsu Ltd | 静的メモリ割当て処理方法 |

| JPH0430231A (ja) * | 1990-05-25 | 1992-02-03 | Hitachi Ltd | 主記憶アドレッシング方式 |

| US5230051A (en) * | 1990-09-04 | 1993-07-20 | Hewlett-Packard Company | Distributed messaging system and method |

| US5265207A (en) * | 1990-10-03 | 1993-11-23 | Thinking Machines Corporation | Parallel computer system including arrangement for transferring messages from a source processor to selected ones of a plurality of destination processors and combining responses |

| JPH04246745A (ja) * | 1991-02-01 | 1992-09-02 | Canon Inc | 情報処理装置及びその方法 |

| EP0576546A4 (en) * | 1991-03-18 | 1995-01-25 | Echelon Corp | NETWORK VARIABLES. |

| EP0576574B1 (en) | 1991-03-18 | 2001-10-31 | Echelon Corporation | Programming language structures for use in a network for communicating, sensing and controlling information |

| US6493739B1 (en) | 1993-08-24 | 2002-12-10 | Echelon Corporation | Task scheduling in an event driven environment |

| US5269013A (en) * | 1991-03-20 | 1993-12-07 | Digital Equipment Corporation | Adaptive memory management method for coupled memory multiprocessor systems |

| US5341485A (en) * | 1991-05-07 | 1994-08-23 | International Business Machines Corporation | Multiple virtual address translation per computer cycle |

| US5630098A (en) * | 1991-08-30 | 1997-05-13 | Ncr Corporation | System and method for interleaving memory addresses between memory banks based on the capacity of the memory banks |

| CA2078312A1 (en) | 1991-09-20 | 1993-03-21 | Mark A. Kaufman | Digital data processor with improved paging |

| CA2078310A1 (en) * | 1991-09-20 | 1993-03-21 | Mark A. Kaufman | Digital processor with distributed memory system |

| US5263003A (en) * | 1991-11-12 | 1993-11-16 | Allen-Bradley Company, Inc. | Flash memory circuit and method of operation |

| CA2073516A1 (en) * | 1991-11-27 | 1993-05-28 | Peter Michael Kogge | Dynamic multi-mode parallel processor array architecture computer system |

| US5434992A (en) * | 1992-09-04 | 1995-07-18 | International Business Machines Corporation | Method and means for dynamically partitioning cache into a global and data type subcache hierarchy from a real time reference trace |

| US5359730A (en) * | 1992-12-04 | 1994-10-25 | International Business Machines Corporation | Method of operating a data processing system having a dynamic software update facility |

| US5845329A (en) * | 1993-01-29 | 1998-12-01 | Sanyo Electric Co., Ltd. | Parallel computer |

| US5598568A (en) * | 1993-05-06 | 1997-01-28 | Mercury Computer Systems, Inc. | Multicomputer memory access architecture |

| JPH06348584A (ja) * | 1993-06-01 | 1994-12-22 | Internatl Business Mach Corp <Ibm> | データ処理システム |

| US5584042A (en) * | 1993-06-01 | 1996-12-10 | International Business Machines Corporation | Dynamic I/O data address relocation facility |

| US5638527A (en) * | 1993-07-19 | 1997-06-10 | Dell Usa, L.P. | System and method for memory mapping |

| GB9320982D0 (en) * | 1993-10-12 | 1993-12-01 | Ibm | A data processing system |

| US5583990A (en) * | 1993-12-10 | 1996-12-10 | Cray Research, Inc. | System for allocating messages between virtual channels to avoid deadlock and to optimize the amount of message traffic on each type of virtual channel |

| US5613067A (en) * | 1993-12-30 | 1997-03-18 | International Business Machines Corporation | Method and apparatus for assuring that multiple messages in a multi-node network are assured fair access to an outgoing data stream |

| JP3687990B2 (ja) * | 1994-01-25 | 2005-08-24 | 株式会社日立製作所 | メモリアクセス機構 |

| SE515344C2 (sv) * | 1994-02-08 | 2001-07-16 | Ericsson Telefon Ab L M | Distribuerat databassystem |

| US5530837A (en) * | 1994-03-28 | 1996-06-25 | Hewlett-Packard Co. | Methods and apparatus for interleaving memory transactions into an arbitrary number of banks |

| US5537635A (en) * | 1994-04-04 | 1996-07-16 | International Business Machines Corporation | Method and system for assignment of reclaim vectors in a partitioned cache with a virtual minimum partition size |

| US5907684A (en) * | 1994-06-17 | 1999-05-25 | International Business Machines Corporation | Independent channel coupled to be shared by multiple physical processing nodes with each node characterized as having its own memory, CPU and operating system image |

| US5727184A (en) * | 1994-06-27 | 1998-03-10 | Cirrus Logic, Inc. | Method and apparatus for interfacing between peripherals of multiple formats and a single system bus |

| JP2625385B2 (ja) * | 1994-06-30 | 1997-07-02 | 日本電気株式会社 | マルチプロセッサシステム |

| US5500852A (en) * | 1994-08-31 | 1996-03-19 | Echelon Corporation | Method and apparatus for network variable aliasing |

| US5812858A (en) * | 1994-09-16 | 1998-09-22 | Cirrus Logic, Inc. | Method and apparatus for providing register and interrupt compatibility between non-identical integrated circuits |

| US5685005A (en) * | 1994-10-04 | 1997-11-04 | Analog Devices, Inc. | Digital signal processor configured for multiprocessing |

| US6182121B1 (en) * | 1995-02-03 | 2001-01-30 | Enfish, Inc. | Method and apparatus for a physical storage architecture having an improved information storage and retrieval system for a shared file environment |

| US5850522A (en) * | 1995-02-03 | 1998-12-15 | Dex Information Systems, Inc. | System for physical storage architecture providing simultaneous access to common file by storing update data in update partitions and merging desired updates into common partition |

| US5860133A (en) * | 1995-12-01 | 1999-01-12 | Digital Equipment Corporation | Method for altering memory configuration and sizing memory modules while maintaining software code stream coherence |

| US6745292B1 (en) | 1995-12-08 | 2004-06-01 | Ncr Corporation | Apparatus and method for selectively allocating cache lines in a partitioned cache shared by multiprocessors |

| US5708790A (en) * | 1995-12-12 | 1998-01-13 | International Business Machines Corporation | Virtual memory mapping method and system for address translation mapping of logical memory partitions for BAT and TLB entries in a data processing system |

| US5896543A (en) * | 1996-01-25 | 1999-04-20 | Analog Devices, Inc. | Digital signal processor architecture |

| US5954811A (en) * | 1996-01-25 | 1999-09-21 | Analog Devices, Inc. | Digital signal processor architecture |

| US5892945A (en) * | 1996-03-21 | 1999-04-06 | Oracle Corporation | Method and apparatus for distributing work granules among processes based on the location of data accessed in the work granules |

| US5784697A (en) * | 1996-03-27 | 1998-07-21 | International Business Machines Corporation | Process assignment by nodal affinity in a myultiprocessor system having non-uniform memory access storage architecture |

| US5940870A (en) * | 1996-05-21 | 1999-08-17 | Industrial Technology Research Institute | Address translation for shared-memory multiprocessor clustering |

| US6134601A (en) * | 1996-06-17 | 2000-10-17 | Networks Associates, Inc. | Computer resource management system |

| US5933852A (en) * | 1996-11-07 | 1999-08-03 | Micron Electronics, Inc. | System and method for accelerated remapping of defective memory locations |

| US6381668B1 (en) * | 1997-03-21 | 2002-04-30 | International Business Machines Corporation | Address mapping for system memory |

| US6065045A (en) * | 1997-07-03 | 2000-05-16 | Tandem Computers Incorporated | Method and apparatus for object reference processing |

| US6002882A (en) * | 1997-11-03 | 1999-12-14 | Analog Devices, Inc. | Bidirectional communication port for digital signal processor |

| US5970232A (en) * | 1997-11-17 | 1999-10-19 | Cray Research, Inc. | Router table lookup mechanism |

| US6101181A (en) * | 1997-11-17 | 2000-08-08 | Cray Research Inc. | Virtual channel assignment in large torus systems |

| US6085303A (en) * | 1997-11-17 | 2000-07-04 | Cray Research, Inc. | Seralized race-free virtual barrier network |

| US6230252B1 (en) | 1997-11-17 | 2001-05-08 | Silicon Graphics, Inc. | Hybrid hypercube/torus architecture |

| US6061779A (en) * | 1998-01-16 | 2000-05-09 | Analog Devices, Inc. | Digital signal processor having data alignment buffer for performing unaligned data accesses |

| US6085254A (en) * | 1998-04-10 | 2000-07-04 | Telefonaktiebolaget Lm Ericsson (Publ) | Dynamic size alteration of memory files |

| US6401189B1 (en) | 1998-08-05 | 2002-06-04 | Michael J. Corinthios | General base state assignment for optimal massive parallelism |

| US6216174B1 (en) | 1998-09-29 | 2001-04-10 | Silicon Graphics, Inc. | System and method for fast barrier synchronization |

| US6275900B1 (en) | 1999-01-27 | 2001-08-14 | International Business Machines Company | Hybrid NUMA/S-COMA system and method |

| US7472215B1 (en) | 1999-03-31 | 2008-12-30 | International Business Machines Corporation | Portable computer system with thermal enhancements and multiple power modes of operation |

| US6345306B1 (en) * | 1999-05-05 | 2002-02-05 | International Business Machines Corporation | Packager apparatus and method for physically and logically packaging and distributing items in a distributed environment |

| US6549931B1 (en) | 1999-09-27 | 2003-04-15 | Oracle Corporation | Distributing workload between resources used to access data |

| US6609131B1 (en) | 1999-09-27 | 2003-08-19 | Oracle International Corporation | Parallel partition-wise joins |

| US6674720B1 (en) | 1999-09-29 | 2004-01-06 | Silicon Graphics, Inc. | Age-based network arbitration system and method |

| US6751698B1 (en) | 1999-09-29 | 2004-06-15 | Silicon Graphics, Inc. | Multiprocessor node controller circuit and method |

| US6643754B1 (en) * | 2000-02-15 | 2003-11-04 | International Business Machines Corporation | System and method for dynamically allocating computer memory |

| US7260543B1 (en) | 2000-05-09 | 2007-08-21 | Sun Microsystems, Inc. | Automatic lease renewal with message gates in a distributed computing environment |

| US7111163B1 (en) | 2000-07-10 | 2006-09-19 | Alterwan, Inc. | Wide area network using internet with quality of service |

| DE10049498A1 (de) * | 2000-10-06 | 2002-04-11 | Philips Corp Intellectual Pty | Virtuelles Speichergerät für ein digitales Hausnetz |

| US7401161B2 (en) * | 2000-12-18 | 2008-07-15 | Sun Microsystems, Inc. | High performance storage array interconnection fabric using multiple independent paths |

| US7072976B2 (en) * | 2001-01-04 | 2006-07-04 | Sun Microsystems, Inc. | Scalable routing scheme for a multi-path interconnection fabric |

| US7007189B2 (en) * | 2001-05-07 | 2006-02-28 | Sun Microsystems, Inc. | Routing scheme using preferred paths in a multi-path interconnection fabric in a storage network |

| US20030037061A1 (en) * | 2001-05-08 | 2003-02-20 | Gautham Sastri | Data storage system for a multi-client network and method of managing such system |

| US6832301B2 (en) * | 2001-09-11 | 2004-12-14 | International Business Machines Corporation | Method for recovering memory |

| US6901491B2 (en) * | 2001-10-22 | 2005-05-31 | Sun Microsystems, Inc. | Method and apparatus for integration of communication links with a remote direct memory access protocol |

| US7124410B2 (en) * | 2002-01-09 | 2006-10-17 | International Business Machines Corporation | Distributed allocation of system hardware resources for multiprocessor systems |

| GB2417111B (en) * | 2002-04-22 | 2006-08-16 | Micron Technology Inc | Providing a register file memory with local addressing in a SIMD parallel processor |

| US7346690B1 (en) | 2002-05-07 | 2008-03-18 | Oracle International Corporation | Deferred piggybacked messaging mechanism for session reuse |

| US7797450B2 (en) * | 2002-10-04 | 2010-09-14 | Oracle International Corporation | Techniques for managing interaction of web services and applications |

| US7085897B2 (en) * | 2003-05-12 | 2006-08-01 | International Business Machines Corporation | Memory management for a symmetric multiprocessor computer system |

| US7379424B1 (en) | 2003-08-18 | 2008-05-27 | Cray Inc. | Systems and methods for routing packets in multiprocessor computer systems |

| US7921262B1 (en) | 2003-12-18 | 2011-04-05 | Symantec Operating Corporation | System and method for dynamic storage device expansion support in a storage virtualization environment |

| US7873776B2 (en) * | 2004-06-30 | 2011-01-18 | Oracle America, Inc. | Multiple-core processor with support for multiple virtual processors |

| US7685354B1 (en) * | 2004-06-30 | 2010-03-23 | Sun Microsystems, Inc. | Multiple-core processor with flexible mapping of processor cores to cache banks |

| KR100591371B1 (ko) * | 2005-03-23 | 2006-06-20 | 엠텍비젼 주식회사 | 공유 메모리의 분할 영역 크기 가변 방법 및 공유 메모리를가지는 휴대형 단말기 |

| US7493400B2 (en) | 2005-05-18 | 2009-02-17 | Oracle International Corporation | Creating and dissolving affinity relationships in a cluster |

| US8037169B2 (en) * | 2005-05-18 | 2011-10-11 | Oracle International Corporation | Determining affinity in a cluster |

| US7797615B2 (en) | 2005-07-07 | 2010-09-14 | Acer Incorporated | Utilizing variable-length inputs in an inter-sequence permutation turbo code system |

| US7856579B2 (en) | 2006-04-28 | 2010-12-21 | Industrial Technology Research Institute | Network for permutation or de-permutation utilized by channel coding algorithm |

| US20070011557A1 (en) | 2005-07-07 | 2007-01-11 | Highdimension Ltd. | Inter-sequence permutation turbo code system and operation methods thereof |

| US7814065B2 (en) * | 2005-08-16 | 2010-10-12 | Oracle International Corporation | Affinity-based recovery/failover in a cluster environment |

| US20160098279A1 (en) * | 2005-08-29 | 2016-04-07 | Searete Llc | Method and apparatus for segmented sequential storage |

| US9176741B2 (en) * | 2005-08-29 | 2015-11-03 | Invention Science Fund I, Llc | Method and apparatus for segmented sequential storage |

| US8468356B2 (en) | 2008-06-30 | 2013-06-18 | Intel Corporation | Software copy protection via protected execution of applications |

| US9086913B2 (en) | 2008-12-31 | 2015-07-21 | Intel Corporation | Processor extensions for execution of secure embedded containers |

| US9171044B2 (en) * | 2010-02-16 | 2015-10-27 | Oracle International Corporation | Method and system for parallelizing database requests |

| US8793429B1 (en) * | 2011-06-03 | 2014-07-29 | Western Digital Technologies, Inc. | Solid-state drive with reduced power up time |

| US9747287B1 (en) * | 2011-08-10 | 2017-08-29 | Nutanix, Inc. | Method and system for managing metadata for a virtualization environment |

| US8601473B1 (en) | 2011-08-10 | 2013-12-03 | Nutanix, Inc. | Architecture for managing I/O and storage for a virtualization environment |

| US9652265B1 (en) | 2011-08-10 | 2017-05-16 | Nutanix, Inc. | Architecture for managing I/O and storage for a virtualization environment with multiple hypervisor types |

| US9009106B1 (en) | 2011-08-10 | 2015-04-14 | Nutanix, Inc. | Method and system for implementing writable snapshots in a virtualized storage environment |

| US8549518B1 (en) | 2011-08-10 | 2013-10-01 | Nutanix, Inc. | Method and system for implementing a maintenanece service for managing I/O and storage for virtualization environment |

| US9772866B1 (en) | 2012-07-17 | 2017-09-26 | Nutanix, Inc. | Architecture for implementing a virtualization environment and appliance |

| US9268707B2 (en) | 2012-12-29 | 2016-02-23 | Intel Corporation | Low overhead paged memory runtime protection |

| US9417903B2 (en) | 2013-06-21 | 2016-08-16 | International Business Machines Corporation | Storage management for a cluster of integrated computing systems comprising integrated resource infrastructure using storage resource agents and synchronized inter-system storage priority map |

| US20170078367A1 (en) * | 2015-09-10 | 2017-03-16 | Lightfleet Corporation | Packet-flow message-distribution system |

| US20170108911A1 (en) * | 2015-10-16 | 2017-04-20 | Qualcomm Incorporated | System and method for page-by-page memory channel interleaving |

Family Cites Families (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3820079A (en) * | 1971-11-01 | 1974-06-25 | Hewlett Packard Co | Bus oriented,modular,multiprocessing computer |

| US3796996A (en) * | 1972-10-05 | 1974-03-12 | Honeywell Inf Systems | Main memory reconfiguration |

| GB1411182A (en) * | 1973-01-04 | 1975-10-22 | Standard Telephones Cables Ltd | Data processing |

| US4228496A (en) * | 1976-09-07 | 1980-10-14 | Tandem Computers Incorporated | Multiprocessor system |

| US4174514A (en) * | 1976-11-15 | 1979-11-13 | Environmental Research Institute Of Michigan | Parallel partitioned serial neighborhood processors |

| US4149242A (en) * | 1977-05-06 | 1979-04-10 | Bell Telephone Laboratories, Incorporated | Data interface apparatus for multiple sequential processors |

| US4285040A (en) * | 1977-11-04 | 1981-08-18 | Sperry Corporation | Dual mode virtual-to-real address translation mechanism |

| US4254463A (en) * | 1978-12-14 | 1981-03-03 | Rockwell International Corporation | Data processing system with address translation |

| US4280176A (en) * | 1978-12-26 | 1981-07-21 | International Business Machines Corporation | Memory configuration, address interleaving, relocation and access control system |

| US4371929A (en) * | 1980-05-05 | 1983-02-01 | Ibm Corporation | Multiprocessor system with high density memory set architecture including partitionable cache store interface to shared disk drive memory |

| US4442484A (en) * | 1980-10-14 | 1984-04-10 | Intel Corporation | Microprocessor memory management and protection mechanism |

| US4509140A (en) * | 1980-11-10 | 1985-04-02 | Wang Laboratories, Inc. | Data transmitting link |

| US4414624A (en) * | 1980-11-19 | 1983-11-08 | The United States Of America As Represented By The Secretary Of The Navy | Multiple-microcomputer processing |

| JPS57162056A (en) * | 1981-03-31 | 1982-10-05 | Toshiba Corp | Composite computer system |

| JPS58149551A (ja) * | 1982-02-27 | 1983-09-05 | Fujitsu Ltd | 記憶制御方式 |

| JPS58154059A (ja) * | 1982-03-08 | 1983-09-13 | Omron Tateisi Electronics Co | 並列処理システムのメモリアクセス方式 |

| US4648035A (en) * | 1982-12-06 | 1987-03-03 | Digital Equipment Corporation | Address conversion unit for multiprocessor system |

| US4577274A (en) * | 1983-07-11 | 1986-03-18 | At&T Bell Laboratories | Demand paging scheme for a multi-ATB shared memory processing system |

| US4591975A (en) * | 1983-07-18 | 1986-05-27 | Data General Corporation | Data processing system having dual processors |

-

1984

- 1984-10-24 US US06/664,131 patent/US4754394A/en not_active Expired - Lifetime

-

1985

- 1985-08-20 PH PH32816A patent/PH25478A/en unknown

- 1985-09-20 CA CA000491267A patent/CA1236588A/en not_active Expired

- 1985-09-24 JP JP60208985A patent/JPS61103258A/ja active Granted

- 1985-10-14 CN CN85107534.7A patent/CN1004307B/zh not_active Expired

- 1985-10-15 KR KR1019850007590A patent/KR910001736B1/ko not_active IP Right Cessation

- 1985-10-17 EP EP85113174A patent/EP0179401B1/en not_active Expired - Lifetime

- 1985-10-17 DE DE8585113174T patent/DE3586389T2/de not_active Expired - Fee Related

- 1985-10-21 GB GB08525903A patent/GB2165975B/en not_active Expired

- 1985-10-24 IN IN838/MAS/85A patent/IN166397B/en unknown

-

1988

- 1988-03-16 US US07/168,721 patent/US4980822A/en not_active Expired - Lifetime

-

1990

- 1990-03-29 HK HK236/90A patent/HK23690A/xx unknown

-

1995

- 1995-06-08 HK HK89995A patent/HK89995A/xx not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| GB2165975B (en) | 1988-07-20 |

| JPS61103258A (ja) | 1986-05-21 |

| EP0179401B1 (en) | 1992-07-22 |

| CN85107534A (zh) | 1987-04-15 |

| US4980822A (en) | 1990-12-25 |

| KR860003553A (ko) | 1986-05-26 |

| DE3586389T2 (de) | 1993-03-04 |

| DE3586389D1 (de) | 1992-08-27 |

| KR910001736B1 (ko) | 1991-03-22 |

| EP0179401A2 (en) | 1986-04-30 |

| US4754394A (en) | 1988-06-28 |

| GB8525903D0 (en) | 1985-11-27 |

| EP0179401A3 (en) | 1989-09-13 |

| PH25478A (en) | 1991-07-01 |

| IN166397B (zh) | 1990-04-28 |

| HK89995A (en) | 1995-06-16 |

| HK23690A (en) | 1990-04-06 |

| JPH0520776B2 (zh) | 1993-03-22 |

| GB2165975A (en) | 1986-04-23 |

| CA1236588A (en) | 1988-05-10 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1004307B (zh) | 动态分配局部/全局存贮器系统 | |

| US5485627A (en) | Partitionable massively parallel processing system | |

| JPH03500585A (ja) | トロイダル接続された分布記憶装置型並列計算機のための増強された入出力アーキテクチャ | |

| JPH0816536A (ja) | マルチプロセッサシステム | |

| CN1004589B (zh) | 使用地址变换的数据处理系统 | |

| US6092136A (en) | Multi-processor central processing unit | |

| ES8606696A1 (es) | Sistema de ordenador digital | |

| US5297255A (en) | Parallel computer comprised of processor elements having a local memory and an enhanced data transfer mechanism | |

| JP2001147800A (ja) | 情報処理システム、並びに、この情報処理システムを利用したソート方法、コンパイル方法およびジョイン方法 | |

| JPH0512126A (ja) | 仮想計算機のアドレス変換装置及びアドレス変換方法 | |

| JPH07120312B2 (ja) | バッファメモリ制御装置 | |

| US5710932A (en) | Parallel computer comprised of processor elements having a local memory and an enhanced data transfer mechanism | |

| Jagadish et al. | An efficient scheme for interprocessor communication using dual-ported RAMs | |

| JP3080457B2 (ja) | 分散アドレス変換方式 | |

| US5299196A (en) | Distributed address decoding for bus structures | |

| US5983323A (en) | Processor node | |

| Burkowski | A multi-user data flow architecture | |

| IE52963B1 (en) | Data processing arrangements | |

| JPS59173828A (ja) | デ−タ処理システム | |

| EP0326164A2 (en) | Parallel computer comprised of processor elements having a local memory and an enhanced data transfer mechanism | |

| Bornstein et al. | Data reshuffling in support of fast I/O for distributed-memory machines | |

| Sharif et al. | Design and simulations of a serial-link interconnection network for a massively parallel computer system | |

| CN85105547B (zh) | 用于一信息处理装置的存储器存取控制系统 | |

| JPH0696032A (ja) | 並列処理システム | |

| KR830001847B1 (ko) | 복수의 마이크로세서를 제어하는 시스템 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C06 | Publication | ||

| PB01 | Publication | ||

| C13 | Decision | ||

| GR02 | Examined patent application | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CX01 | Expiry of patent term |