CN100451914C - 锁相环迅速加电方法和装置 - Google Patents

锁相环迅速加电方法和装置 Download PDFInfo

- Publication number

- CN100451914C CN100451914C CNB028169697A CN02816969A CN100451914C CN 100451914 C CN100451914 C CN 100451914C CN B028169697 A CNB028169697 A CN B028169697A CN 02816969 A CN02816969 A CN 02816969A CN 100451914 C CN100451914 C CN 100451914C

- Authority

- CN

- China

- Prior art keywords

- frequency

- clock signal

- signal

- multiplier

- processor

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

- 238000000034 method Methods 0.000 title claims description 28

- 230000001360 synchronised effect Effects 0.000 claims description 15

- 230000033228 biological regulation Effects 0.000 claims description 5

- 238000012544 monitoring process Methods 0.000 claims description 3

- 230000000630 rising effect Effects 0.000 claims description 2

- 238000012545 processing Methods 0.000 description 9

- 238000010586 diagram Methods 0.000 description 7

- 230000006870 function Effects 0.000 description 7

- 230000008859 change Effects 0.000 description 4

- 238000012937 correction Methods 0.000 description 4

- 238000013016 damping Methods 0.000 description 4

- 230000003213 activating effect Effects 0.000 description 3

- 230000001934 delay Effects 0.000 description 3

- 230000009471 action Effects 0.000 description 2

- 230000004913 activation Effects 0.000 description 2

- 238000013461 design Methods 0.000 description 2

- 230000005059 dormancy Effects 0.000 description 2

- 230000006872 improvement Effects 0.000 description 2

- GOLXNESZZPUPJE-UHFFFAOYSA-N spiromesifen Chemical compound CC1=CC(C)=CC(C)=C1C(C(O1)=O)=C(OC(=O)CC(C)(C)C)C11CCCC1 GOLXNESZZPUPJE-UHFFFAOYSA-N 0.000 description 2

- 239000013078 crystal Substances 0.000 description 1

- 230000003111 delayed effect Effects 0.000 description 1

- 238000001514 detection method Methods 0.000 description 1

- 238000005516 engineering process Methods 0.000 description 1

- 238000001914 filtration Methods 0.000 description 1

- 230000005764 inhibitory process Effects 0.000 description 1

- 230000000266 injurious effect Effects 0.000 description 1

- 238000012423 maintenance Methods 0.000 description 1

- 230000007246 mechanism Effects 0.000 description 1

- 230000002093 peripheral effect Effects 0.000 description 1

- 230000001915 proofreading effect Effects 0.000 description 1

- 230000001105 regulatory effect Effects 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F11/00—Error detection; Error correction; Monitoring

- G06F11/36—Preventing errors by testing or debugging software

- G06F11/362—Software debugging

- G06F11/3636—Software debugging by tracing the execution of the program

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/04—Generating or distributing clock signals or signals derived directly therefrom

- G06F1/08—Clock generators with changeable or programmable clock frequency

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/3237—Power saving characterised by the action undertaken by disabling clock generation or distribution

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/324—Power saving characterised by the action undertaken by lowering clock frequency

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/3287—Power saving characterised by the action undertaken by switching off individual functional units in the computer system

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F1/00—Details not covered by groups G06F3/00 - G06F13/00 and G06F21/00

- G06F1/26—Power supply means, e.g. regulation thereof

- G06F1/32—Means for saving power

- G06F1/3203—Power management, i.e. event-based initiation of a power-saving mode

- G06F1/3234—Power saving characterised by the action undertaken

- G06F1/3296—Power saving characterised by the action undertaken by lowering the supply or operating voltage

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0806—Multiuser, multiprocessor or multiprocessing cache systems

- G06F12/0842—Multiuser, multiprocessor or multiprocessing cache systems for multiprocessing or multitasking

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/14—Handling requests for interconnection or transfer

- G06F13/20—Handling requests for interconnection or transfer for access to input/output bus

- G06F13/28—Handling requests for interconnection or transfer for access to input/output bus using burst mode transfer, e.g. direct memory access DMA, cycle steal

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F13/00—Interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F13/38—Information transfer, e.g. on bus

- G06F13/382—Information transfer, e.g. on bus using universal interface adapter

- G06F13/385—Information transfer, e.g. on bus using universal interface adapter for adaptation of a particular data processing system to different peripheral devices

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3836—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3836—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution

- G06F9/3851—Instruction issuing, e.g. dynamic instruction scheduling or out of order instruction execution from multiple instruction streams, e.g. multistreaming

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/30—Arrangements for executing machine instructions, e.g. instruction decode

- G06F9/38—Concurrent instruction execution, e.g. pipeline, look ahead

- G06F9/3867—Concurrent instruction execution, e.g. pipeline, look ahead using instruction pipelines

- G06F9/3869—Implementation aspects, e.g. pipeline latches; pipeline synchronisation and clocking

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/48—Program initiating; Program switching, e.g. by interrupt

- G06F9/4806—Task transfer initiation or dispatching

- G06F9/4843—Task transfer initiation or dispatching by program, e.g. task dispatcher, supervisor, operating system

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/0802—Details of the phase-locked loop the loop being adapted for reducing power consumption

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/16—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop

- H03L7/18—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using a frequency divider or counter in the loop

- H03L7/183—Indirect frequency synthesis, i.e. generating a desired one of a number of predetermined frequencies using a frequency- or phase-locked loop using a frequency divider or counter in the loop a time difference being used for locking the loop, the counter counting between fixed numbers or the frequency divider dividing by a fixed number

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F12/00—Accessing, addressing or allocating within memory systems or architectures

- G06F12/02—Addressing or allocation; Relocation

- G06F12/08—Addressing or allocation; Relocation in hierarchically structured memory systems, e.g. virtual memory systems

- G06F12/0802—Addressing of a memory level in which the access to the desired data or data block requires associative addressing means, e.g. caches

- G06F12/0844—Multiple simultaneous or quasi-simultaneous cache accessing

- G06F12/0855—Overlapped cache accessing, e.g. pipeline

- G06F12/0859—Overlapped cache accessing, e.g. pipeline with reload from main memory

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F2213/00—Indexing scheme relating to interconnection of, or transfer of information or other signals between, memories, input/output devices or central processing units

- G06F2213/38—Universal adapter

- G06F2213/3814—Wireless link with a computer system port

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03L—AUTOMATIC CONTROL, STARTING, SYNCHRONISATION, OR STABILISATION OF GENERATORS OF ELECTRONIC OSCILLATIONS OR PULSES

- H03L7/00—Automatic control of frequency or phase; Synchronisation

- H03L7/06—Automatic control of frequency or phase; Synchronisation using a reference signal applied to a frequency- or phase-locked loop

- H03L7/08—Details of the phase-locked loop

- H03L7/085—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal

- H03L7/095—Details of the phase-locked loop concerning mainly the frequency- or phase-detection arrangement including the filtering or amplification of its output signal using a lock detector

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04W—WIRELESS COMMUNICATION NETWORKS

- H04W88/00—Devices specially adapted for wireless communication networks, e.g. terminals, base stations or access point devices

- H04W88/02—Terminal devices

- H04W88/06—Terminal devices adapted for operation in multiple networks or having at least two operational modes, e.g. multi-mode terminals

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D10/00—Energy efficient computing, e.g. low power processors, power management or thermal management

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D30/00—Reducing energy consumption in communication networks

- Y02D30/50—Reducing energy consumption in communication networks in wire-line communication networks, e.g. low power modes or reduced link rate

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y02—TECHNOLOGIES OR APPLICATIONS FOR MITIGATION OR ADAPTATION AGAINST CLIMATE CHANGE

- Y02D—CLIMATE CHANGE MITIGATION TECHNOLOGIES IN INFORMATION AND COMMUNICATION TECHNOLOGIES [ICT], I.E. INFORMATION AND COMMUNICATION TECHNOLOGIES AIMING AT THE REDUCTION OF THEIR OWN ENERGY USE

- Y02D30/00—Reducing energy consumption in communication networks

- Y02D30/70—Reducing energy consumption in communication networks in wireless communication networks

-

- Y—GENERAL TAGGING OF NEW TECHNOLOGICAL DEVELOPMENTS; GENERAL TAGGING OF CROSS-SECTIONAL TECHNOLOGIES SPANNING OVER SEVERAL SECTIONS OF THE IPC; TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10—TECHNICAL SUBJECTS COVERED BY FORMER USPC

- Y10S—TECHNICAL SUBJECTS COVERED BY FORMER USPC CROSS-REFERENCE ART COLLECTIONS [XRACs] AND DIGESTS

- Y10S331/00—Oscillators

- Y10S331/02—Phase locked loop having lock indicating or detecting means

Abstract

提供了一种PLL倍频器,其等待时间几乎与PLL的唤醒时间相等。当PLL正在获取锁相时,通过保证时钟信号不包含高于PLL目标频率及低于预定阈值频率的频率而向处理器提供一操作时钟信号。特别地,提供分频器和频率检测器,以防止时钟信号的频率在阈值和目标频率定义的范围之外操作。

Description

相关申请

本申请要求2001年8月29日在35U.S.C.§119(e)基础上由Allen等提交的申请号为60/315,655,标题为“DIGITAL BASEBANDPROCESSOR”的临时申请的权益。以上临时申请的全部合并在本申请中以作参考。

技术领域

本发明涉及锁相环(PLL)倍频器,特别是用于通过在PLL的锁定时间间隔期间提供操作时钟信号而减少与激活PLL相关的消耗的方法和装置。

背景技术

在许多计算系统、数字设备等之中,经常将处理器需要的各种时钟信号同步到单一的基准时钟信号,然后分配到处理器适当的逻辑电路、子系统、和元件。术语“处理器”通常指任何执行逻辑运算、计算任务、和/或控制功能的设备。处理器可以包括一个或多个子系统、元件、和/或其他处理器。处理器一般包括各种逻辑和/或数字元件,它们利用时钟信号来操作,用来锁存数据、前进和/或排序逻辑状态、同步计算和逻辑操作、和/或提供其他定时功能。

例如,便携式电话包括具有多个子系统或元件的处理器,比如数字信号处理器(DSP),它以高时钟频率动作,用来执行实时、计算密集并且经常是时间严格的任务;微控制器(MCU),以较低时钟频率动作,例如执行各种控制功能、协调事件、执行系统软件等等。此外,DSP和MCU可以各自操作或者具有以多个时钟频率动作的支持元件。在任何指定时间时钟频率的需求取决于处理器的计算需求。

由模拟或数字锁相环(PLL)或延迟锁定环(DLL)实现的倍频器经常用来生成高频时钟信号,并将其锁定为与基准时钟同相。然后该高频时钟信号可以提供用来驱动逻辑电路或元件、提供给数字设备的时钟分配树、和/或另外分配给处理器来满足系统的计时需求。这样,处理器各种元件的时钟频率需求可以由单一的基准信号支持和同步到单一的基准信号。

提供时钟信号中的术语“提供”描述了信号没有被禁用、被旁路、被禁止(gated off)、或被阻止应用于所指的逻辑门、数字元件和/或电路等,或由其接收并用于操作。通常,术语时钟元件将用在这里描述任何以上提到的元件。例如,时钟信号可以提供给旁路选择、禁止逻辑、时钟分配树等等,但最终提供给一个或多个诸如逻辑门、触发器等需要如逻辑电平、定时信号、锁存器等的低电平元件。这些低电平元件或这种低电平元件的集合通常被称为时钟元件。

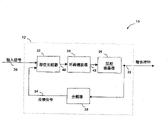

图1为从输入时钟信号生成输出时钟信号的现有的倍频器10的框图。倍频器10包括PLL 12,该PLL 12生成高频输出时钟信号32并锁定该信号与输入时钟信号30同相。

术语时钟信号或简单时钟通常是指任何模拟或数字周期性信号,尤其是用来为逻辑元件、数字电路或其他(即,时钟元件)生成至少一个定时信号或逻辑电平的周期性信号。时钟信号可以是各种波形中的任何一种,这些波形包括但不限定于正弦波、方波、脉冲串等。例如,时钟信号可以是最终用作前进处理器的状态、锁定数据、执行逻辑操作等的信号。诸如摆动(swing)正弦波的信号,和来自例如从中形成和/或导出一个或多个时钟信号的晶体振荡器的信号也可以考虑为时钟信号。

PLL 12包括相位比较器22、环路滤波器24、压控振荡器26、和分频器28。相位比较器22接收输入时钟信号30和反馈时钟信号34,并比较两信号的相位。输入时钟信号30可以例如是系统时钟,该系统时钟为处理器提供基准时钟,利用该基准时钟来同步分配给处理器的较高频率的时钟信号。反馈信号34与输出时钟信号32相关,具有与输出时钟信号32相同的相位和与输入时钟信号30相同的频率。相位比较器22提供相位误差信号40,该信号与输入时钟信号30和反馈时钟信号34之间的差异成比例。

环路滤波器24用来滤除噪声并使相位误差信号40平滑。例如,环路滤波器24可以包括低通滤波器。此外,环路滤波器24将相位误差信号转换为一信号,该信号表示用来减少相位误差信号40大小所需要的电压的变化。由环路滤波器24产生的电压校正信号42提供给VCO,用来校正输入时钟信号30和反馈信号34之间的相位差异。

压控振荡器(VCO)一般为振荡器提供电压,该振荡器产生具有与所提供电压成比例的频率的信号。这样,VCO 26接收来自环路滤波器24的电压校正信号42,并相应地调整提供给振荡器的电压。从而调整输出时钟信号32的频率,以校正由相位比较器22检测到的相位误差(即输出时钟信号32被改进为与输入时钟信号30同相)。

输出时钟信号32通过分频器28反馈到相位比较器。分频器28可以是例如n分计数器,对输出时钟信号的频率进行分频,来提供用来与输入时钟信号30进行比较的反馈时钟信号34。这样,选择分频器比率n来匹配由VCO得到的倍频器比率,从而提供反馈时钟信号,它具有与输入时钟信号相同的频率并且与输出时钟信号相同的相位。

一般伴随生成被锁相到输入时钟信号的输出时钟信号会有各种延迟。特别是锁相环收敛需要一定时间间隔(即,锁定输出时钟信号与输入时钟信号同相)。当获得相位锁定时发生的延迟经常称为锁定时间。

图2为图解利用如图1所示的倍频器产生锁相到输入时钟信号的输出时钟信号时,经常伴随其发生的延迟的时序图。座标图5表示输出时钟信号(例如,输出时钟信号32)的频率作为时间的函数。在图2中,将假定PLL在时间t0是未激活的。例如,没有输入信号提供给PLL,没有启动VCO,没有产生输出信号。

换言之,时间t0表示何时想要给倍频器提供输入时钟并给VCO加电的时间,即何时想要激活PLL。

在稳定的输入信号能够提供给PLL的相位比较器之前需要一定数量的时间。该时间是间隔的一部分,称为唤醒时间,表示为间隔60。不同的PLL或DLL实现会具有其他与唤醒时间相关的延迟。例如,在图1的PLL中,具有与启动VCO开始给振荡器提供电压相关的延迟。通常,唤醒时间是指与启用各种信号和/或PLL的元件相关的时间间隔。特别是,唤醒时间是指想要产生输出信号与信号发生器第一次输出信号之间的时间间隔。

此外,会有与PLL获得输入和输出时钟信号之间的相位锁定所需要的时间相关的延迟。这些延迟表示为时间间隔64和66,分别称作PLL锁定时间和PLL锁定定时器。时间间隔64表示获得输入和输出时钟信号之间的相位锁定所实际需要的时间。然而,经常很难精确检测出何时PLL已经被有效地锁定。更为复杂的是,实际锁定时间会变化,作为所期望的倍频器的频率增长、输入时钟信号中的噪声量等的函数。这样的话,在预计PLL的锁定时间时会有一定程度的不确定性。

为了防止检测和/或预计实际锁定时间中的不确定性,锁定定时器可以用来记录等于或超过PLL锁定时间最坏情况的时间间隔。当PLL第一次激活时,锁定定时器开始递减计数。一般,直到锁定定时器期满,才认为PLL被锁定和稳定。因此,倍频器的等待时间经常由锁定定时器中记录的延迟来约束(例如,间隔66)。术语等待一般是指从倍频器输出有效的时钟信号之前所经过的时间间隔。

有效的时钟信号是指可以提供给时钟元件用来执行预期功能的时钟信号。一般,有效的时钟信号提供可用的定时参考和/或逻辑信号,从而可以执行有用的计算和/或处理,而不会丢失数据或产生其他有害的影响。例如,有效的时钟信号可以是足以向前推进处理器、锁存数据、同步逻辑时间、和/或执行其他需要时钟信号的逻辑操作的时钟信号,操作不会超出时钟元件的容许偏差并且不会导致时钟元件操作错误。

已经提出各种方法来减少倍频器的等待时间。然而,这些方法经常集中在降低锁相环的锁定时间上,从而减少由锁定定时器需要的延迟来调节最坏情况的锁定时间。

发明内容

申请者已经发现通过减少倍频器锁定时间这种方法来获得等待时间,当系统等待倍频器获得相位锁定期间,仍然有显著的处理时间的损失和功率消耗。此外,一些处理情况会需要具有比通过减少倍频器锁定时间这种方法获得的等待时间短的倍频器。

因此,根据本发明的一个实施例包括一种用于减少激活倍频器的消耗的方法,该倍频器提供与输入时钟信号同步的第一输出时钟信号。该方法包括操作:将具有第一频率的输入时钟信号提供给倍频器,用来同步第一输出时钟信号;产生第一输出时钟信号,该第一时钟信号具有充分收敛到目标频率的第二频率,该目标频率大于第一频率,第一输出时钟信号的产生决定锁定时间间隔的开始;从第一输出时钟信号产生第二输出时钟信号,该第二输出时钟信号具有第三频率,该第三频率小于第二频率并且不超过目标频率;确定第一输出时钟信号何时与输入时钟信号同步,同步的确定结束锁定时间间隔;和在锁定时间间隔期间,将第二输出时钟信号提供给至少一个时钟元件,在锁定时间间隔之后,将第一输出时钟信号提供给至少一个时钟元件。

根据本发明的又一个实施例,包括一种用于在倍频器的锁定时间间隔期间提供操作时钟信号的方法,该倍频器适于提供与输入时钟信号同步的输出时钟信号。该方法包括操作:通过将输入时钟信号与输出时钟信号连接在反馈控制环路中,将输入时钟信号与输出时钟信号之间的相位差异基本减少至零。在减少输入时钟信号与输出时钟信号之间的相位差异的操作期间,该方法还包括:利用将输出时钟信号的频率N分频,来提供频率降低后的时钟信号;和仅在确定频率降低后的输出时钟信号具有超过规定阈值频率的频率之后,将频率降低后的输出时钟信号提供给至少一个时钟元件。

根据本发明的又一个实施例,包括比较器,用于接收具有第一频率的输入时钟信号和反馈信号,该比较器适于提供误差信号,该误差信号表示在输入时钟信号与反馈信号之间的第一特性的差异;信号发生器,连接至该比较器,用来提供具有第二频率的输出时钟信号,发生器基于误差信号调整输出时钟信号的第二特性,来降低在输入时钟信号与反馈信号之间的第一特性的差异;反馈环路,基于输出时钟信号来将反馈信号提供给比较器,反馈环路与所需第一时间间隔相关联,来将在输入时钟信号与输出时钟信号之间的第一特性的差异基本上减少至零;和用于在第一时间间隔期间基于输出时钟信号来提供操作信号的装置。

根据本发明的又一个实施例,包括一种倍频器,适于在输出时钟信号已经与输入时钟信号同步之前提供操作时钟信号,该倍频器包括:比较器,用于接收具有第一频率的输入时钟信号和反馈信号,该比较器适于提供误差信号,该误差信号表示在输入时钟信号与反馈信号之间的第一特性的差异;信号发生器,连接至比较器,用来提供具有第二频率的输出时钟信号,发生器基于误差信号调整输出时钟信号的第二特性,来降低在输入时钟信号与反馈信号之间的第一特性的差异;第一分频器,用于降低第二频率,产生提供给相位比较器的反馈时钟信号;第二分频器,通过将第二频率N分频,来提供具有第三频率的第二输出时钟信号;和检测器,适于监控第一输出时钟信号和第二输出时钟信号中的至少一个,该检测器配置为将第二输出时钟信号提供给至少一个时钟元件,该操作仅在检测器确定第三频率已经超过规定的阈值频率之后进行,该规定的阈值频率大于第一频率。

附图说明

图1为锁相环(PLL)倍频器的框图;

图2为图1的PLL倍频器中与激活和获得相位锁定相关的延迟的时序图;

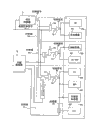

图3图解用于包括PLL倍频器的处理器的定时方案和控制;

图4图解根据本发明的实施例,降低了等待时间的PLL倍频器;

图5为图4所示的PLL倍频器中与激活和获得相位锁定相关的延迟、及PLL倍频器的减少了的等待时间的时序图;

图6图解根据本发明另一个实施例的减少了等待时间的PLL倍频器;

具体实施方式

在许多设备,尤其是由电池提供能量的设备中,比如移动电话、便携式电脑、个人数字助理(PDA)、以及其他手提式设备,功率消耗会消极影响在需要再次充电或替换电源之前这些设备的操作时间。

申请者已经发现设备的功率消耗与提供给设备处理器的电压的平方相关,并与处理器操作的频率成比例。设备的功率消耗可以表示为:

PD=cV2F(方程1)

这里:

V=供给设备的电压(即Vdd与GND之间的电压差)

F=频率(例如处理器的时钟频率)

c=一个由在电压V和频率F工作的电路所决定的常量

此外,申请者也认识到,操作处理器所需要的电压可能是提供给处理器的时钟频率的函数。

因此,一种减小设备功率消耗的方法就是将提供给处理器的频率动态调整至满足处理器的计算和/或处理需求所需的最小频率。

图3所示的系统定时方案将用来说明在典型处理器中会发生的各种处理情况。例如,处理器可能具有与图3所示的系统定时方案近似的系统定时方案。PLL多路复用器10接收作为输入的系统时钟信号80并输出高频时钟信号82。然后,高频时钟信号82提供给各种处理器元件,这些元件在三种所示的时钟域中操作:时钟域90a、时钟域90b、和时钟域90c。

时钟域90a,例如将时钟信号84提供给数字信号处理器(DSP)100a和专用DSP协处理器100b。时钟信号84的频率(即,提供给时钟域90a中元件的时钟的频率)由多路复用器70a和与门72a决定。多路复用器70a选择高频时钟信号82或者系统时钟信号80分配给在时钟域90a中操作的各种时钟元件。与门72a或者提供由多路复用器70a选择的时钟信号,或者禁止时钟信号,从而禁止用来将时钟信号84分配给DSP和协处理器的时钟元件的时钟树(未图示)。

相似的,时钟域90b将时钟信号86提供给,例如,由DSP子系统用来交换数据、传送控制信号等的专用总线(DSP总线100c),和诸如高速缓存或暂时存储器这样的专用存储器(DSP SRAM 100D)。多路复用器70b选择高频时钟信号或者系统时钟,与门或者允许或者禁止由多路复用器提供的时钟信号。此外,当高频时钟被选择时,分频器74b允许高频时钟信号82降低频率(例如,降低2倍)。

时钟域90c将时钟信号88提供给处理器100的各种其他典型的子系统和元件。尤其是在域90c中操作的微控制器(MCU)100e、系统存储器100f、外围设备总线100g、和外部总线100h。分频器74c允许高频时钟信号82在提供给多路复用器74c,用来象上述时钟域90a和90b那样选择或旁路之前,通过因数2、4、6、8、10、12、14降低频率。

处理器100可以具有许多工作状态,其中一个或多个元件处于空闲状态,和/或一个或多个时钟域不需要操作。例如,考虑包括处理器100的便携式电话。当便携式电话电源开通,但没工作(即,待机状态)的时候,便携式电话与其当前位于的小区的基站保持连接。基站周期性地(例如,每2秒钟)向所有小区电话广播关于是否已经接收到呼叫和电话是否应该转变为呼叫操作状态的小区信息。已知广播寻呼信道,便携式电话必须监控寻呼信道,以确定是否已经接收到呼叫。

然而,为了从寻呼信道获得信息需要很少的处理功率。如此这样,在寻呼信道获得期间,处理器仅需要系统时钟运行。相反,一旦信息进入便携式电话(例如,存储到存储缓冲器),为了确定是否有呼叫,需要DSP来处理该信息。然而,这种工作状态中大部分时间不需要DSP。

如此这样,当处理器的计算性需求不需要PLL时,期望将其禁止,例如,当DSP在空闲状态时。通过DSP进入空闲状态,可以禁用高频时钟信号(即,倍频器可以休眠或者禁用)。然而,当再次需要DSP的处理功率时,例如,用来处理从寻呼信道接收的信息时,为了提供处理器上增长的需求所需的必要的时钟频率,必须激活PLL。

然而,会有与激活倍频器相关的消耗,它与PLL的等待时间有关。尤其是,在PLL的锁定时间间隔期间,消耗功率但没有做计算性的工作。伴随激活倍频器带来的有效处理时间的损失,使得在某些情况下,优选地需要倍频器保持激活,而不管额外的功率消耗。

术语激活倍频器用于说明增加倍频器输出时钟信号的频率所涉及的操作。将倍频器从休眠或禁用状态启用和增加PLL的倍频器比率都认为是激活倍频器。伴随激活PLL的消耗可以认为具有时间成分和功率成分。

申请者已经认识到在输出时钟信号被认为是有效的之前,没有必要获得输入时钟信号与输出时钟信号之间的相位锁定。尤其是,申请者已经确定,输出时钟足以达到规定的最小频率并不超出规定的最大频率,从而使输出时钟被认为是操作时钟。最小和最大频率由将输出时钟信号提供给的时钟元件的特性来决定。

例如,如果输出时钟信号是用于驱动处理器的时钟,则该时钟信号需要达到能够向前推进处理器而不会导致时序破坏的最小频率。此外,输出时钟信号需要保持在处理器支持的最大频率之下,以保证正确操作。

在根据本发明的一个实施例中,通过在倍频器的锁定时间间隔期间提供操作时钟信号来减少激活倍频器的消耗。尤其是,倍频器的等待时间减少为与倍频器的唤醒时间基本相等。如此这样,在锁定时间期间可以完成计算性的工作,并且增加了激活倍频器期间的有效的处理时间。

下面更详细的阐述与根据本发明的方法与装置相关的概念和它们的实施例。应该理解以上讨论的本发明的各种方面以及以下的概要,可以用多种形式实现,本发明不限定于任何特定的实现方式。特定实现的例子仅用于说明的目的。

例如,下面阐述的PLL倍频器将用于说明本发明的各种方面。然而,倍频器的领域包括多种变形和实现,此处无法都涉及。应该理解本发明不限定于任何特定的倍频器实现,如此这样,任何具有一定时间间隔,用来将输出时钟信号与输入时钟信号同步的倍频器都认为在本发明的范围之内。

术语“倍频器”应用于提供与输入时钟信号同步的输出时钟信号的任何元件,该输出时钟信号具有大于输入时钟信号的频率。通常,倍频器包括信号发生器,用来产生具有期望频率的信号;用来将所产生的信号与输入时钟信号进行比较的方法;根据该比较用来将所产生的信号与输入时钟信号同步的方法。

当该比较是基于相位的,术语锁相环(PLL)将用于说明这样的倍频器。

可以通过各种方式实现相位比较,比如边沿跟踪(即,比较时钟信号的上升和/或轨迹边沿)、信号过零、信号导数中的零等等。此外,可以通过各种方法中的任何一种来获得相位锁定,比如,根据相位比较来改变输出时钟信号的频率、根据相位误差来延迟输出时钟信号等等。

图4表示根据本发明的倍频器的一个实施例。倍频器10‘包括锁相环12’。该锁相环的操作方式与图1所表示的PLL 12相似。特别地,PLL 12’包括相位比较器22’,提供相位误差信号40’,该信号表示输入时钟信号30’与反馈时钟信号34’之间的相位差异。环路滤波器24’接收相位误差信号40’并提供电压校正信号42’。VCO 26’接收校正信号42’并调整提供给振荡器的电压,来提供趋向减少相位误差信号40’幅度的输出时钟信号。分频器28’对输出时钟信号进行分频,提供反馈时钟信号34’,该信号具有与输入时钟信号30’基本相同的频率,和与输出时钟信号32’基本相同的相位。

此外,倍频器12’包括频率检测器50和分频器52。由VCO 26’产生的输出时钟信号32’被提供给检测器50和分频器52。检测器50和分频器52确保提供给处理器的时钟信号中不包含可能导致处理器操作错误或者导致数据丢失的频率,即,检测器50和分频器52提供操作时钟信号36。

在唤醒间隔(例如,图2中的间隔60)之后和锁定输出时钟信号与输入时钟信号同相之前,输出时钟信号容易频率超出接收时钟信号的时钟元件所预期的频率。例如,输出时钟信号会经历目标频率之上的频率,该目标频率是指由倍频器达到的预期频率。尤其是,目标频率是PLL已经锁定后由VCO产生的信号的频率。

此外,就在VCO启动之后(即,唤醒时间间隔结束的时候),输出时钟信号会经历低于接收时钟信号的时钟元件所需要的阈值频率的频率。如此这样,为了提供操作时钟信号,应该抑制由阈值频率和目标频率所定义的频率范围之外的频率。

图5表示PLL的激活间隔的频率与时间的特性曲线图,该PLL不是临界阻尼的。当考虑PLL的等待时间,PLL经常不是临界阻尼的,即,PLL不是阻尼的以防止目标频率的超调。典型的,阻尼PLL将具有延长的锁定时间,并且不适合许多考虑PLL激活消耗的应用。

PLL的输出时钟信号的目标频率(即,由倍频器得到的频率)由频率轴上的虚线表示为频率110。例如,目标频率可以是如图3说明的提供给DSP的高频时钟。

在启动VCO之后(即,在时间tw),输出时钟信号几乎瞬时达到频率100,由时间tw处的垂直线示意性表示。如图所示,在锁定时间间隔期间,输出时钟信号的频率跳跃,并且PLL趋向超调目标频率。如此这样,输出时钟信号将经历一直到频率120的频率。然后时钟信号在目标频率附近振荡,直到收敛到目标频率作为PLL锁定。

那些超过目标频率110的频率,如果提供给例如处理器,可能引起处理器操作错误。这可能导致破坏或丢失数据、错误定时或同步、或者可能对处理器的操作产生其他坏影响。如此这样,如果认为锁定时间间隔期间提供给处理器的时钟信号是操作性的,则应该抑制超过目标频率的那些频率。

为了阻止目标频率之上的频率应用到处理器的时钟元件,在图3说明的实施例中,输出时钟信号32’提供给分频器52。分频器52将输出时钟信号N分频,以确保不会由于超过时钟元件处理器操作所需最大频率的频率,而使时钟元件易丢失数据或者错误操作。

分频器52可以是例如二分计数器。然而本发明不限定于任何特定的分频器比率。设计考虑和PLL的特征会引导对每个特定实现的N的选择。

然而,N的选择应该阻止提供给处理器的时钟信号经历那些可能导致处理器操作错误的频率,即,应给提供操作时钟信号。

此外,接收时钟信号的时钟元件会具有使它能够操作的最小频率。例如,处理器的定时会依赖提供高于最小频率的时钟信号。为了确保当时钟信号第一次提供给时钟元件或元件时是操作性的,频率检测器50用来监控输出时钟信号。

仅仅当输出时钟信号超过阈值频率时,才允许将分频器的输出作为操作时钟信号36而提供。阈值频率取决于接收时钟信号的时钟元件的类型和需求。

图4表示由频率检测器控制的开关72,用来在锁定时间间隔期间,当已经超过了阈值频率后提供操作时钟信号36。然而,任何一种方法都可以用来当已经确定信号为操作性的之后,将时钟信号提供给时钟元件和元件。典型的,在PLL已经锁定之后,分频器52被旁路(例如,通过关闭开关72和打开开关70,或者通过某些相当的机构),并且将输出时钟信号作为操作时钟信号提供给处理器的各种时钟元件。

如此这样,在PLL锁定时间间隔之间,倍频器10‘将操作时钟信号提供给处理器。然后在PLL锁定时间间隔之间,可以进行计算性的工作、逻辑操作、定时、和其他各种处理任务。倍频器的等待时间几乎等于PLL的唤醒时间,如此这样,减少了激活PLL的消耗。

此外,伴随激活PLL的时间消耗会适应处理环境,其中依赖于锁定时间的等待时间已经阻止倍频器被禁用。这样,提供给处理器的时钟频率能够动态调整,以符合处理器的计算性的需求,而不必在不需要计算等级时还保持高能量状态。

应该理解以上实施例中说明的元件的排列、数量、和类型仅是示范性的。对于本领域的技术人员而言,可以在设计上做许多变形。然而,这些变形不应该背离本发明的范围。

例如,提供用来抑制目标频率之上的频率的分频器(例如,分频器52)不需要是附加的和/或单独的分频器。例如,PLL的控制环路中的全部或部分分频器(例如,分频器28‘)可以用来实现对超调频率的抑制。

图6中,分频器28“被图解为一列串联连接的二分计数器。在第一个二分计数器之后分流出时钟信号,并提供作为操作时钟信号36’,即分频器52‘是分频器28“的第一个分频级。如此这样,分频器52‘提供频率减少因数2来抑制超过倍频器目标频率的那些频率。然而,取决于期望的频率减少,可以从分频器28“的任何级引出信号。此外,分频器28“不需要包括二分计数器,而可以是具有任何适当分频比率的任何适当的分频元件。

此外,用来确定何时已经超过阈值频率的频率检测器(例如,频率检测器50)可以检测时钟信号的频率,而不是检测如图7所示直接由VCO提供的信号的频率。例如,频率检测器可以监控已经提供到分频器或者从分频器分流出的信号的频率,该分频器用于抑制超过目标频率的频率(例如,分频器52、52‘)。

此外,频率检测器可以编程为检测何时时钟信号已经超过可变的阈值频率。例如,参照图3表示的处理器100,在给定时间从任何一个时钟域中选择的最大的分频因数可以决定阈值频率应该是什么,以确保将具有符合或超过时钟元件的最小频率需求的频率的时钟信号,提供给每个接收时钟信号的元件。作为例子,当时钟域90c选择了通过14因数分频,则需要增加阈值频率,当选择更小因数或没有减少因数时,则降低阈值频率。

在一些实施例中,不需要用于检测何时已经超过阈值频率的频率检测器。例如,信号发生器(例如,VCO)的特征和接收由倍频器输出的时钟信号的时钟元件的需求可能是这样的,即当启动信号发生器后由它提供的初始输出时钟信号已经在阈值频率之上。在这种情况下,可以用简单地检测信号发生器何时第一次开始输出信号,而不管频率的逻辑来替换频率检测器(例如,频率检测器50)。由于已知信号发生器立即达到超出阈值频率的频率,所以信号发生器一启动,输出时钟信号就是操作性的。

为了得到仅具有特定范围中的频率的输出时钟信号,对于本领域的技术人员而言,对于元件的数量、类型、和配置可以做许多其他的变更、变形、和替换。这些变形应该认为是在本发明的范围之内。

已经详细阐述了本发明的许多实施例,对于本领域的技术人员而言,将很容易对其做出各种变更和改进。这些变更和改进规定为在本发明的范围之内。

因此,以上的说明仅作为例子,并不限定。本发明仅由权利要求以及等价部分来限定。

Claims (33)

1.在提供与输入时钟信号同步的第一输出时钟信号的倍频器中,一种用于减少激活倍频器的消耗的方法,该方法包括操作:

将具有第一频率的输入时钟信号提供给该倍频器;

产生该第一输出时钟信号,其具有充分收敛到目标频率的第二频率,该目标频率大于该第一频率;

检测当该第二频率已经超过最小频率并且在该第二频率到达该目标频率之前的时间,该时间确定第一间隔的开始;

从该第一输出时钟信号产生第二输出时钟信号,该第二输出时钟信号具有第三频率,该第三频率小于该第二频率并且不超过该目标频率,该第三频率基本上收敛到该目标频率的一个因数;

确定该第一输出时钟信号何时与该输入时钟信号同步,该同步的确定结束该第一间隔;和

在该第一间隔期间,提供该第二输出时钟信号来操作至少一个时钟元件,并且在该第一间隔之后,将该第一输出时钟信号提供给该至少一个时钟元件。

2.如权利要求1的方法,其中产生该第二输出时钟信号的操作包括N分该第二频率的操作,其中N决定该目标频率的因数。

3.如权利要求2的方法,其中N分该第二频率的操作包括将该第二频率至少二分。

4.一种倍频器,包括:

比较器,用于接收具有第一频率的输入时钟信号和反馈信号,该比较器提供误差信号,该误差信号表示在该输入时钟信号与该反馈信号之间的第一特性的差异;

信号发生器,连接至该比较器,用来提供具有第二频率的输出时钟信号,该信号发生器基于该误差信号调整该输出时钟信号的第二特性,来降低在该输入时钟信号与该反馈信号之间的该第一特性的差异;

具有分频器的反馈环路,基于该输出时钟信号来将该反馈信号提供给比较器,该反馈环路与第一时间间隔相关联,用来减少该第一特性的差异,从而该输入时钟信号的第一特性与该反馈信号的第一特性基本相同;和

用于在该第一时间间隔期间基于该输出时钟信号来提供操作信号的装置,该装置包括至少一部分分频器,该分频器连接至该输出时钟信号,以将该第二频率降低到低于该输出时钟信号的目标频率。

5.如权利要求4的倍频器,其中用于提供操作信号的装置包括检测器,该检测器用来确定该第二频率何时已经超过大于该第一频率的阈值频率,从而在该第二频率已经超过该阈值频率之后且在该第二频率已经到达由该分频器确定的目标频率的因数之前,提供该操作信号。

6.如权利要求5的倍频器,其中依赖该第一频率与该目标频率之间的增长来确定该阈值频率。

7.如权利要求4的倍频器,其中该第一特性是相位。

8.如权利要求7的倍频器,其中该比较器确定该输入时钟信号与该反馈信号的至少一个上升沿和下降沿之间的差异。

9.如权利要求7的倍频器,其中该比较器确定该输入时钟信号与该反馈信号的过零点之间的差异。

10.如权利要求7的倍频器,其中该第二特性是频率。

11.如权利要求7的倍频器,其中该第二特性是该输出时钟信号的延迟。

12.如权利要求4的倍频器与至少一个处理器结合。

13.如权利要求12的结合,其中该输入时钟信号是该处理器系统时钟信号。

14.如权利要求12的结合,其中该输出时钟信号分配到该至少一个处理器的时钟元件。

15.如权利要求12的结合,其中该至少一个处理器包括多个子系统,多个子系统能够以多个频率操作。

16.如权利要求15的结合,其中倍频器将时钟信号提供给该至少一个处理器的多个子系统。

17.在适于提供与输入时钟信号以目标频率同步的输出时钟信号的倍频器中,一种用于在倍频器的锁定时间间隔期间提供操作时钟信号的方法,该方法包括操作:

减少反馈控制环路中该输入时钟信号与该输出时钟信号之间的相位差异,该反馈控制环路比较该输入时钟信号与该输出时钟信号之间的相位差异,并且调整该输出时钟信号来减少该相位差异,

在减少该输入时钟信号与该输出时钟信号之间的相位差异的操作期间:

将该输出时钟信号的频率N分频,来提供频率降低后的该输出时钟信号;和

将频率降低后的该输出时钟信号提供给至少一个时钟元件,该操作在确定频率降低后的该输出时钟信号具有超过规定阈值频率的频率之后,并且频率降低后的该输出时钟信号具有已经达到N频分的该目标频率之前开始。

18.如权利要求17的方法,其中调整该输出时钟信号的频率来减少该输入时钟信号与反馈信号之间的相位差异。

19.如权利要求17的方法,其中调整该输出时钟信号的延迟来减少该输入时钟信号与反馈信号之间的相位差异。

20.如权利要求17的方法,其中确定频率降低后的该输出时钟信号具有超过规定该阈值频率的频率的操作包括:检测频率降低后的该输出时钟信号的频率,并将该频率与规定的该阈值频率比较。

21.如权利要求17的方法,还包括从压控振荡器产生该输出时钟信号,压控振荡器调整该输出时钟信号的频率来减少相位差异。

22.如权利要求21的方法,其中确定频率降低后的该输出时钟信号具有超过规定该阈值频率的频率的操作包括:检测该压控振荡器何时第一次产生该输出时钟信号。

23.一种倍频器,适于在输出时钟信号已经与输入时钟信号同步之前提供操作时钟信号,该倍频器包括:

比较器,用于接收具有第一频率的该输入时钟信号和反馈信号,该比较器适于提供误差信号,该误差信号表示在该输入时钟信号与该反馈信号之间的第一特性的差异;

信号发生器,连接至该比较器,来提供第一输出时钟信号,该第一输出时钟信号具有基本收敛于目标频率的第二频率,该信号发生器基于该误差信号调整该第一输出时钟信号的第二特性,来降低在该第一输入时钟信号与该反馈信号之间的第一特性的差异;

分频器,连接至该信号发生器,具有至少第一部分,该第一部分配置为将该第二频率N分频,以提供具有第三频率的第二输出时钟信号;

检测器,适于监控该第一输出时钟信号和该第二输出时钟信号中的至少一个,该检测器配置为将该第二输出时钟信号提供给至少一个时钟元件,该操作在该检测器确定该第二频率已经超过大于该第一频率的规定的阈值频率之后且该第二频率已经达到该目标频率之前开始。

24.如权利要求23的倍频器,其中该分频器具有至少第二部分,该第二部分配置为降低该第二频率来产生提供给该比较器的该反馈时钟信号。

25.如权利要求24的倍频器,其中该分频器包括多个级,每个级具有第一分频器因数,并且该分频器的第一部分包括多个级中的至少一个。

26.如权利要求25的倍频器,其中该第一分频器因数等于2。

27.如权利要求23的倍频器,其中该检测器监控该第一输出时钟信号,来检测该信号发生器何时第一次产生该第一输出时钟信号,以确定该第三频率何时超过规定的该阈值频率。

28.如权利要求23的倍频器与至少一个处理器结合。

29.如权利要求28的结合,其中该输入时钟信号是该至少一个处理器系统时钟信号。

30.如权利要求28的结合,其中该第一和第二输出时钟信号分配到该至少一个处理器的时钟元件。

31.如权利要求28的结合,其中该至少一个处理器包括多个子系统,多个子系统能够以多个频率操作。

32.如权利要求31的结合,其中该倍频器将该输出时钟信号提供给该至少一个处理器的多个子系统。

33.如权利要求1的方法,其中该倍频器将该第一输出时钟信号提供给至少一个处理器,并且提供该第二输出时钟信号的操作包括在该第一间隔期间将该第二输出时钟信号提供给该至少一个处理器。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US31565501P | 2001-08-29 | 2001-08-29 | |

| US60/315,655 | 2001-08-29 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1549960A CN1549960A (zh) | 2004-11-24 |

| CN100451914C true CN100451914C (zh) | 2009-01-14 |

Family

ID=23225453

Family Applications (9)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028169263A Expired - Lifetime CN100570577C (zh) | 2001-08-29 | 2002-08-29 | 高速程序跟踪 |

| CNB028169689A Expired - Lifetime CN100471079C (zh) | 2001-08-29 | 2002-08-29 | 用于无线系统中的时钟及电源控制的方法和设备 |

| CNB02816928XA Expired - Lifetime CN100399472C (zh) | 2001-08-29 | 2002-08-29 | 用于使用快速突发模式以改善处理器性能的方法和装置 |

| CN2009102091339A Expired - Lifetime CN101673238B (zh) | 2001-08-29 | 2002-08-29 | 程序跟踪器以及程序跟踪方法 |

| CNB028169271A Expired - Lifetime CN100361109C (zh) | 2001-08-29 | 2002-08-29 | 通用串行端口体系结构和系统 |

| CN02816976XA Expired - Lifetime CN1549961B (zh) | 2001-08-29 | 2002-08-29 | 动态电压控制方法与设备 |

| CNB028169697A Expired - Lifetime CN100451914C (zh) | 2001-08-29 | 2002-08-29 | 锁相环迅速加电方法和装置 |

| CNB028169700A Expired - Lifetime CN100517215C (zh) | 2001-08-29 | 2002-08-29 | 用于无线系统中定时及事件处理的方法和装置 |

| CNB028167791A Expired - Lifetime CN1299201C (zh) | 2001-08-29 | 2002-08-29 | 通过响应高速缓存缺失而切换任务来提高基于高速缓存的嵌入式处理器的处理能力的方法和装置 |

Family Applications Before (6)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028169263A Expired - Lifetime CN100570577C (zh) | 2001-08-29 | 2002-08-29 | 高速程序跟踪 |

| CNB028169689A Expired - Lifetime CN100471079C (zh) | 2001-08-29 | 2002-08-29 | 用于无线系统中的时钟及电源控制的方法和设备 |

| CNB02816928XA Expired - Lifetime CN100399472C (zh) | 2001-08-29 | 2002-08-29 | 用于使用快速突发模式以改善处理器性能的方法和装置 |

| CN2009102091339A Expired - Lifetime CN101673238B (zh) | 2001-08-29 | 2002-08-29 | 程序跟踪器以及程序跟踪方法 |

| CNB028169271A Expired - Lifetime CN100361109C (zh) | 2001-08-29 | 2002-08-29 | 通用串行端口体系结构和系统 |

| CN02816976XA Expired - Lifetime CN1549961B (zh) | 2001-08-29 | 2002-08-29 | 动态电压控制方法与设备 |

Family Applications After (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028169700A Expired - Lifetime CN100517215C (zh) | 2001-08-29 | 2002-08-29 | 用于无线系统中定时及事件处理的方法和装置 |

| CNB028167791A Expired - Lifetime CN1299201C (zh) | 2001-08-29 | 2002-08-29 | 通过响应高速缓存缺失而切换任务来提高基于高速缓存的嵌入式处理器的处理能力的方法和装置 |

Country Status (7)

| Country | Link |

|---|---|

| US (10) | US7159134B2 (zh) |

| EP (9) | EP1421588B1 (zh) |

| JP (10) | JP2005502114A (zh) |

| CN (9) | CN100570577C (zh) |

| AU (2) | AU2002331774A1 (zh) |

| DE (6) | DE60211921T2 (zh) |

| WO (8) | WO2003021409A2 (zh) |

Families Citing this family (328)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| EP1421588B1 (en) * | 2001-08-29 | 2012-01-18 | MediaTek Inc. | Method and apparatus utilizing flash burst mode to improve processor performance |

| GB0123421D0 (en) * | 2001-09-28 | 2001-11-21 | Memquest Ltd | Power management system |

| US7502817B2 (en) * | 2001-10-26 | 2009-03-10 | Qualcomm Incorporated | Method and apparatus for partitioning memory in a telecommunication device |

| US6944780B1 (en) * | 2002-01-19 | 2005-09-13 | National Semiconductor Corporation | Adaptive voltage scaling clock generator for use in a digital processing component and method of operating the same |

| EP1351117A1 (en) * | 2002-04-03 | 2003-10-08 | Hewlett-Packard Company | Data processing system and method |

| US7180322B1 (en) | 2002-04-16 | 2007-02-20 | Transmeta Corporation | Closed loop feedback control of integrated circuits |

| US7941675B2 (en) * | 2002-12-31 | 2011-05-10 | Burr James B | Adaptive power control |

| US7133972B2 (en) | 2002-06-07 | 2006-11-07 | Micron Technology, Inc. | Memory hub with internal cache and/or memory access prediction |

| US7117316B2 (en) | 2002-08-05 | 2006-10-03 | Micron Technology, Inc. | Memory hub and access method having internal row caching |

| US7149874B2 (en) * | 2002-08-16 | 2006-12-12 | Micron Technology, Inc. | Memory hub bypass circuit and method |

| US7836252B2 (en) | 2002-08-29 | 2010-11-16 | Micron Technology, Inc. | System and method for optimizing interconnections of memory devices in a multichip module |

| US7395447B2 (en) * | 2002-09-16 | 2008-07-01 | Silicon Labs Cp, Inc. | Precision oscillator for an asynchronous transmission system |

| US7774627B2 (en) * | 2002-10-03 | 2010-08-10 | Via Technologies, Inc. | Microprocessor capable of dynamically increasing its performance in response to varying operating temperature |

| US7698583B2 (en) * | 2002-10-03 | 2010-04-13 | Via Technologies, Inc. | Microprocessor capable of dynamically reducing its power consumption in response to varying operating temperature |

| US7290156B2 (en) * | 2003-12-17 | 2007-10-30 | Via Technologies, Inc. | Frequency-voltage mechanism for microprocessor power management |

| US7770042B2 (en) * | 2002-10-03 | 2010-08-03 | Via Technologies, Inc. | Microprocessor with improved performance during P-state transitions |

| US7814350B2 (en) * | 2002-10-03 | 2010-10-12 | Via Technologies, Inc. | Microprocessor with improved thermal monitoring and protection mechanism |

| US7882369B1 (en) | 2002-11-14 | 2011-02-01 | Nvidia Corporation | Processor performance adjustment system and method |

| US7886164B1 (en) | 2002-11-14 | 2011-02-08 | Nvidia Corporation | Processor temperature adjustment system and method |

| US7849332B1 (en) * | 2002-11-14 | 2010-12-07 | Nvidia Corporation | Processor voltage adjustment system and method |

| US7080268B2 (en) * | 2002-12-03 | 2006-07-18 | Intel Corporation | Method and apparatus for regulating power to electronic circuits |

| US7065663B2 (en) * | 2002-12-19 | 2006-06-20 | Intel Corporation | Methods and apparatus to control power state transitions |

| US7146822B2 (en) | 2002-12-30 | 2006-12-12 | Intel Corporation | Centrifugal liquid pump with perimeter magnetic drive |

| US7444524B2 (en) | 2002-12-30 | 2008-10-28 | Intel Corporation | Dynamic voltage transitions |

| US7228242B2 (en) | 2002-12-31 | 2007-06-05 | Transmeta Corporation | Adaptive power control based on pre package characterization of integrated circuits |

| US7811231B2 (en) | 2002-12-31 | 2010-10-12 | Abbott Diabetes Care Inc. | Continuous glucose monitoring system and methods of use |

| US8771183B2 (en) | 2004-02-17 | 2014-07-08 | Abbott Diabetes Care Inc. | Method and system for providing data communication in continuous glucose monitoring and management system |

| US7953990B2 (en) * | 2002-12-31 | 2011-05-31 | Stewart Thomas E | Adaptive power control based on post package characterization of integrated circuits |

| CN1759368A (zh) * | 2003-01-23 | 2006-04-12 | 罗切斯特大学 | 多时钟域微处理器 |

| US7206959B1 (en) * | 2003-01-24 | 2007-04-17 | National Semiconductor Corporation | Closed-loop, supply-adjusted ROM memory circuit |

| US7069461B1 (en) * | 2003-01-24 | 2006-06-27 | National Semiconductor Corporation | Closed-loop, supply-adjusted RAM memory circuit |

| US7587287B2 (en) | 2003-04-04 | 2009-09-08 | Abbott Diabetes Care Inc. | Method and system for transferring analyte test data |

| EP1467582B1 (en) * | 2003-04-11 | 2008-03-05 | Telefonaktiebolaget LM Ericsson (publ) | Method for synchronization in a mobile radio terminal |

| CN100416573C (zh) * | 2003-05-07 | 2008-09-03 | 睦塞德技术公司 | 利用电源岛管理集成电路上的功率 |

| JP4033066B2 (ja) | 2003-05-07 | 2008-01-16 | ソニー株式会社 | 周波数制御装置、情報処理装置、周波数制御方法及びプログラム |

| JP2004348662A (ja) * | 2003-05-26 | 2004-12-09 | Toshiba Corp | 電子機器、電源制御装置および電源制御方法 |

| US7375553B1 (en) * | 2003-05-28 | 2008-05-20 | Actel Corporation | Clock tree network in a field programmable gate array |

| US8066639B2 (en) | 2003-06-10 | 2011-11-29 | Abbott Diabetes Care Inc. | Glucose measuring device for use in personal area network |

| US7245145B2 (en) | 2003-06-11 | 2007-07-17 | Micron Technology, Inc. | Memory module and method having improved signal routing topology |

| US6822481B1 (en) * | 2003-06-12 | 2004-11-23 | Agilent Technologies, Inc. | Method and apparatus for clock gating clock trees to reduce power dissipation |

| US7120727B2 (en) | 2003-06-19 | 2006-10-10 | Micron Technology, Inc. | Reconfigurable memory module and method |

| US7260685B2 (en) | 2003-06-20 | 2007-08-21 | Micron Technology, Inc. | Memory hub and access method having internal prefetch buffers |

| US7836222B2 (en) * | 2003-06-26 | 2010-11-16 | International Business Machines Corporation | System and method for tracking messages between a processing unit and an external device |

| KR100540483B1 (ko) * | 2003-06-30 | 2006-01-11 | 주식회사 하이닉스반도체 | 데이터 억세스 위치에 관계없이 연속적인 버스트 모드로 데이터를 억세스할 수 있는 반도체 메모리 장치 및 그의 구동방법 |

| US7389364B2 (en) | 2003-07-22 | 2008-06-17 | Micron Technology, Inc. | Apparatus and method for direct memory access in a hub-based memory system |

| US7210059B2 (en) * | 2003-08-19 | 2007-04-24 | Micron Technology, Inc. | System and method for on-board diagnostics of memory modules |

| US7133991B2 (en) * | 2003-08-20 | 2006-11-07 | Micron Technology, Inc. | Method and system for capturing and bypassing memory transactions in a hub-based memory system |

| US7196562B1 (en) * | 2003-08-26 | 2007-03-27 | Integrated Device Technology, Inc. | Programmable clock drivers that support CRC error checking of configuration data during program restore operations |

| US7136958B2 (en) | 2003-08-28 | 2006-11-14 | Micron Technology, Inc. | Multiple processor system and method including multiple memory hub modules |

| US7287245B2 (en) * | 2003-09-17 | 2007-10-23 | Faraday Technology Corp. | Method for real-time instruction information tracing |

| US7194593B2 (en) | 2003-09-18 | 2007-03-20 | Micron Technology, Inc. | Memory hub with integrated non-volatile memory |

| US7225303B2 (en) * | 2003-09-22 | 2007-05-29 | Micron Technology, Inc. | Method and apparatus for accessing a dynamic memory device by providing at least one of burst and latency information over at least one of redundant row and column address lines |

| JP4837247B2 (ja) * | 2003-09-24 | 2011-12-14 | パナソニック株式会社 | プロセッサ |

| US7085943B2 (en) * | 2003-09-26 | 2006-08-01 | Freescale Semiconductor, Inc. | Method and circuitry for controlling supply voltage in a data processing system |

| US20050081075A1 (en) * | 2003-10-14 | 2005-04-14 | Andrej Kocev | Computer system, carrier medium and method for adjusting an expiration period |

| US7120743B2 (en) | 2003-10-20 | 2006-10-10 | Micron Technology, Inc. | Arbitration system and method for memory responses in a hub-based memory system |

| TWI254882B (en) * | 2003-11-07 | 2006-05-11 | Via Tech Inc | Rate multiplication method and rate multiplier |

| GB2408357A (en) * | 2003-11-18 | 2005-05-25 | Motorola Inc | Regulating a voltage supply to a semiconductor device |

| US7631307B2 (en) | 2003-12-05 | 2009-12-08 | Intel Corporation | User-programmable low-overhead multithreading |

| US7692477B1 (en) | 2003-12-23 | 2010-04-06 | Tien-Min Chen | Precise control component for a substrate potential regulation circuit |

| US7129771B1 (en) | 2003-12-23 | 2006-10-31 | Transmeta Corporation | Servo loop for well bias voltage source |

| US7649402B1 (en) | 2003-12-23 | 2010-01-19 | Tien-Min Chen | Feedback-controlled body-bias voltage source |

| US7012461B1 (en) | 2003-12-23 | 2006-03-14 | Transmeta Corporation | Stabilization component for a substrate potential regulation circuit |

| KR101136036B1 (ko) * | 2003-12-24 | 2012-04-18 | 삼성전자주식회사 | 유휴 모드에서의 전력 소모가 감소된 프로세서 시스템 및그 방법 |

| US7330992B2 (en) | 2003-12-29 | 2008-02-12 | Micron Technology, Inc. | System and method for read synchronization of memory modules |

| US7188219B2 (en) | 2004-01-30 | 2007-03-06 | Micron Technology, Inc. | Buffer control system and method for a memory system having outstanding read and write request buffers |

| US7788451B2 (en) | 2004-02-05 | 2010-08-31 | Micron Technology, Inc. | Apparatus and method for data bypass for a bi-directional data bus in a hub-based memory sub-system |

| US7412574B2 (en) * | 2004-02-05 | 2008-08-12 | Micron Technology, Inc. | System and method for arbitration of memory responses in a hub-based memory system |

| CN100361040C (zh) * | 2004-02-24 | 2008-01-09 | 中国科学院计算技术研究所 | 一种soc架构下的处理器核动态变频装置和方法 |

| US7479753B1 (en) | 2004-02-24 | 2009-01-20 | Nvidia Corporation | Fan speed controller |

| US7240170B2 (en) * | 2004-02-25 | 2007-07-03 | Analog Devices, Inc. | High/low priority memory |

| US7366864B2 (en) | 2004-03-08 | 2008-04-29 | Micron Technology, Inc. | Memory hub architecture having programmable lane widths |

| US7313707B2 (en) * | 2004-03-09 | 2007-12-25 | Hewlett-Packard Development Company, L.P. | Systems and methods for configuring ports |

| US7613911B2 (en) * | 2004-03-12 | 2009-11-03 | Arm Limited | Prefetching exception vectors by early lookup exception vectors within a cache memory |

| FI20040418A (fi) * | 2004-03-18 | 2005-09-19 | Nokia Corp | Digitaalijärjestelmän kellokontrolli |

| US7769950B2 (en) * | 2004-03-24 | 2010-08-03 | Qualcomm Incorporated | Cached memory system and cache controller for embedded digital signal processor |

| US7257683B2 (en) | 2004-03-24 | 2007-08-14 | Micron Technology, Inc. | Memory arbitration system and method having an arbitration packet protocol |

| US7120723B2 (en) | 2004-03-25 | 2006-10-10 | Micron Technology, Inc. | System and method for memory hub-based expansion bus |

| US6980042B2 (en) | 2004-04-05 | 2005-12-27 | Micron Technology, Inc. | Delay line synchronizer apparatus and method |

| US7590797B2 (en) | 2004-04-08 | 2009-09-15 | Micron Technology, Inc. | System and method for optimizing interconnections of components in a multichip memory module |

| US7363419B2 (en) | 2004-05-28 | 2008-04-22 | Micron Technology, Inc. | Method and system for terminating write commands in a hub-based memory system |

| US7310748B2 (en) | 2004-06-04 | 2007-12-18 | Micron Technology, Inc. | Memory hub tester interface and method for use thereof |

| US7519788B2 (en) | 2004-06-04 | 2009-04-14 | Micron Technology, Inc. | System and method for an asynchronous data buffer having buffer write and read pointers |

| US7971191B2 (en) * | 2004-06-10 | 2011-06-28 | Hewlett-Packard Development Company, L.P. | System and method for analyzing a process |

| US7042260B2 (en) * | 2004-06-14 | 2006-05-09 | Micron Technology, Inc. | Low power and low timing jitter phase-lock loop and method |

| CN101006397A (zh) * | 2004-06-15 | 2007-07-25 | 皇家飞利浦电子股份有限公司 | 用于性能参数的二进制控制的控制方案 |

| EP1607835A1 (en) * | 2004-06-15 | 2005-12-21 | Koninklijke Philips Electronics N.V. | Closed-loop control for performance tuning |

| US7562233B1 (en) | 2004-06-22 | 2009-07-14 | Transmeta Corporation | Adaptive control of operating and body bias voltages |

| US7401241B2 (en) * | 2004-06-22 | 2008-07-15 | Intel Corporation | Controlling standby power of low power devices |

| US7774625B1 (en) * | 2004-06-22 | 2010-08-10 | Eric Chien-Li Sheng | Adaptive voltage control by accessing information stored within and specific to a microprocessor |

| KR100598011B1 (ko) * | 2004-06-29 | 2006-07-06 | 삼성전자주식회사 | 클럭 사용 회로 및 클럭 신호 발생 방법 |

| US20050008095A1 (en) * | 2004-07-23 | 2005-01-13 | Rush Frederick A. | Apparatus using interrupts for controlling a processor for radio isolation and associated methods |

| US8472990B2 (en) * | 2004-07-23 | 2013-06-25 | St Ericsson Sa | Apparatus using interrupts for controlling a processor for radio isolation and associated method |

| US7312487B2 (en) * | 2004-08-16 | 2007-12-25 | International Business Machines Corporation | Three dimensional integrated circuit |

| US7681065B2 (en) * | 2004-08-16 | 2010-03-16 | Broadcom Corporation | Method and system for a message processor switch for performing incremental redundancy in edge compliant terminals |

| US7308590B2 (en) | 2004-10-15 | 2007-12-11 | Intel Corporation | Automatic dynamic processor operating voltage control |

| US7434073B2 (en) * | 2004-11-29 | 2008-10-07 | Intel Corporation | Frequency and voltage scaling architecture |

| US7456829B2 (en) * | 2004-12-03 | 2008-11-25 | Hewlett-Packard Development Company, L.P. | Methods and systems to control electronic display brightness |

| CN1319274C (zh) * | 2004-12-10 | 2007-05-30 | 展讯通信(上海)有限公司 | 射频接收系统锁定时间及锁定后频率误差的评估方法 |

| US7379718B2 (en) | 2004-12-20 | 2008-05-27 | Marvell World Trade Ltd. | Method and apparatus to manage power consumption of a semiconductor device |

| US7337335B2 (en) * | 2004-12-21 | 2008-02-26 | Packet Digital | Method and apparatus for on-demand power management |

| US7228446B2 (en) * | 2004-12-21 | 2007-06-05 | Packet Digital | Method and apparatus for on-demand power management |

| FR2882449A1 (fr) * | 2005-01-21 | 2006-08-25 | Meiosys Soc Par Actions Simpli | Procede non intrusif de rejeu d'evenements internes au sein d'un processus applicatif, et systeme mettant en oeuvre ce procede |

| FR2881246B1 (fr) * | 2005-01-21 | 2007-03-23 | Meiosys Soc Par Actions Simpli | Procede perdictif de gestion, de journalisation ou de rejeu d'operations non deterministes au sein du deroulement d'un processus applicatif |

| US7409520B2 (en) * | 2005-01-25 | 2008-08-05 | International Business Machines Corporation | Systems and methods for time division multiplex multithreading |

| JP2006236241A (ja) * | 2005-02-28 | 2006-09-07 | Toshiba Corp | 周辺装置 |

| US20060215567A1 (en) * | 2005-03-25 | 2006-09-28 | Arun Raghunath | Method and apparatus for monitoring path statistics |

| US7529911B1 (en) * | 2005-05-26 | 2009-05-05 | Sun Microsystems, Inc. | Hardware-based technique for improving the effectiveness of prefetching during scout mode |

| CN1881798B (zh) * | 2005-06-16 | 2011-08-31 | 旺玖科技股份有限公司 | 有理数倍频电路与产生有理数倍频的方法 |

| US8745627B2 (en) * | 2005-06-27 | 2014-06-03 | Qualcomm Incorporated | System and method of controlling power in a multi-threaded processor |

| US20070008011A1 (en) * | 2005-06-29 | 2007-01-11 | Paulette Thurston | Distributed power and clock management in a computerized system |

| CN101223490A (zh) * | 2005-07-14 | 2008-07-16 | Nxp股份有限公司 | 使用历史负载简档来动态调整手持多媒体设备处理器内核的工作频率及可用功率 |

| US7953960B2 (en) * | 2005-10-18 | 2011-05-31 | International Business Machines Corporation | Method and apparatus for delaying a load miss flush until issuing the dependent instruction |

| CN101297255B (zh) * | 2005-10-26 | 2011-11-02 | 英特尔公司 | 可检测变化的集群体系结构 |

| US7766829B2 (en) * | 2005-11-04 | 2010-08-03 | Abbott Diabetes Care Inc. | Method and system for providing basal profile modification in analyte monitoring and management systems |

| US8253748B1 (en) | 2005-11-29 | 2012-08-28 | Nvidia Corporation | Shader performance registers |

| US7809928B1 (en) * | 2005-11-29 | 2010-10-05 | Nvidia Corporation | Generating event signals for performance register control using non-operative instructions |

| TW200805047A (en) * | 2005-12-23 | 2008-01-16 | Koninkl Philips Electronics Nv | Performance analysis based system level power management |

| CN100346306C (zh) * | 2006-01-06 | 2007-10-31 | 浙江大学 | 基于动态调频技术的节能编译方法 |

| US7499724B2 (en) * | 2006-01-30 | 2009-03-03 | Harris Corporation | Event sequencer used for controlling the sequence and timing of events in software defined radio |

| JP2007233718A (ja) * | 2006-03-01 | 2007-09-13 | Canon Inc | 制御装置及び半導体集積回路 |

| US20070214374A1 (en) * | 2006-03-13 | 2007-09-13 | Mark Hempstead | Ultra low power system for sensor network applications |

| US8226891B2 (en) | 2006-03-31 | 2012-07-24 | Abbott Diabetes Care Inc. | Analyte monitoring devices and methods therefor |

| US7620438B2 (en) | 2006-03-31 | 2009-11-17 | Abbott Diabetes Care Inc. | Method and system for powering an electronic device |

| US7617409B2 (en) * | 2006-05-01 | 2009-11-10 | Arm Limited | System for checking clock-signal correspondence |

| US7502913B2 (en) | 2006-06-16 | 2009-03-10 | Microsoft Corporation | Switch prefetch in a multicore computer chip |

| DE502006006706D1 (de) * | 2006-06-20 | 2010-05-27 | Siemens Ag | Verfahren zur Überwachung eines zyklischen Steuerungsprogramms |

| US7814339B2 (en) * | 2006-06-30 | 2010-10-12 | Intel Corporation | Leakage power estimation |

| US7672393B2 (en) * | 2006-08-02 | 2010-03-02 | Richtek Technology Corporation | Single-wire asynchronous serial interface |

| EP1895426A1 (en) * | 2006-08-25 | 2008-03-05 | Ali Corporation | Transmitter and transmitting system utilizing the same |

| JP4808108B2 (ja) | 2006-08-29 | 2011-11-02 | パナソニック株式会社 | プロセッサシステム |

| US8200807B2 (en) * | 2006-08-31 | 2012-06-12 | The Mathworks, Inc. | Non-blocking local events in a state-diagramming environment |

| US7958291B2 (en) * | 2006-10-10 | 2011-06-07 | Atmel Rousset S.A.S. | Supplemental communication interface |

| US7840825B2 (en) * | 2006-10-24 | 2010-11-23 | International Business Machines Corporation | Method for autonomous dynamic voltage and frequency scaling of microprocessors |

| EP1919103B8 (en) * | 2006-11-02 | 2016-11-30 | Google Technology Holdings LLC | Method and apparatus for automatic frequency correction in a multimode device |

| WO2008056293A2 (en) * | 2006-11-08 | 2008-05-15 | Nxp B.V. | Fast adaptive voltage scaling |

| TWI335531B (en) * | 2006-12-13 | 2011-01-01 | Inst Information Industry | Apparatus, method, application program, and computer readable medium thereof for generating and utilizing a feature code to monitor a program |

| US7840849B2 (en) * | 2006-12-21 | 2010-11-23 | Novell, Inc. | Methods and apparatus for debugging software including divisions of an execution history of a debuggee program |

| US7917784B2 (en) * | 2007-01-07 | 2011-03-29 | Apple Inc. | Methods and systems for power management in a data processing system |

| US8667198B2 (en) * | 2007-01-07 | 2014-03-04 | Apple Inc. | Methods and systems for time keeping in a data processing system |

| US7949801B2 (en) * | 2007-01-31 | 2011-05-24 | Pitney Bowes Inc. | Main processor initiating command timing signal via DMA to coprocessor in order to synchronize execution of instructions |

| US20080199894A1 (en) | 2007-02-15 | 2008-08-21 | Abbott Diabetes Care, Inc. | Device and method for automatic data acquisition and/or detection |

| US8123686B2 (en) | 2007-03-01 | 2012-02-28 | Abbott Diabetes Care Inc. | Method and apparatus for providing rolling data in communication systems |

| US7937076B2 (en) * | 2007-03-07 | 2011-05-03 | Harris Corporation | Software defined radio for loading waveform components at runtime in a software communications architecture (SCA) framework |

| JP4950716B2 (ja) * | 2007-03-22 | 2012-06-13 | 株式会社日立ハイテクノロジーズ | 画像処理システム、及び走査型電子顕微鏡装置 |

| US7900069B2 (en) * | 2007-03-29 | 2011-03-01 | Intel Corporation | Dynamic power reduction |

| US7743279B2 (en) | 2007-04-06 | 2010-06-22 | Apple Inc. | Program counter (PC) trace |

| US7917799B2 (en) * | 2007-04-12 | 2011-03-29 | International Business Machines Corporation | Method and system for digital frequency clocking in processor cores |

| US8161314B2 (en) * | 2007-04-12 | 2012-04-17 | International Business Machines Corporation | Method and system for analog frequency clocking in processor cores |

| DE102007019543A1 (de) | 2007-04-25 | 2008-10-30 | Rohde & Schwarz Gmbh & Co. Kg | Messgerät mit serieller digitaler Schnittstelle |

| US9134782B2 (en) | 2007-05-07 | 2015-09-15 | Nvidia Corporation | Maintaining optimum voltage supply to match performance of an integrated circuit |

| US8456301B2 (en) | 2007-05-08 | 2013-06-04 | Abbott Diabetes Care Inc. | Analyte monitoring system and methods |

| US7928850B2 (en) | 2007-05-08 | 2011-04-19 | Abbott Diabetes Care Inc. | Analyte monitoring system and methods |

| US8461985B2 (en) | 2007-05-08 | 2013-06-11 | Abbott Diabetes Care Inc. | Analyte monitoring system and methods |

| US8665091B2 (en) | 2007-05-08 | 2014-03-04 | Abbott Diabetes Care Inc. | Method and device for determining elapsed sensor life |

| US20080281171A1 (en) * | 2007-05-08 | 2008-11-13 | Abbott Diabetes Care, Inc. | Analyte monitoring system and methods |

| US7845568B2 (en) * | 2007-05-09 | 2010-12-07 | Atmel Rousset S.A.S. | Managing power and timing in a smart card device |

| JP5209046B2 (ja) * | 2007-05-23 | 2013-06-12 | アギア システムズ インコーポレーテッド | 単一及び複数の無線技術通信システムにおいて移動体デバイスの時間節約型セル検索のためのシステム及び方法 |

| US8645740B2 (en) * | 2007-06-08 | 2014-02-04 | Apple Inc. | Methods and systems to dynamically manage performance states in a data processing system |

| US9313067B2 (en) * | 2007-08-14 | 2016-04-12 | Qualcomm Incorporated | Multi-bandwidth communication system using a shared baseband processor |

| US7711864B2 (en) | 2007-08-31 | 2010-05-04 | Apple Inc. | Methods and systems to dynamically manage performance states in a data processing system |

| US7921312B1 (en) | 2007-09-14 | 2011-04-05 | National Semiconductor Corporation | System and method for providing adaptive voltage scaling with multiple clock domains inside a single voltage domain |

| TWI402647B (zh) * | 2007-09-14 | 2013-07-21 | Asustek Comp Inc | 可動態調整電壓及有效節能之電壓控制裝置、方法及電腦裝置 |

| GB2453174B (en) * | 2007-09-28 | 2011-12-07 | Advanced Risc Mach Ltd | Techniques for generating a trace stream for a data processing apparatus |

| US7945804B2 (en) * | 2007-10-17 | 2011-05-17 | International Business Machines Corporation | Methods and systems for digitally controlled multi-frequency clocking of multi-core processors |

| US9354890B1 (en) | 2007-10-23 | 2016-05-31 | Marvell International Ltd. | Call stack structure for enabling execution of code outside of a subroutine and between call stack frames |

| US20090108817A1 (en) * | 2007-10-30 | 2009-04-30 | Topower Computer Industrial Co., Ltd. | Method for actuation by boosting power source voltage |

| CN101436167B (zh) * | 2007-11-16 | 2011-03-23 | 宏达国际电子股份有限公司 | 解译串行传输信号的方法 |

| US8578193B2 (en) * | 2007-11-28 | 2013-11-05 | International Business Machines Corporation | Apparatus, method and program product for adaptive real-time power and perfomance optimization of multi-core processors |

| KR20090059602A (ko) * | 2007-12-07 | 2009-06-11 | 한국전자통신연구원 | 세션 메모리 버스를 구비한 암호화 장치 |

| GB0724337D0 (en) * | 2007-12-13 | 2008-01-23 | Icera Inc | Radio access technology |

| US8589706B2 (en) | 2007-12-26 | 2013-11-19 | Intel Corporation | Data inversion based approaches for reducing memory power consumption |

| US20090182802A1 (en) * | 2008-01-10 | 2009-07-16 | Microsoft Corporation | Mobile device management scheduling |

| US8166145B2 (en) * | 2008-01-10 | 2012-04-24 | Microsoft Corporation | Managing event-based conditional recurrent schedules |

| US8230436B2 (en) * | 2008-01-10 | 2012-07-24 | Microsoft Corporation | Aggregating recurrent schedules to optimize resource consumption |

| US7841436B2 (en) | 2008-01-21 | 2010-11-30 | Amigo Mobility International | Personal mobility vehicle |

| US8370663B2 (en) | 2008-02-11 | 2013-02-05 | Nvidia Corporation | Power management with dynamic frequency adjustments |

| US8595538B2 (en) * | 2008-03-03 | 2013-11-26 | Quintic Holdings | Single-clock-based multiple-clock frequency generator |

| US8312299B2 (en) | 2008-03-28 | 2012-11-13 | Packet Digital | Method and apparatus for dynamic power management control using serial bus management protocols |

| EP2472727B1 (en) * | 2008-03-31 | 2013-07-24 | Telefonaktiebolaget L M Ericsson (publ) | Digital baseband circuit |

| US7826382B2 (en) | 2008-05-30 | 2010-11-02 | Abbott Diabetes Care Inc. | Close proximity communication device and methods |

| US8112475B2 (en) * | 2008-06-27 | 2012-02-07 | Microsoft Corporation | Managing data delivery based on device state |

| US8090826B2 (en) * | 2008-06-27 | 2012-01-03 | Microsoft Corporation | Scheduling data delivery to manage device resources |

| US8904083B2 (en) * | 2008-07-30 | 2014-12-02 | Infineon Technologies Ag | Method and apparatus for storing data in solid state memory |

| JP2010072897A (ja) * | 2008-09-18 | 2010-04-02 | Nec Electronics Corp | クロック供給装置 |

| US8122270B2 (en) * | 2008-09-29 | 2012-02-21 | Intel Corporation | Voltage stabilization for clock signal frequency locking |

| US8127160B2 (en) | 2008-10-13 | 2012-02-28 | International Business Machines Corporation | Dynamic frequency and voltage scaling for a computer processor |

| JP2010097277A (ja) * | 2008-10-14 | 2010-04-30 | Toshiba Corp | 情報処理装置 |

| US20100094572A1 (en) * | 2008-10-15 | 2010-04-15 | International Business Machines Corporation | Dynamic Frequency And Voltage Scaling For A Computer Processor |

| JP5509579B2 (ja) * | 2008-11-21 | 2014-06-04 | セイコーエプソン株式会社 | 映像出力装置および映像出力方法ならびにプロジェクタ |

| JP5330409B2 (ja) | 2008-11-28 | 2013-10-30 | パナソニック株式会社 | メモリ制御装置、データプロセッサ及びデータ読み出し方法 |

| TWI363498B (en) * | 2008-12-03 | 2012-05-01 | Ind Tech Res Inst | A tri-mode delay type phase lock loop |

| JP5816407B2 (ja) * | 2009-02-27 | 2015-11-18 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置 |

| US8285917B2 (en) * | 2009-03-26 | 2012-10-09 | Scaleo Chip | Apparatus for enhancing flash memory access |

| US9226701B2 (en) | 2009-04-28 | 2016-01-05 | Abbott Diabetes Care Inc. | Error detection in critical repeating data in a wireless sensor system |

| EP2424426B1 (en) * | 2009-04-29 | 2020-01-08 | Abbott Diabetes Care, Inc. | Method and system for providing data communication in continuous glucose monitoring and management system |

| US9184490B2 (en) | 2009-05-29 | 2015-11-10 | Abbott Diabetes Care Inc. | Medical device antenna systems having external antenna configurations |

| US9314195B2 (en) | 2009-08-31 | 2016-04-19 | Abbott Diabetes Care Inc. | Analyte signal processing device and methods |

| WO2011026148A1 (en) | 2009-08-31 | 2011-03-03 | Abbott Diabetes Care Inc. | Analyte monitoring system and methods for managing power and noise |

| EP2290542B1 (en) * | 2009-09-01 | 2013-03-27 | Research In Motion Limited | System and method for sequencing radio items for a multi downlink multi carrier receiver |

| US8213974B2 (en) * | 2009-09-01 | 2012-07-03 | Research In Motion Limited | System and method for sequencing radio items for a multi downlink multi carrier receiver |

| JP2011118469A (ja) | 2009-11-30 | 2011-06-16 | Toshiba Corp | メモリ管理装置およびメモリ管理方法 |

| JP2011139370A (ja) * | 2009-12-28 | 2011-07-14 | Canon Inc | 電子機器とその制御方法 |

| US9256265B2 (en) | 2009-12-30 | 2016-02-09 | Nvidia Corporation | Method and system for artificially and dynamically limiting the framerate of a graphics processing unit |

| US9830889B2 (en) | 2009-12-31 | 2017-11-28 | Nvidia Corporation | Methods and system for artifically and dynamically limiting the display resolution of an application |

| US9582443B1 (en) * | 2010-02-12 | 2017-02-28 | Marvell International Ltd. | Serial control channel processor for executing time-based instructions |

| US9000804B2 (en) | 2010-03-03 | 2015-04-07 | Freescale Semiconductor, Inc. | Integrated circuit device comprising clock gating circuitry, electronic device and method for dynamically configuring clock gating |

| US8423802B2 (en) * | 2010-04-07 | 2013-04-16 | Andes Technology Corporation | Power scaling module and power scaling unit of an electronic system having a function unit in a standby state which is insensitive to change in frequency or voltage during synchronization |

| US8839006B2 (en) | 2010-05-28 | 2014-09-16 | Nvidia Corporation | Power consumption reduction systems and methods |

| US8766666B2 (en) | 2010-06-10 | 2014-07-01 | Micron Technology, Inc. | Programmable device, hierarchical parallel machines, and methods for providing state information |

| CN101860353B (zh) * | 2010-06-17 | 2012-02-29 | 广州市广晟微电子有限公司 | 数模混合芯片中的时钟电路控制装置及方法 |

| US8667308B2 (en) | 2010-06-18 | 2014-03-04 | Apple Inc. | Dynamic voltage dithering |

| WO2012004863A1 (ja) * | 2010-07-07 | 2012-01-12 | ルネサスエレクトロニクス株式会社 | データ処理装置およびデータ処理システム |

| US20120017035A1 (en) * | 2010-07-16 | 2012-01-19 | Plx Technology, Inc. | Runtime reprogramming of a processor code space memory area |

| US9996102B2 (en) | 2010-07-20 | 2018-06-12 | Nxp Usa, Inc. | Clock circuit and method for providing an electronic device with an adjustable clock signal |

| JP2012033001A (ja) | 2010-07-30 | 2012-02-16 | Toshiba Corp | 情報処理装置および情報処理方法 |

| US20120042212A1 (en) * | 2010-08-10 | 2012-02-16 | Gilbert Laurenti | Mixed Mode Processor Tracing |

| JP5598161B2 (ja) * | 2010-08-26 | 2014-10-01 | ヤマハ株式会社 | クロック発生回路 |

| US8732495B2 (en) | 2010-08-31 | 2014-05-20 | Integrated Device Technology, Inc. | Systems, apparatuses and methods for dynamic voltage and frequency control of components used in a computer system |

| WO2012030329A1 (en) * | 2010-08-31 | 2012-03-08 | Integrated Device Technology, Inc. | Systems, apparatuses and methods for dynamic voltage and frequency control of components used in a computer system |

| US20120072632A1 (en) * | 2010-09-17 | 2012-03-22 | Paul Kimelman | Deterministic and non-Deterministic Execution in One Processor |

| JP5581960B2 (ja) * | 2010-10-14 | 2014-09-03 | 凸版印刷株式会社 | 半導体装置 |

| CN102457270B (zh) * | 2010-10-29 | 2013-09-04 | 扬智科技股份有限公司 | 低增益压控振荡器的控制方法 |

| GB2499151B (en) * | 2010-11-09 | 2016-04-20 | Ibm | Energy capture of time-varying energy sources by varying computation workload |

| CN103404031B (zh) * | 2010-12-01 | 2016-01-20 | 爱立信(中国)通信有限公司 | 锁相环控制电压确定 |

| DE102011122074A1 (de) | 2010-12-20 | 2012-06-21 | Dmos Gmbh | Bussystem zur Kommunikation und Stromversorgung von Teilnehmerschaltungen und Verfahren zur Reduzierung des Energieverbrauchs in Baugruppen von Bussystemen |

| CN102082506B (zh) * | 2010-12-22 | 2012-12-12 | 复旦大学 | 适用于开关电源转换器的时钟频率选择电路 |

| CN102611148A (zh) * | 2011-01-24 | 2012-07-25 | 祥硕科技股份有限公司 | 配置充电端口的方法与控制器 |

| TW201232239A (en) * | 2011-01-24 | 2012-08-01 | Asmedia Technology Inc | Method and controller allocating charging ports |

| JP5284401B2 (ja) | 2011-03-24 | 2013-09-11 | 株式会社東芝 | 動作切替装置およびプログラム |

| US8856571B2 (en) | 2011-04-05 | 2014-10-07 | Apple Inc. | Adjusting device performance over multiple time domains |

| US8572421B2 (en) | 2011-04-05 | 2013-10-29 | Apple Inc. | Adjusting device performance based on processing profiles |

| US9588881B2 (en) | 2011-05-16 | 2017-03-07 | Cypress Semiconductor Corporation | Stack processor using a ferroelectric random access memory (F-RAM) for code space and a portion of the stack memory space having an instruction set optimized to minimize processor stack accesses |

| US9910823B2 (en) | 2011-05-16 | 2018-03-06 | Cypress Semiconductor Corporation | Stack processor using a ferroelectric random access memory (F-RAM) having an instruction set optimized to minimize memory fetch |

| US8934279B2 (en) * | 2011-05-16 | 2015-01-13 | Cypress Semiconductor Corporation | Stack processor using a ferroelectric random access memory (F-RAM) for code space and a portion of the stack memory space |

| US9135082B1 (en) * | 2011-05-20 | 2015-09-15 | Google Inc. | Techniques and systems for data race detection |

| CN102170499B (zh) * | 2011-05-24 | 2013-10-02 | 惠州Tcl移动通信有限公司 | 一种移动终端及其电源控制系统 |

| US8884920B1 (en) | 2011-05-25 | 2014-11-11 | Marvell International Ltd. | Programmatic sensing of capacitive sensors |

| US8855969B2 (en) | 2011-06-27 | 2014-10-07 | International Business Machines Corporation | Frequency guard band validation of processors |

| US9098694B1 (en) | 2011-07-06 | 2015-08-04 | Marvell International Ltd. | Clone-resistant logic |

| US9081517B2 (en) * | 2011-08-31 | 2015-07-14 | Apple Inc. | Hardware-based automatic clock gating |

| US9069553B2 (en) | 2011-09-06 | 2015-06-30 | Marvell World Trade Ltd. | Switching tasks between heterogeneous cores |

| GB2495959A (en) * | 2011-10-26 | 2013-05-01 | Imagination Tech Ltd | Multi-threaded memory access processor |

| US9980669B2 (en) | 2011-11-07 | 2018-05-29 | Abbott Diabetes Care Inc. | Analyte monitoring device and methods |

| JP2013106166A (ja) * | 2011-11-14 | 2013-05-30 | Sony Corp | クロックゲーティング回路およびバスシステム |

| CN104011693B (zh) * | 2011-12-21 | 2017-09-12 | 英特尔公司 | 设置基于i/o带宽的处理器频率层的装置和方法 |

| CN102594344B (zh) * | 2012-01-09 | 2015-03-18 | 青岛海信移动通信技术股份有限公司 | 一种集中式时钟装置和移动终端设备 |

| TWI497304B (zh) * | 2012-03-13 | 2015-08-21 | Novatek Microelectronics Corp | 序列介面傳送方法及其裝置 |

| CN103324588B (zh) * | 2012-03-22 | 2016-05-04 | 联咏科技股份有限公司 | 序列接口传送方法及其装置 |

| US8943352B1 (en) | 2012-05-07 | 2015-01-27 | Dust Networks, Inc. | Low power timing, configuring, and scheduling |

| JP6103825B2 (ja) * | 2012-06-07 | 2017-03-29 | キヤノン株式会社 | 半導体集積回路、情報処理装置 |

| US9317460B2 (en) * | 2012-06-15 | 2016-04-19 | International Business Machines Corporation | Program event recording within a transactional environment |

| CN103513698B (zh) * | 2012-06-29 | 2017-03-01 | 联想(北京)有限公司 | 一种时钟信号校准方法、装置及电子设备 |

| US8710879B2 (en) * | 2012-07-06 | 2014-04-29 | Silicon Integrated System Corp. | Apparatus and method for multiplying frequency of a clock signal |

| US9968306B2 (en) | 2012-09-17 | 2018-05-15 | Abbott Diabetes Care Inc. | Methods and apparatuses for providing adverse condition notification with enhanced wireless communication range in analyte monitoring systems |

| US9129072B2 (en) * | 2012-10-15 | 2015-09-08 | Qualcomm Incorporated | Virtual GPIO |

| US9530398B2 (en) | 2012-12-06 | 2016-12-27 | White Eagle Sonic Technologies, Inc. | Method for adaptively scheduling ultrasound system actions |

| US9983905B2 (en) | 2012-12-06 | 2018-05-29 | White Eagle Sonic Technologies, Inc. | Apparatus and system for real-time execution of ultrasound system actions |

| US10499884B2 (en) | 2012-12-06 | 2019-12-10 | White Eagle Sonic Technologies, Inc. | System and method for scanning for a second object within a first object using an adaptive scheduler |

| US9529080B2 (en) | 2012-12-06 | 2016-12-27 | White Eagle Sonic Technologies, Inc. | System and apparatus having an application programming interface for flexible control of execution ultrasound actions |

| US10076313B2 (en) | 2012-12-06 | 2018-09-18 | White Eagle Sonic Technologies, Inc. | System and method for automatically adjusting beams to scan an object in a body |

| DE102013001143A1 (de) * | 2013-01-23 | 2014-07-24 | Giesecke & Devrient Gmbh | Verfahren zur Ausvührung eines Programms über einen Mikroprozessor auf einem Sicherheitsmodul |

| JP5892083B2 (ja) * | 2013-02-12 | 2016-03-23 | 日本電気株式会社 | パラメータ設定装置、パラメータ設定プログラム及びパラメータ設定方法 |

| US9823719B2 (en) | 2013-05-31 | 2017-11-21 | Intel Corporation | Controlling power delivery to a processor via a bypass |

| US9256276B2 (en) * | 2013-09-27 | 2016-02-09 | Intel Corporation | Utilization of processor capacity at low operating frequencies |

| EP4254209A3 (en) * | 2013-10-30 | 2023-11-22 | INTEL Corporation | A method, apparatus and system for measuring latency in a physical unit of a circuit |

| US9814106B2 (en) * | 2013-10-30 | 2017-11-07 | Apple Inc. | Backlight driver chip incorporating a phase lock loop (PLL) with programmable offset/delay and seamless operation |

| TWI497314B (zh) * | 2013-11-06 | 2015-08-21 | Univ Nat Chiao Tung | 適應性計算之無線處理器 |

| JP6381899B2 (ja) * | 2013-12-05 | 2018-08-29 | ルネサスエレクトロニクス株式会社 | 半導体装置の設計方法、設計支援プログラム、設計装置、及び、半導体装置 |

| US10200951B2 (en) * | 2014-02-20 | 2019-02-05 | Qualcomm Incorporated | Low power low latency protocol for data exchange |

| KR102320399B1 (ko) * | 2014-08-26 | 2021-11-03 | 삼성전자주식회사 | 전원 관리 칩, 그것을 포함하는 모바일 장치 및 그것의 클록 조절 방법 |

| US9841795B2 (en) | 2014-09-22 | 2017-12-12 | Nxp Usa, Inc. | Method for resetting an electronic device having independent device domains |

| KR102271469B1 (ko) | 2014-10-24 | 2021-06-30 | 삼성전자주식회사 | 반도체 장치 및 이를 포함하는 반도체 시스템 |

| CN104699578B (zh) * | 2015-01-09 | 2017-12-26 | 同济大学 | 一种以内升温方式检测时延故障的定温指令级自测试方法 |

| US9450582B2 (en) | 2015-02-03 | 2016-09-20 | Freescale Semiconductor, Inc. | Programmable buffer system |

| US9696782B2 (en) | 2015-02-09 | 2017-07-04 | Microsoft Technology Licensing, Llc | Battery parameter-based power management for suppressing power spikes |

| US10158148B2 (en) | 2015-02-18 | 2018-12-18 | Microsoft Technology Licensing, Llc | Dynamically changing internal state of a battery |

| US9748765B2 (en) | 2015-02-26 | 2017-08-29 | Microsoft Technology Licensing, Llc | Load allocation for multi-battery devices |

| JP6466740B2 (ja) * | 2015-03-02 | 2019-02-06 | 株式会社メガチップス | クロック生成回路 |

| WO2016164543A1 (en) | 2015-04-07 | 2016-10-13 | Analog Devices, Inc. | Quality factor estimation for resonators |

| US10432337B2 (en) * | 2015-05-15 | 2019-10-01 | Avago Technologies International Sales Pte. Limited | Apparatus and method for timestamping of data packets |

| CN104881529B (zh) * | 2015-05-18 | 2018-05-29 | 南京航空航天大学 | 基于有限状态机的采样保持控制策略的实现方法 |

| US10210919B2 (en) | 2015-06-03 | 2019-02-19 | Altera Corporation | Integrated circuits with embedded double-clocked components |

| US9503067B1 (en) * | 2015-06-22 | 2016-11-22 | Realtek Semiconductor Corporation | Time shifter and method thereof |

| US9874863B2 (en) * | 2015-08-24 | 2018-01-23 | Keysight Technologies, Inc. | Finite state machine-based trigger event detection employing interpolation |

| US9939862B2 (en) | 2015-11-13 | 2018-04-10 | Microsoft Technology Licensing, Llc | Latency-based energy storage device selection |

| US10061366B2 (en) | 2015-11-17 | 2018-08-28 | Microsoft Technology Licensing, Llc | Schedule-based energy storage device selection |

| US9793570B2 (en) | 2015-12-04 | 2017-10-17 | Microsoft Technology Licensing, Llc | Shared electrode battery |

| CN105608027B (zh) * | 2015-12-18 | 2018-10-19 | 华为技术有限公司 | 非易失存储设备和访问非易失存储设备的方法 |

| US10303203B2 (en) | 2016-01-25 | 2019-05-28 | Samsung Electronics Co., Ltd. | Semiconductor device, semiconductor system and method for operating semiconductor device |

| DE102017110821A1 (de) | 2016-01-25 | 2018-07-26 | Samsung Electronics Co., Ltd. | Halbleitervorrichtung |

| US10248155B2 (en) | 2016-01-25 | 2019-04-02 | Samsung Electronics Co., Ltd. | Semiconductor device including clock generating circuit and channel management circuit |

| US10296066B2 (en) | 2016-01-25 | 2019-05-21 | Samsung Electronics Co., Ltd. | Semiconductor device, semiconductor system, and method of operating the semiconductor device |

| US10209734B2 (en) | 2016-01-25 | 2019-02-19 | Samsung Electronics Co., Ltd. | Semiconductor device, semiconductor system, and method of operating the semiconductor device |

| KR102467172B1 (ko) * | 2016-01-25 | 2022-11-14 | 삼성전자주식회사 | 반도체 장치 |

| KR102474620B1 (ko) * | 2016-01-25 | 2022-12-05 | 삼성전자주식회사 | 반도체 장치, 반도체 시스템 및 반도체 장치의 동작 방법 |

| JP2017191564A (ja) * | 2016-04-15 | 2017-10-19 | 富士通株式会社 | 演算処理装置及び演算処理装置の制御方法 |

| US10445099B2 (en) * | 2016-04-19 | 2019-10-15 | Xiaolin Wang | Reconfigurable microprocessor hardware architecture |

| KR20170124017A (ko) * | 2016-04-29 | 2017-11-09 | 삼성전자주식회사 | 동작 전압을 조절하는 메모리 장치, 메모리 장치를 제어하는 어플리케이션 프로세서 및 메모리 장치의 동작방법 |

| JP6594533B2 (ja) * | 2016-05-17 | 2019-10-23 | 三菱電機株式会社 | コントローラシステム |

| US10254782B2 (en) * | 2016-08-30 | 2019-04-09 | Micron Technology, Inc. | Apparatuses for reducing clock path power consumption in low power dynamic random access memory |

| US10305495B2 (en) * | 2016-10-06 | 2019-05-28 | Analog Devices, Inc. | Phase control of clock signal based on feedback |

| US10659063B2 (en) * | 2016-11-01 | 2020-05-19 | Nvidia Corporation | Adaptive voltage frequency scaling for optimal power efficiency |

| JP2018120449A (ja) * | 2017-01-26 | 2018-08-02 | ソニーセミコンダクタソリューションズ株式会社 | 演算処理装置および情報処理システム |

| JP6819327B2 (ja) * | 2017-02-03 | 2021-01-27 | 富士通株式会社 | クロック生成回路、シリアル・パラレル変換回路及び情報処理装置 |

| TW201838392A (zh) * | 2017-02-10 | 2018-10-16 | 香港商凱歐斯科技(香港)有限公司 | 功能型手機及其操作方法 |

| US10120819B2 (en) * | 2017-03-20 | 2018-11-06 | Nxp Usa, Inc. | System and method for cache memory line fill using interrupt indication |

| KR102435034B1 (ko) * | 2017-06-21 | 2022-08-23 | 삼성전자주식회사 | 디지털 위상 고정 루프 및 디지털 위상 고정 루프의 동작 방법 |

| US10809790B2 (en) * | 2017-06-30 | 2020-10-20 | Intel Corporation | Dynamic voltage-level clock tuning |

| US10578435B2 (en) | 2018-01-12 | 2020-03-03 | Analog Devices, Inc. | Quality factor compensation in microelectromechanical system (MEMS) gyroscopes |

| US11360504B2 (en) * | 2018-05-25 | 2022-06-14 | Advanced Micro Devices, Inc. | Adaptable voltage margin for a processor |

| EP3806336A4 (en) | 2018-06-05 | 2021-08-04 | Panasonic Intellectual Property Management Co., Ltd. | INPUT / OUTPUT CIRCUIT |

| GB201810478D0 (en) * | 2018-06-26 | 2018-08-08 | Nordic Semiconductor Asa | Precision timing between systems |

| US11041722B2 (en) | 2018-07-23 | 2021-06-22 | Analog Devices, Inc. | Systems and methods for sensing angular motion in the presence of low-frequency noise |

| CN111435267A (zh) * | 2019-01-15 | 2020-07-21 | 海信集团有限公司 | 功耗自动调整的方法、装置、设备及计算机可读存储介质 |

| CN109787625B (zh) * | 2019-03-05 | 2022-04-05 | 上海芷锐电子科技有限公司 | 一种基于双pll的系统超频引起的电压毛刺保护系统 |

| IT201900006633A1 (it) * | 2019-05-08 | 2020-11-08 | Stmicroelectronics Application Gmbh | Sistema di elaborazione, relativo circuito integrato, dispositivo e procedimento |

| CN110081933B (zh) * | 2019-05-10 | 2021-07-20 | 上海岚盒信息技术有限公司 | 振动巡检仪及其低功耗频域变换方法、计算机可读存储介质 |

| CN110413558A (zh) * | 2019-07-15 | 2019-11-05 | 广芯微电子(广州)股份有限公司 | 一种实现低功耗串口模块动态分频方法 |

| KR20210062499A (ko) * | 2019-11-21 | 2021-05-31 | 에스케이하이닉스 주식회사 | 반도체 메모리 장치 및 그 동작 방법 |

| CN112104537B (zh) * | 2020-03-28 | 2022-04-19 | 上海芯郡电子科技有限公司 | 一种通信控制器 |

| KR102414817B1 (ko) * | 2020-05-25 | 2022-06-30 | 윈본드 일렉트로닉스 코포레이션 | 지연 락 루프 디바이스와 그 동작 방법 |