CN100538910C - 测试存储单元的装置和方法 - Google Patents

测试存储单元的装置和方法 Download PDFInfo

- Publication number

- CN100538910C CN100538910C CNB028106474A CN02810647A CN100538910C CN 100538910 C CN100538910 C CN 100538910C CN B028106474 A CNB028106474 A CN B028106474A CN 02810647 A CN02810647 A CN 02810647A CN 100538910 C CN100538910 C CN 100538910C

- Authority

- CN

- China

- Prior art keywords

- bit line

- storage unit

- coupled

- voltage level

- latch

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

- G11C29/028—Detection or location of defective auxiliary circuits, e.g. defective refresh counters with adaption or trimming of parameters

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/02—Detection or location of defective auxiliary circuits, e.g. defective refresh counters

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/50—Marginal testing, e.g. race, voltage or current testing

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C29/00—Checking stores for correct operation ; Subsequent repair; Testing stores during standby or offline operation

- G11C29/04—Detection or location of defective memory elements, e.g. cell constructio details, timing of test signals

- G11C29/50—Marginal testing, e.g. race, voltage or current testing

- G11C2029/5004—Voltage

Abstract

一种用于测试存储单元的装置和方法,所述方法包括:将第一和第二存储单元分别连接到第一和第二位线;通过第一和第二位线从第一和第二存储单元中读出数据;以及比较第一和第二位线的电压电平。

Description

技术领域

本发明涉及使用结构测试技术加速对存储器阵列的测试,这是用传统功能测试所不能做到的。

背景技术

随着在许多电子器件中常用的存储器阵列日益增大和封装日益密集,测试的复杂程度成指数增加,彻底地测试各个单元以及其它存储器阵列元件所需的时间亦成指数增加。结果,制造测试过程需要更长的时间才能完成,已发现的故障的调测工作亦需更长的时间才能完成。

现有技术的通常做法是利用功能测试,即将各种数值组合写入到存储器阵列的存储单元中,再从中读出。但是,由于存储器阵列中的行和列存储单元的尺寸不断增大,充分测试存储单元所需的写入和读出操作的次数成指数增加,导致进行这种操作所需的时间量相应也成指数增加。这样就产生了需要在零件的产量和测试覆盖的彻底性之间权衡取舍的问题,增加了将有故障的存储器阵列发送到用户手中的可能性。

这种功能测试也不能很好地提供跟踪故障源所需的信息。实际上,当发现单元返回的数值不是最后写入的数值时,所述结果并不能说明这到底是地址解码器故障、数据锁存器故障、数据线故障、存储单元故障还是驱动程序故障。因此,需要进行进一步的测试来分离出存储器阵列中的故障、以便提高以后的产量,而且随着存储器阵列的尺寸不断增大,进行这些附加测试所需的时间就更长。

发明内容

本发明提供一种用于测试存储单元的装置,它包括:耦合到第一位线和第二位线的第一存储单元;耦合到第三位线和第四位线的第二存储单元;地址解码器,它耦合到所述第一和第二存储单元以便能存取所述第一和第二存储单元;以及第一比较器电路,它耦合到所述第一和第三位线,以便当通过所述第一位线从所述第一存储单元输出数据并且通过所述第三位线从所述第二存储单元输出数据时,将所述第一位线上的电压电平与所述第三位线上的电压电平进行比较;和第二比较器电路,它耦合到所述第二位线和第四位线,以便当通过所述第二位线从所述第一存储单元、以及通过所述第四位线从所述第二存储单元输出通过所述第一位线和所述第三位线输出的数据补码时,将所述第二位线上的电压电平与所述第四位线上的电压电平进行比较。

本发明还提供一种用于测试存储单元的方法,它包括:向第一和第二存储单元写入相同的数据;将所述第一存储单元耦合到第一位线;将所述第一存储单元耦合到第二位线;将所述第二存储单元耦合到第三位线;将所述第二存储单元耦合到第四位线;将所述第一和第三位线耦合到第一比较器电路的输入端;将所述第二和第四位线耦合到第二比较器电路的输入端;通过所述第一位线从所述第一存储单元并且通过所述第三位线从所述第二存储单元读出所述相同的数值;通过所述第一位线从所述第一存储单元并且通过所述第三位线从所述第二存储单元读出所述相同的数值,所述相同的数值是通过第一位线和第三位线传输的数值的补码;比较所述第一和第三位线上的电压电平;和比较所述第二和第四位线上的电压电平。

本发明还提供一种存储器阵列中的比较器电路,它包括:第一位线,它耦合到存储器阵列中的第一存储单元;第二位线,它耦合到所述存储器阵列中的第二存储单元;第三位线,它耦合到所述存储器阵列中的所述第一存储单元;复用器,它耦合到所述第二位线和所述第三位线;和比较器,它具有耦合到所述第一位线的第一输入端,和耦合到所述复用器的第二输入端,所述复用器可选择地耦合到所述第二位线或者所述第三位线。

附图说明

参考以下的详细说明,本发明的目的、特征和优点对于本专业的技术人员就可一目了然,附图中:

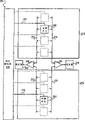

图1是本发明一个实施例的方框图。

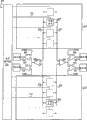

图2是本发明另一个实施例的方框图。

图3是本发明又一个实施例的方框图。

图4是本发明一个实施例的流程图。

图5是本发明另一个实施例的流程图。

图6是本发明又一个实施例的流程图。

具体实施方式

在以下的说明中,为了说明,提出了许多细节以便提供对本发明的透彻的理解。但对本专业的技术人员来说,很明显,这些具体的细节并不是实现本发明所必需的。

本发明涉及存储器阵列,其中有一个以行和列的形式组织而成的存储单元阵列,这些单元可被动态和随机地存取,如常用的DRAM和SRAM集成电路(IC)。但本专业的技术人员应理解,本发明也适用于其它电路阵列,包括(但不限于)可擦除ROM IC、可编程逻辑器件以及在微处理器中组织成阵列的元件。

图1是本发明一个实施例的方框图。所示存储器阵列100包括:上半部110和下半部112;通过多条字线(包括字线130和132)连接到上半部110和下半部112的地址解码器120;比较器电路140;以及锁存器142。在上半部110和下半部112中分别是存储单元160和162,它们分别连接到位线170和172。位线170和172依次连接到比较器140的输入端,比较器140又连接到锁存器142。在讨论本发明时为清晰起见,在上半部100仅示出存储单元160和位线170,在下半部112仅示出存储单元162和位线172。但本专业的技术人员都知道,典型的存储器阵列会有许多位线,每条位线都有许多存储单元与之相连。

在存储器阵列100正常工作时,地址解码器120将部分存储器地址解码并接通一连接地址解码器120与上半部110的合适的字线和一连接地址解码器120与下半部112的合适的字线,以便能够存取上半部110和下半部112中合适的存储单元。根据所进行的存储器操作,数据通过与上半部110和下半部112中的存储单元相连接的位线写入存储单元或从中读出。例如,在对与存储单元160和162相关联的存储器地址进行写入操作时,地址解码器120将部分存储器地址解码并接通字线130和132,以便能分别通过位线170和172存取存储单元160和162。

在本发明的一个实施例中,对存储单元160和162进行的测试是先分别通过位线170和172向每个存储单元160和162写入相同的数据。然后将位线170和172预充电到高电压状态或低电压状态,通常分别称为Vcc或Vss。地址解码器120将与存储单元160和162相关联的部分存储器地址解码。然后存储单元160和162分别把它们的数据输出到位线170和172上。比较器电路140是单一比较器,它不断地比较位线170和172上的电压,并不断产生表明位线170和172上的电压是否基本上相同的信号。在一个实施例中,测试过程中可以在一个或多个预定的时刻触发锁存器142,以便捕捉这些时刻比较器电路140的输出的状态,例如在示范的波形180和182的进行过程中示范的时刻t1和t2,分别表示在位线170和172上样值从高到低的转变。在另一实施例中,可以以“粘性锁存器”的形式实现锁存器142,它锁存并存储任何来自比较器电路140的表明位线170和172上的电压变为显著不同的信号的出现。

在正常使用存储器阵列过程中读存储单元时,通常的做法是将位线预充电到高电压状态。所以,在本发明的一个实施例中,对存储单元的测试在读存储单元时仅在位线充电到高电压状态时进行。但是,由于常用的存储单元的设计的缘故,仅限于预充电到高状态会导致存储单元中多达一半的存储单元电路因过量漏电或其它情况而不能测试。所以,本发明的另一实施例需要在位线预充电到高和低的两种状态的情况下进行测试。

使用比较器电路140来测试存储单元160和162是基于以下假定:即设计相同的存储单元若连接到设计相同的位线,应能以基本上相同的速率将它们关联的位线电压驱动到高或低。简言之,在位线170和172上所见的波形(例如示范的波形180和182)看上去应基本上相同。使用比较器电路140还基于以下假定:即不大可能因过程改变或存储器阵列100中的其它缺陷而在上半部110和下半部112中产生相同的故障,因此以下情况也是极不可能的:即存储单元160和162以相同的方式有缺陷而在位线170和172上所得的错误波形看上去还基本上相同。换句话说,已假设:杂质,例如灰尘颗粒,或制造过程错误对上半部110和下半部112不会具有相同的影响而导致按照本发明所进行的测试揭示不出上半部110和下半部112之间任何一对存储单元之间的差异。

按照本专业技术人员熟知的常用做法,所示存储器阵列100分成上半部110和下半部112、使得可以集中设置缓冲区和其它关联电路因而可以将位线保持在很短以使位线具有更理想的电特性。本发明采用这种常用做法,利用所提供的同一中心位置来集中设置比较器电路,例如比较器140,以便比较邻近位线的电特性。但是,对本专业技术人员来说,很清楚的是将存储器阵列100分成上半部110和下半部112并不是实现本发明所必需的。也可以利用包括存储器阵列的元件的许多其它布局或安排来实现本发明。

图2是本发明另一个实施例的方框图。存储器阵列200与图1的存储器阵列100基本上相同,图2中编号为2xx的项目对应于图1中编号为1xx的项目。同样对应于存储器阵列100,存储器阵列200包括地址解码器220,后者通过字线230耦合到上半部210中的存储单元260并通过字线232耦合到下半部212中的存储单元262。

但和存储单元160和162不同的是,存储单元160和162各自仅连接到一条位线,而存储单元260和262各自连接到一对位线(分别为位线270和274以及位线272和276)。在一个实施例中,各对位线用于各存储单元,向每个存储单元写入数据位及其补码以及从每个存储单元读出数据位及其补码。在所述实施例中,通常的做法是使每对位线通到读出放大器的差分输入端上,供读出数据位及其补码。但在另一实施例中,两条(或更多)位线用来提供两条(或更多)完全独立的通路,通过所述通路,可以将数据写入每个存储单元或从每个存储单元读出。在所述实施例中位线的这种用法常常反映了多端口存储器元件的常用实现方法。

不管将一对位线连接到存储单元260和262中的每一个的目的如何,位线270和272以对应于图1中存储器阵列100的位线170和172的方式连接到比较器电路240的输入端,而位线274和276以对应于图1中存储器阵列100的位线170和172的方式连接到比较器电路244的输入端。同样,对应于图1,比较器电路240和244的输出端连接到锁存器242和246。

在本发明的一个实施例中(其中利用传输数据及其补码的位线对向存储单元写入和从存储单元读出),采用以下方法对存储单元260和262进行测试:先分别通过位线270和274以及位线272和276向每个存储单元260和262写入相同的数据。然后将位线270到276预充电到高电压状态或低电压状态。地址解码器220将与存储单元260和262相关联的部分存储器地址解码。然后存储单元260和262将它们的数据分别输出到位线270和274以及位线272和276上。比较器电路240是单一比较器,它不断地比较位线270和272上的电压并不断产生表明位线270和272上的电压是否基本上相同的信号。比较器电路244对位线274和276上的电压作同样的工作。在一个实施例中,测试过程中可以在一个或多个时刻触发锁存器242和246,以便捕捉在那些时刻比较器电路240和244的输出的状态。在另一实施例中,可以以“粘性锁存器”的形式来实现锁存器240和244,它锁存并存储任何来自与它们相连的比较器电路的表明它们所关联的位线上的电压变为显著不同的信号的出现。

此外,在一个实施例中(其中利用传输数据及其补码的位线对向存储单元写入和从存储单元读出并用读出放大器从存储单元中读出),所述读出放大器也可配置成比较器,作为比较器电路来测试存储单元。通过使用复用器来根据需要选择性地连接或断开不同的位线对,以便使读出放大器可以完成这两种功能中的这一个或另一个,就可以做到这一点。或者,在另一实施例中,读出放大器和比较器仍为单独的元件。

在本发明的又一实施例中(其中利用连接到每个存储单元的位线中的任一条向存储单元独立地写入或从存储单元独立地读出),如同多端口存储器的情况一样,利用与上述大致相同的方式测试存储单元。但为了确保写入存储单元260和262的功能完美无缺,对各存储单元260和262的测试要进行两次,先用位线270和272分别向存储单元260和262写入相同的数据,然后再用位线274和276重复操作。

图3是本发明又一个实施例的方框图。存储器阵列300与图2的存储器阵列200基本上相同,图3中编号为3xx的项目对应于图2中编号为2xx的项目,但比较器电路及其关联的锁存器除外。以对应于存储器阵列200的方式,存储器阵列300包括通过字线330耦合到上半部310中的存储单元360并且通过字线332耦合到下半部312中的存储单元362的地址解码器320。同样,以对应于存储器阵列200的方式,存储单元360耦合到位线370和374,存储单元362耦合到位线372和376。

和图2所示的实施例不同,图3的比较器电路各自包含一个减法电路和一对比较器。位线370和372连接到减法电路390的输入端,减法电路390从位线372中一位线的电压电平中减去位线370中另一位线的电压电平并输出代表所述减法所得的差的电压,它可以是正也可是负的电压输出。所述减法电路390的输出端又连接到比较器340和341中每一个的两个输入端之一。相应地,位线374和376连接到减法电路392的输入端,减法电路392的输出端连接到比较器344和345中每一个的两个输入端之一。比较器340和344中每一个的另一输入端连接到高电压电平基准+vref,相应地,比较器341和345中每一个的另一输入端连接到低电压基准-vref。比较器340、341、344和345的输出端分别连接到锁存器342、343、346和347的输入端。

无论存储器阵列300的存储单元是用一对位线写入和读出,或是连接到每个单元的两条位线各用来进行独立的写入和读出操作,对存储器阵列300的存储单元360和362的测试按上述对图2的存储单元260和262的同样方式进行。但是,如图3所示的各自包括减法电路和一对比较器的比较器电路的配置提供了更大的能力来控制在进行比较的各位线对上电压相互差异的程度。更精确地说,靠调节+vref和-vref,就可使比较器340和344偏置,以便在比较器340或344输出表示故障的信号之前,使位线370和372上的电压电平相差到可以调节的程度。如果位线370和372之间的电压电平差是这样的、使得它上升到超过+vref,则比较器340向锁存器342输出表示此情况的信号,而如果位线370和372之间的电压电平差是这样的、使得它降低到低于-vref,则比较器344向锁存器346输出表示此情况的信号。

图4是本发明一个实施例的流程图。从400开始,在410将相同的数据写入存储器阵列的存储单元对中。在420,两个存储单元各自相应的位线对连接到比较器电路的输入端。在每个存储单元仅连接一条位线的实施例中,这就是指在420,两条位线中每一条都连接到单一比较器电路的输入端。或者,在每个存储单元连接到两条位线的另一实施例中,在420,一个存储单元的每条位线和另一存储单元的相应位线一起连接到比较器电路。

在430,从该存储单元对的每个单元中读出所述相同的数据,并比较连接到比较器电路的每对相应的位线。如果在相应的位线对之间的电压电平有很大不同,则在460就发现了故障。但如果在相应的位线对之间没有显著不同的电压电平,则在450,对所述存储单元对以及它们所连接的位线的测试就可通过。

图5是本发明另一实施例的流程图。对存储器阵列中存储单元的测试从500开始。在510,将相同的数据写入存储器阵列的一对存储单元中,在520,连接到该对存储单元中各存储单元的相应位线对连接到比较器电路的输入端。然后,在530,从这对存储单元中读出所述相同的数据,并比较相应位线对的电压电平。如果,在540,在相应的位线对之间的电压电平中发现了显著的差异,则在550将发现显著区别的事实锁存。但是,不论在540是否发现显著的差异,如果没有更多的存储单元要测试,则在560测试结束。否则,在510对另一对存储单元重复该测试。

举例来说,参考图1和图5,在510,利用位线170和172分别将相同的数据写入存储单元160和162中。在520,位线170和172连接到比较器电路140的输入端。在530,分别用位线170和172从存储单元160和162中读出已写入存储单元160和162中的相同数据,并用比较器电路140来比较位线170和172上的电压电平。如果比较器电路140检测到位线170和172之间的电压有显著的区别,则所述事实的指示由锁存器142锁存。如果在560,有更多的存储单元要测试,则在510,将另一对相同的数值写入另一对存储单元。或者,对存储单元160和162重复该测试,先将位线170和172预充电到高状态,进行读出所述相同数据的测试,然后预充电到低状态,进行相同数据的另一次读出。

举另一例来说明,参考图2和图5,其中存储单元260和262是利用位线对来写入和读出的,具体地说,位线270和272用来写入和读出数据,而位线274和276用来写入和读出数据的补码。在510,用位线270和272分别将相同的数据写入存储单元260和262中,而位线274和276则分别用来向存储单元260和262写入相同的补码数据。在520,位线270和272连接到比较器电路240的输入端,位线274和276连接到比较器电路244的输入端。在530,读出已写入存储单元260和262的相同数据和补码,利用位线270和274从存储单元260中读出,而利用位线272和276从存储单元262中读出。如果比较器电路240在读出数据时检测到位线270和272之间的电压有显著不同,则所述事实的指示由锁存器242锁存。相应的,如果比较器电路244在读出补码数据时检测到位线274和276之间的电压有显著不同,则所述事实的指示由锁存器244锁存。如果在560,有更多的存储单元要测试,则在510,将另一对相同的数值写入另一对存储单元。或者,对存储单元260和262重复进行测试,位线270、272、274和276预充电到高状态作一次测试,然后预充电到低状态作另一次测试。

图6是本发明又一实施例的流程图。在存储器阵列中利用位线对读出和写入数据位及其补码的存储单元测试在600开始。在610,将相同的数据写入存储器阵列的一对存储单元中,在620,耦合到该对存储单元中每一个存储单元的相应数据位线和补码数据位线连接到比较器电路的输入端。然后在630,设定比较器电路所用的电压基准。在640,从该对存储单元中读出所述相同的数据,并比较相应的数据和补码数据位线对上的电压电平。如果,在650,发现在相应的位线对中的电压电平有显著差异,则在660,发现显著差异的事实被锁存。但是,不论在650是否发现这种显著差异,如果没有更多的存储单元要测试,则在670测试结束。否则,在610对另一对存储单元重复该测试。或者,如果需要在读出相同数据期间利用高和低预充电来测试位线,那么,也可以重复进行所述测试。

举例来说,参考图3和图6,其中存储单元360和362是利用位线对写入和读出的,具体地说,位线370和372用来写入和读出数据,而位线374和376用来写入和读出数据的补码。在610,利用位线370和372分别将相同的数据写入存储单元360和362中,而位线374和376则分别用来向存储单元360和362写入相同的补码数据。在620,位线370和372连接到减法电路390的输入端,所述减法电路390和比较器电路340和341一起也包括比较器电路。相应地,位线374和376连接到减法电路392的输入端,所述减法电路392和比较器电路344和345一起也包括比较器电路。在630,设定耦合到比较器340和341输入端的电压基准+vref和耦合到比较器344和345输入端的电压基准-vref。在640,读出早先已写入存储单元360和362的相同数据和所述数据的补码,利用位线370和374从存储单元360中读出,而利用位线372和376从存储单元362中读出。在650,如果发现在相应的位线对370和372,或位线对374和376之间的电压电平有显著差异,则在660,此事的发生由锁存器342、343、346或347中适当的一个锁存。

更具体地说,减法电路390从位线372上的电压中减去位线370上的电压,并向比较器340和341的输入端输出代表所得差的电压。如果在位线370和372之间的电压电平有差异,则减法电路390的输出就会是非零的电压电平,或为正或为负,取决于位线370或372中哪一个具有更高的电压电平。比较器340比较减法电路390的所述输出,如果所述输出的电压电平高于+vref,则所述事实的指示由锁存器342锁存。同理,比较器341比较减法电路390的输出,如果所述输出的电压电平低于-vref,则所述事实的指示由锁存器343锁存。相应地,减法电路392把代表位线374和376的电压电平之间差异的输出提供给比较器344和345的输入端,比较器344和345分别将所述输出与+vref和-vref进行比较,所述输出的电压电平升高到超过+vref或下降到低于-vref的指示分别由锁存器346和347锁存。

如果在670,还有更多的存储单元要测试,则在610,将另一对相同的数据写入另一对存储单元。或者,对存储单元360和362重复该测试,位线370、372、374和376预充电到高状态进行一次测试,然后预充电到低状态进行另一次测试。

以上结合优选实施例对本发明作了说明。很明显对于本专业的技术人员而言,根据上述说明,许多替换、修改、变化和用途是显而易见的。对于本专业的技术人员来说,显然,也可以在支持电子器件的其它功能中实现本发明。

以上在部分地可通过位线存取的存储单元阵列的范围内描述了本发明的示范实施例。但本发明适用于各种电子、微电子和微机械装置。

Claims (22)

1.一种用于测试存储单元的装置,它包括:

耦合到第一位线和第二位线的第一存储单元;

耦合到第三位线和第四位线的第二存储单元;

地址解码器,它耦合到所述第一和第二存储单元以便能存取所述第一和第二存储单元;

第一比较器电路,它耦合到所述第一和第三位线,以便当通过所述第一位线从所述第一存储单元输出数据并且通过所述第三位线从所述第二存储单元输出数据时,将所述第一位线上的电压电平与所述第三位线上的电压电平进行比较;和

第二比较器电路,它耦合到所述第二位线和第四位线,以便当通过所述第二位线从所述第一存储单元、以及通过所述第四位线从所述第二存储单元输出通过所述第一位线和所述第三位线输出的数据补码时,将所述第二位线上的电压电平与所述第四位线上的电压电平进行比较。

2.如权利要求1所述的装置,其特征在于:所述地址解码器将部分存储器地址解码。

3.如权利要求1所述的装置,其特征在于:所述第一和第二存储单元是动态RAM存储单元。

4.如权利要求1所述的装置,其特征在于:所述第一和第二存储单元是静态RAM存储单元。

5.如权利要求1所述的装置,其特征在于:所述第一比较器电路包括单一比较器,所述比较器的第一输入端耦合到所述第一位线,而所述比较器的第二输入端耦合到所述第三位线,并且所述第二比较器电路包括单一比较器,所述比较器的第一输入端耦合到所述第二位线,而所述比较器的第二输入端耦合到所述第四位线。

6.如权利要求5所述的装置,其特征在于:所述第一比较器的输出端耦合到第一锁存器,以便存储表明所述第一位线上的所述电压电平与所述第三位线上的所述电压电平显著不同的指示,和所述第二比较器的输出端耦合到第二锁存器,以便存储表明所述第二位线上的所述电压电平与所述第四位线上的所述电压电平显著不同的指示。

7.如权利要求6所述的装置,其特征在于:所述第一和第二锁存器的触发时间是可调的。

8.如权利要求6所述的装置,其特征在于:所述第一锁存器是粘性锁存器,任何时候当发生表明所述第一位线上的所述电压电平与所述第三位线上的所述电压电平显著不同的指示时,触发所述锁存器锁存这种指示,并且所述第二锁存器是粘性锁存器,任何时候当发生表明所述第三位线上的所述电压电平与所述第四位线上的所述电压电平显著不同的指示时,触发所述锁存器锁存这种指示。

9.如权利要求1所述的装置,其特征在于所述第一和第二比较器电路包括:

减法电路,所述减法电路的第一输入端耦合到所述第一位线,而所述减法电路的第二输入端耦合到所述第二位线;

耦合到所述减法电路的输出端的第一比较器;以及

耦合到所述减法电路的输出端的第二比较器。

10.如权利要求9所述的装置,其特征在于:

所述第一比较器的所述输出端耦合到第一锁存器,以便存储表明所述第一位线和所述第二位线之间的电压电平差升高到超过第一基准电压的指示;以及

所述第二比较器的所述输出端耦合到第二锁存器,以便存储表明所述第一位线和所述第二位线之间的电压电平差下降到低于第二基准电压的指示。

11.如权利要求10所述的装置,其特征在于:所述第一和第二基准电压是可调的。

12.如权利要求10所述的装置,其特征在于:所述第一和第二锁存器的触发时间是可调的。

13.如权利要求10所述的装置,其特征在于:所述第一和第二锁存器是粘性锁存器,使得所述第一锁存器锁存表明所述第一位线和所述第二位线之间的所述电压电平差已经升高到超过所述第一基准电压的任何指示、而所述第二锁存器锁存表明所述第一位线和所述第二位线之间的所述电压电平差已经下降到低于所述第二基准电压的任何指示。

14.一种用于测试存储单元的方法,它包括:

向第一和第二存储单元写入相同的数据;

将所述第一存储单元耦合到第一位线;

将所述第一存储单元耦合到第二位线;

将所述第二存储单元耦合到第三位线;

将所述第二存储单元耦合到第四位线;

将所述第一和第三位线耦合到第一比较器电路的输入端;

将所述第二和第四位线耦合到第二比较器电路的输入端;

通过所述第一位线从所述第一存储单元并且通过所述第三位线从所述第二存储单元读出所述相同的数值;

通过所述第一位线从所述第一存储单元并且通过所述第三位线从所述第二存储单元读出所述相同的数值,所述相同的数值是通过第一位线和第三位线传输的数值的补码;

比较所述第一和第三位线上的电压电平;和

比较所述第二和第四位线上的电压电平。

15.如权利要求14所述的方法,其特征在于还包括:锁存来自所述第一比较器电路的表明所述第一位线上的电压电平与所述第三位线上的电压电平是否显著不同的指示,和锁存来自所述第一比较器电路的表明所述第二位线上的电压电平与所述第四位线上的电压电平是否显著不同的指示。

16.如权利要求14所述的方法,其特征在于还包括:设定所述第一位线和所述第三位线之间电压电平显著差异的程度,以及第二位线和所述第四位线之间电压电平显著差异的程度。

17.一种存储器阵列中的比较器电路,它包括:

第一位线,它耦合到存储器阵列中的第一存储单元;

第二位线,它耦合到所述存储器阵列中的第二存储单元;

第三位线,它耦合到所述存储器阵列中的所述第一存储单元;

复用器,它耦合到所述第二位线和所述第三位线;和

比较器,它具有耦合到所述第一位线的第一输入端,和耦合到所述复用器的第二输入端,所述复用器可选择地耦合到所述第二位线或者所述第三位线。

18.如权利要求17所述的比较器电路,其特征在于:所述第一和第二存储单元是动态RAM存储单元。

19.如权利要求17所述的比较器电路,其特征在于:所述第一和第二存储单元是静态RAM存储单元。

20.如权利要求17所述的比较器电路,其特征在于:所述比较器的所述输出端耦合到一个锁存器,以便存储表明所述第一位线和所述第三位线之间的电压电平差存在显著不同的指示。

21.如权利要求20所述的比较器电路,其特征在于:可以调整所述锁存器的触发时间。

22.如权利要求20所述的比较器电路,其特征在于:所述锁存器是粘性锁存器,它可被触发以锁存表明所述第一位线上的所述电压电平与所述第三位线上的所述电压电平显著不同的指示。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US09/823,642 | 2001-03-30 | ||

| US09/823,642 US6757209B2 (en) | 2001-03-30 | 2001-03-30 | Memory cell structural test |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1537312A CN1537312A (zh) | 2004-10-13 |

| CN100538910C true CN100538910C (zh) | 2009-09-09 |

Family

ID=25239313

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB028106474A Expired - Fee Related CN100538910C (zh) | 2001-03-30 | 2002-03-08 | 测试存储单元的装置和方法 |

Country Status (10)

| Country | Link |

|---|---|

| US (1) | US6757209B2 (zh) |

| EP (1) | EP1374250B1 (zh) |

| JP (1) | JP2004530243A (zh) |

| KR (1) | KR100544362B1 (zh) |

| CN (1) | CN100538910C (zh) |

| AT (1) | ATE329354T1 (zh) |

| DE (1) | DE60212103T2 (zh) |

| HK (1) | HK1060437A1 (zh) |

| MY (1) | MY127555A (zh) |

| WO (1) | WO2002080183A2 (zh) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7480195B2 (en) * | 2005-05-11 | 2009-01-20 | Micron Technology, Inc. | Internal data comparison for memory testing |

| US7602778B2 (en) * | 2005-06-29 | 2009-10-13 | Cisco Technology, Inc. | System and methods for compressing message headers |

| JP4773791B2 (ja) * | 2005-09-30 | 2011-09-14 | 富士通セミコンダクター株式会社 | 半導体記憶装置、およびメモリテスト回路 |

| US7548473B2 (en) * | 2006-04-14 | 2009-06-16 | Purdue Research Foundation | Apparatus and methods for determining memory device faults |

| CN101714407B (zh) * | 2009-11-12 | 2012-08-08 | 钰创科技股份有限公司 | 行地址保留存储单元触发电路及行地址保留存储单元装置 |

| JP6430194B2 (ja) * | 2014-09-29 | 2018-11-28 | ルネサスエレクトロニクス株式会社 | 半導体記憶装置 |

| CN108051767B (zh) * | 2018-01-04 | 2019-07-19 | 南京国睿安泰信科技股份有限公司 | 一种用于集成电路测试仪的自动诊断方法 |

Family Cites Families (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPS57105897A (en) * | 1980-12-23 | 1982-07-01 | Fujitsu Ltd | Semiconductor storage device |

| US4503536A (en) | 1982-09-13 | 1985-03-05 | General Dynamics | Digital circuit unit testing system utilizing signature analysis |

| US4527272A (en) | 1982-12-06 | 1985-07-02 | Tektronix, Inc. | Signature analysis using random probing and signature memory |

| JPS61261895A (ja) * | 1985-05-16 | 1986-11-19 | Toshiba Corp | 半導体記憶装置 |

| JPS61292300A (ja) * | 1985-06-18 | 1986-12-23 | Toshiba Corp | オンチツプメモリテスト容易化回路 |

| JP2523586B2 (ja) * | 1987-02-27 | 1996-08-14 | 株式会社日立製作所 | 半導体記憶装置 |

| JP2831767B2 (ja) * | 1990-01-10 | 1998-12-02 | 株式会社アドバンテスト | 半導体メモリ試験装置 |

| JPH04212799A (ja) * | 1990-01-31 | 1992-08-04 | Nec Ic Microcomput Syst Ltd | テスト回路内蔵半導体メモリ |

| JPH04211160A (ja) * | 1990-03-20 | 1992-08-03 | Mitsubishi Electric Corp | 半導体記憶装置 |

| KR940007240B1 (ko) * | 1992-02-21 | 1994-08-10 | 현대전자산업 주식회사 | 병렬 테스트 회로 |

| JP3251637B2 (ja) * | 1992-05-06 | 2002-01-28 | 株式会社東芝 | 半導体記憶装置 |

| JP3307473B2 (ja) * | 1992-09-09 | 2002-07-24 | ソニー エレクトロニクス インコーポレイテッド | 半導体メモリの試験回路 |

| JPH07211099A (ja) * | 1994-01-12 | 1995-08-11 | Sony Corp | 半導体記憶装置の試験装置 |

| JPH07307100A (ja) * | 1994-05-11 | 1995-11-21 | Nec Corp | メモリ集積回路 |

| US5708598A (en) * | 1995-04-24 | 1998-01-13 | Saito; Tamio | System and method for reading multiple voltage level memories |

| JP3607407B2 (ja) * | 1995-04-26 | 2005-01-05 | 株式会社日立製作所 | 半導体記憶装置 |

| US5973967A (en) * | 1997-01-03 | 1999-10-26 | Programmable Microelectronics Corporation | Page buffer having negative voltage level shifter |

| US6002623A (en) * | 1997-02-12 | 1999-12-14 | Micron Technology, Inc. | Semiconductor memory with test circuit |

| JPH10308100A (ja) * | 1997-05-06 | 1998-11-17 | Mitsubishi Electric Corp | 半導体記憶装置 |

| KR100269319B1 (ko) * | 1997-12-29 | 2000-10-16 | 윤종용 | 동시칼럼선택라인활성화회로를구비하는반도체메모리장치및칼럼선택라인제어방법 |

| US5963497A (en) * | 1998-05-18 | 1999-10-05 | Silicon Aquarius, Inc. | Dynamic random access memory system with simultaneous access and refresh operations and methods for using the same |

| KR100308191B1 (ko) | 1998-05-28 | 2001-11-30 | 윤종용 | 빌트-인패럴테스트회로를구비한반도체메모리장치 |

| JP2001210095A (ja) * | 2000-01-24 | 2001-08-03 | Mitsubishi Electric Corp | メモリモジュール |

| US6353568B1 (en) * | 2000-12-29 | 2002-03-05 | Lsi Logic Corporation | Dual threshold voltage sense amplifier |

-

2001

- 2001-03-30 US US09/823,642 patent/US6757209B2/en not_active Expired - Fee Related

-

2002

- 2002-01-21 MY MYPI20020232A patent/MY127555A/en unknown

- 2002-03-08 JP JP2002578510A patent/JP2004530243A/ja not_active Ceased

- 2002-03-08 EP EP02717602A patent/EP1374250B1/en not_active Expired - Lifetime

- 2002-03-08 CN CNB028106474A patent/CN100538910C/zh not_active Expired - Fee Related

- 2002-03-08 KR KR1020037012883A patent/KR100544362B1/ko not_active IP Right Cessation

- 2002-03-08 WO PCT/US2002/007340 patent/WO2002080183A2/en active IP Right Grant

- 2002-03-08 DE DE60212103T patent/DE60212103T2/de not_active Expired - Fee Related

- 2002-03-08 AT AT02717602T patent/ATE329354T1/de not_active IP Right Cessation

-

2004

- 2004-05-13 HK HK04103384A patent/HK1060437A1/xx not_active IP Right Cessation

Also Published As

| Publication number | Publication date |

|---|---|

| US6757209B2 (en) | 2004-06-29 |

| DE60212103D1 (de) | 2006-07-20 |

| DE60212103T2 (de) | 2007-01-04 |

| WO2002080183A3 (en) | 2003-04-17 |

| US20020141259A1 (en) | 2002-10-03 |

| MY127555A (en) | 2006-12-29 |

| EP1374250A2 (en) | 2004-01-02 |

| JP2004530243A (ja) | 2004-09-30 |

| KR100544362B1 (ko) | 2006-01-23 |

| WO2002080183A2 (en) | 2002-10-10 |

| HK1060437A1 (en) | 2004-08-06 |

| CN1537312A (zh) | 2004-10-13 |

| KR20030085084A (ko) | 2003-11-01 |

| ATE329354T1 (de) | 2006-06-15 |

| EP1374250B1 (en) | 2006-06-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| KR950001133B1 (ko) | 스태틱형 반도체 기억장치 | |

| EP0451595B1 (en) | Short circuit detector circuit for memory array | |

| CN1700356B (zh) | 半导体存储器 | |

| EP0543408B1 (en) | Semiconductor memory and screening test method thereof | |

| US7298655B2 (en) | Isolation control circuit and method for a memory device | |

| KR19980024153A (ko) | 테스트 대상의 반도체 메모리 회로를 구비한 반도체 장치, 반도체 메모리 회로의 테스트 방법 및 반도체 메모리 회로의 판독회로 | |

| JPH01166391A (ja) | スタティック型ランダムアクセスメモリ | |

| KR940022582A (ko) | 병렬비트테스트모드내장 반도체 메모리 | |

| US5519712A (en) | Current mode test circuit for SRAM | |

| CN100538910C (zh) | 测试存储单元的装置和方法 | |

| JPH04230049A (ja) | 半導体装置 | |

| US6731561B2 (en) | Semiconductor memory and method of testing semiconductor memory | |

| US5896395A (en) | Integrated circuit memory devices and operating methods including temporary data path width override | |

| JPH0854446A (ja) | 半導体記憶装置用マルチビットテスト回路 | |

| CN114236366A (zh) | 支持乱序成品测试的芯片及测试方法 | |

| KR100300873B1 (ko) | 강유전체 커패시터를 사용한 반도체 메모리 장치의 리던던시 회로 및 수리 방법 | |

| US20040130952A1 (en) | Circuit and method for transforming data input/output format in parallel bit test | |

| US5684748A (en) | Circuit for testing reliability of chip and semiconductor memory device having the circuit | |

| US6600684B2 (en) | Semiconductor storage device | |

| KR20040107592A (ko) | 반도체 장치 및 그 테스트 방법 | |

| US10650909B2 (en) | Testing method for reading current of static random access memory | |

| KR19980069836A (ko) | 반도체 기억장치 | |

| US6519177B1 (en) | Circuits and methods for initializing memory cells | |

| US6392940B2 (en) | Semiconductor memory circuit | |

| KR0164397B1 (ko) | 데이타 변경회로를 구비한 반도체 메모리장치의 멀티 비트 테스트 회로 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| C17 | Cessation of patent right | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20090909 Termination date: 20100308 |