CN101425328B - 半导体器件 - Google Patents

半导体器件 Download PDFInfo

- Publication number

- CN101425328B CN101425328B CN2008101838307A CN200810183830A CN101425328B CN 101425328 B CN101425328 B CN 101425328B CN 2008101838307 A CN2008101838307 A CN 2008101838307A CN 200810183830 A CN200810183830 A CN 200810183830A CN 101425328 B CN101425328 B CN 101425328B

- Authority

- CN

- China

- Prior art keywords

- mentioned

- electric current

- bit line

- current

- magnetoresistance element

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/14—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using thin-film elements

- G11C11/15—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using thin-film elements using multiple magnetic layers

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1653—Address circuits or decoders

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1653—Address circuits or decoders

- G11C11/1657—Word-line or row circuits

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1659—Cell access

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1673—Reading or sensing circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1675—Writing or programming circuits or methods

-

- G—PHYSICS

- G11—INFORMATION STORAGE

- G11C—STATIC STORES

- G11C11/00—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor

- G11C11/02—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements

- G11C11/16—Digital stores characterised by the use of particular electric or magnetic storage elements; Storage elements therefor using magnetic elements using elements in which the storage effect is based on magnetic spin effect

- G11C11/165—Auxiliary circuits

- G11C11/1693—Timing circuits or methods

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B61/00—Magnetic memory devices, e.g. magnetoresistive RAM [MRAM] devices

- H10B61/20—Magnetic memory devices, e.g. magnetoresistive RAM [MRAM] devices comprising components having three or more electrodes, e.g. transistors

- H10B61/22—Magnetic memory devices, e.g. magnetoresistive RAM [MRAM] devices comprising components having three or more electrodes, e.g. transistors of the field-effect transistor [FET] type

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N—ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10N50/00—Galvanomagnetic devices

- H10N50/10—Magnetoresistive devices

Abstract

本发明提供一种半导体器件,在利用自旋注入磁化反转的存储器中,实现高速动作时的低电流重写动作,抑制每个存储器单元的离差,并抑制读出干扰。在进行重写前,提供弱脉冲,使自旋状态不稳定,降低重写电流。利用重写电流在脉冲宽度中非线性地增大的区域进行读出,对干扰进行抑制。进而,通过利用位线电荷使注入自旋量恒定的驱动方法来抑制离差。

Description

本申请是申请日为2007年2月27日、申请号为200710084807.8、发明名称为“半导体器件”的发明专利申请的分案申请。

技术领域

本发明涉及半导体器件,尤其涉及利用磁阻变化的存储器单元的写入控制方法。

背景技术

在非易失性存储器中,利用磁阻变化的MRAM(MagnetoresistiveRandom Access Memory)有作为可高速动作的RAM的可能性。现有的MRAM的单元结构,由1个隧道磁阻元件TMR和用于读出的选择晶体管MCT、写入字线WWL、位线BL、以及源极线SL构成。如图30所示,在隧道磁阻元件TMR中,至少有2层磁性层,其中,一层由自旋方向固定的固定层PL构成,另一层由自旋方向相对于固定层呈平行状态和反平行状态这2个状态的自由层FL构成。利用该自由层的自旋方向进行信息存储,在反平行状态,隧道磁阻元件的电阻为高阻抗状态,在平行状态,隧道磁阻元件的电阻为低阻抗状态。在读出动作中,读出隧道磁阻元件TMR的电阻大小。而在重写动作中,使电流流过写入的字线WWL和位线BL,此时,由在隧道磁阻元件TMR中激励的合成磁场控制自由层的自旋方向。但是,在该重写方式中,随着隧道磁阻元件TMR的微细化,重写所需的磁场强度变大,因此存在流过写入的字线和位线的电流也变大的问题。针对该问题,在非专利文献1中公开了一种MRAM(Spin RAM),该MRAM利用了通过使电流垂直地流过上述的隧道磁阻元件TMR来改变自由层的自旋方向的自旋注入磁化反转技术。上述重写方式,如图31所示,能够利用与固定层、隧道膜、自由层垂直的方向的电流来控制自由层的自旋方向。因此,由于重写所需的电流与隧道磁阻元件TMR的尺寸成比例,所以能够随着隧道磁阻元件TMR的微细化降低重写电流,在可扩缩性方面是优异的。

专利文献1:日本特开2005-116923号公报

非专利文献1:2005 International Electron Device MeetingTechnical Digest Papers pp.473-476

发明内容

在自旋注入型MRAM中,当前重写所需的电流密度(阈值电流)需要满足1×106~107A/cm2,在用50nm×100nm的元件考虑此条件的情况下,需要50μA的电流,这是与最小加工尺寸的MOS晶体管能够驱动的电流相等的水平。

另外,发明人在研究中发现,该重写所需的电流密度(阈值电流)是写入时间(重写脉冲宽度)的函数,即,若要以短写入时间充分地使自旋方向反转就需要很大的电流。也就是说,当为自旋注入型MRAM时,可扩缩性优异,且高速写入性能优良,但在高速地进行写入时,需要用于流过大电流的大MOS晶体管,相反地,在为了减小面积而使用小MOS晶体管时,则无法高速地进行写入。

另外,自旋注入型MRAM,可扩缩性优异,能够进行微细化。但是,若进行微细化,则每个存储器单元的制造离差变大,写入电流会在每个存储器单元上产生离差。因此,在写入时需要降低流过存储器单元的电流的离差。

进而,在自旋注入型MRAM中,写入与读出的差别仅是流过的电流量不同。因此,存在因读出导致的误写入的隐患。为避免上述隐患需要降低读出干扰。

为了解决上述问题,本申请的说明书所公开的主要发明如下。

第一,在自旋注入型MRAM的写入动作时,使第一电流流过隧道磁阻元件后,使比第一电流大的第二电流流过。

第二,在自旋注入型MRAM的读出时,使电流流过存储器单元的时间比重写动作的时间短,电流值为相同程度。

第三,在自旋注入型MRAM的写入动作时,流过对电容进行充电的电荷。

第四,在自旋注入型MRAM的写入动作时,使用写入辅助线来产生磁场,对隧道磁阻元件产生影响。

第五,在自旋注入型MRAM的写入动作前,使电流流过位线来产生磁场,对隧道磁阻元件产生影响。

本发明的效果是能够实现高速写入或稳定动作。

附图说明

图1是本发明的第一实施例。

图2是本发明的第一实施例的动作例。

图3是采用了本发明的第一实施例时的实验结果。

图4是实现第一实施例时的存储器阵列的结构例。

图5是图4的位线·源极线选择电路的结构例。

图6是图4的读出放大器·写入电路的结构例。

图7是图4的字驱动器的结构例。

图8是图4至图7的电路动作波形图。

图9是图6的读出放大器·写入电路的其它结构例。

图10是图6的读出放大器·写入电路的其它结构例。

图11是图10所示的电路的动作波形图。

图12是本发明的第二实施例。

图13是采用了本发明的第二实施例时的实验结果。

图14是本发明的第二实施例的其它结构例。

图15是本发明的第二实施例的其它结构例。

图16是图15的结构例的动作例。

图17是本发明的第三实施例。

图18是本发明的第三实施例的动作例。

图19是本发明的第三实施例的其它结构例。

图20是图19的结构例的动作例。

图21是本发明的第三实施例的其它结构例。

图22是图21的结构例的动作例。

图23是实现本发明的实施例的存储器单元阵列的布局例。

图24是图23的A-A’间的剖面图和外围电路的剖面图。

图25是图23的B-B’间的剖面图和C-C’间的剖面图。

图26是表示了本发明的第4实施例的存储器阵列的布局例。

图27是对应于图26的剖面结构的存储器单元的电路图。

图28是本发明的第4实施例的其它结构例。

图29是图28的结构例的动作例。

图30是隧道磁阻元件TMR的结构例。

图31是自由层的自旋方向控制的说明图。

具体实施方式

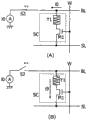

使用图1和图2说明本发明的第一实施例。本结构的存储器单元SC,由n型MOS晶体管M1和隧道磁阻元件T1构成,如图1所示那样连接在位线BL和源极线SL上,控制M1栅极的是字线W。隧道磁阻元件T1,如已经在图30中作为TMR说明的那样,至少具有2层磁性层,其中,一层由自旋方向固定的固定层PL构成,另一层由使自旋方向相对于固定层取为平行状态、反平行状态这2种状态的自由层FL构成。利用该自由层的自旋的方向进行信息存储,隧道磁阻元件的电阻抗在反平行状态下为高阻抗状态,在平行状态下为低阻抗状态。当选择字线时,在T1和M1中,如果BL侧比SL侧电位高则电流沿着图1中的i方向流过,如果SL侧比BL侧电位高则电流沿相反方向流过。与此对应,如已经在图31中说明的那样,能够控制自旋的方向,并能够写入与此相对应的信息。

图2的(A)表示本结构的特征。取横轴为时间来示出电流i的值。即,非选择时的电流值为i0(例如,取电流为0μA),最初的时间t1的电流值为i1,之后时间t2的电流值为i2,i1具有比i2小的特征。在本说明书中,将提供最初的弱电流i1的动作称为前脉冲。与此相比较,在不提供前脉冲的情况下,如图2的(B)所示,当在重写动作时间t3的期间流过恒定的电流i3时,该i3变为比i2大的值。另外,如图2的(C)所示,即使流过的电流与i2相同,重写动作时间t4也会比t2长。作为引起这种现象的原因,考虑是由最初的弱电流i1使自由层的自旋发生扰动,导致成为方向容易改变的状态。因此,与一次性地流过重写电流相比,预先用最初的弱电流做成为容易改变自旋的状态、之后使原本的重写电流流过,能够实现更小的重写电流。图3表示使用了本发明时的实验结果的示意图。横轴表示重写时间,纵轴表示重写所需的电流,为了分别用所希望的点进行标准化,单位是任意的。如该图3所示,通过如图2的(A)所示那样在最初提供弱电流(具有前脉冲),能够用更短的时间进行重写。

如上所述,采用在最初提供弱电流i1,之后提供比该电流大的电流i2(图2(A))的方法,能够用更低的电流进行重写,另外,能够实现高速重写动作。在前脉冲动作之后,若不流过原本的用于重写动作的电流,存储器单元的状态会返回最初的状态,不会成为其它的状态。另外,可以仅对重写的存储器单元提供前脉冲,也可以包括不重写的单元而同时提供前脉冲。

图4表示使用了本发明申请的存储器阵列。存储器单元SC由字驱动器WD控制,字线为W1、W2,各个存储器单元由MT和隧道磁阻元件TMR构成,如图所示那样地连接在位线BL和源极线SL上。在图4中,存储器单元SC配置在字线与位线的一半交点上,但也可以配置在全部交点上。读出放大器块SAB配置有位线·源极线选择电路BLSEL、放大位线的微弱信号的读出放大器SA、以及用于对存储器单元写入数据的写入电路WA。在图4中,示出了对1个读出放大器·写入电路连接有4对位线·源极线对的例子,但不限于此。也可以对1对位线·源极线对连接读出放大器·写入电路。在该情况下,面积增大,但由于对全部位线连接读出放大器,因此有利于一次向外部输出大量数据。另外,若对4对、8对或16对等多个位线·源极线对配置1个读出放大器·写入电路,则将使读出放大器·写入电路的数量减少,因而具有能够减少小面积的优点。

图5是根据位线选择信号SEL0、SEL1、SEL2、SEL3从4对位线·源极线对中选择1对位线·源极线对的位线·源极线选择电路例子。在该电路中还包括补偿MOS和预充电电路,该补偿MOS用于根据补偿信号EQ0、EQ1、EQ2、EQ3和预充电信号PC0、PC1、PC2、PC3而在非选择时将位线和源极线的电位设定为预定电压Vs,上述预充电电路用于根据读出放大器预充电信号PCSA在读出时将位线和源极线的电位设定为预定读出电压(VR)。本电路并不限于图5所示的结构。只要具有同样的功能,也可以是其它电路结构。

图6表示图4所示的读出放大器SA和写入电路WA的结构例。采用图6所示出的结构能够实现面积的减小。写入电路,首先具有锁存电路,该锁存电路由将LTP和LTA作为输出的2级反相器电路构成。由列选择信号Y1和第一写入控制信号WE根据输入输出线IO的信息来设定该锁存电路中的信息。由该设定结果的LTP和LTA的值,并由第二写入控制信号WE1,使连接在此处的MOS晶体管导通,则位线BLSA和源极线SLSA与Vd或Vs电连接。另外,由位线·源极线选择电路BLSEL所选择的位线BL、源极线SL也与Vd或VS电连接。位线BLSA、源极线SLSA与位线BL、源极线SL相同地进行控制,因此为了防止以下的说明变得复杂,只要没有特别说明,位线BLSA和位线BL作为相同线处理,源极线SLSA和SL作为相同线处理。此时,位线BL与Vd电连接时,LTP是高电位,LTA是低电位,源极线SL与Vs电连接。为了对位线、源极线可靠地提供Vd,预先设定锁存电路的电位比Vd高。读出时,能够由读出控制电路RE1、RE将位线BL的信号送入读出放大器进行放大,或者将读出放大器的信号通过由列选择信号Y1所控制的MOS晶体管输出至IO。通过采用该图6的电路结构,能够进行在图1~图3中所说明的本发明的动作。

图7是图4所示的字驱动器WD的电路例子。图7的字驱动器WD表示用于通过控制字线来实现前脉冲的结构。这里,该字驱动器是通过由例示出Ai1和Ai2这二者的外部地址所选择的信号(译码信号)来选择字线W1和W2的电路,此时,能够通过切换HW来对字线提供两种电压,上述两种电压分别是电压值比Vd1少了nMOS的阈值量的电压和电压值等于Vd1的电压。即,在非选择状态,Ai1、Ai2及HW为高电平,因此字线为Vs电平。在此,当Ai1被选择而成为低电平时,利用接收了该低电平的反相器的输出,插入在Vd1和W1之间的nMOS的栅极电压成为Vd1。因此,在字线输出电压值比Vd1低了nMOS的阈值量的电压。接着,HW也成为低电平,则插入在Vd1和W1之间的串联的2个pMOS的栅极成为低电平,在字线输出电压值等于Vd1的电压。根据该例子,能够发生2种电压,能够实现本发明所需的流过2种电流值的电流的动作。

图8表示图4~图7的电路的动作例。是从IO取入重写数据,利用本发明的方法进行重写的动作。IO为初始低电压,作为重写数据取为高电位。通过将Y1和WE置为高电位将其锁存地读入。结果LTP由低电位切换为高电位,LTA由高电位切换为低电位。预充电信号PC和补偿信号EQ此时为高电位,因此位线BL和源极线SL都为低电位Vs。如果切换WE1,源极线SL成为能够与高电位Vd电连接的状态,位线BL成为能够与低电位Vs电连接的状态。接着,PC和EQ成为低电位,位线BL和源极线SL从低电位Vs电切换出来。之后,WE1成为高电位,源极线SL电连接高电位Vd,位线BL与低电位Vs电连接。此时,译码信号Ai1被切换,字驱动器WD1进行动作,字线W1首先成为V1电位(前脉冲动作)。该V1的值,如图7的电路图所示,为电压值比Vd1低了MOS的阈值量的电压。由此,使对应图2的小电流i1流过存储器单元。因此,存储器单元中的自旋成为容易改变方向的状态。之后,信号线HW被切换。这样,如图7的电路图所示,由电压Vd1经由pMOS对字线施加电压,字线W1成为比V2(=Vd1)高的电压。使比对应图2电流大的重写电流即i2流过存储器单元。由此,存储器单元中的自旋成为朝向所希望的方向,能够进行重写动作。此时,最初对字线提供V1之后提供V2的动作,与一次性地对字线提供用于重写动作的电压的情况相比,能够使V2变低或者使提供的时间缩短(即,能够进行高速重写)。这样,本发明能够降低重写电流,进行重写的高速化。当重写结束时,使字线返回最初的低电位,将WE1置为低电位,将PC置为高电位。因此,位线BL和源极线SL都为低电位Vs。

图9表示实现本发明时的写入电路的其它结构。与图6的差别在于:由差动信号(互补信号线)构成输入输出线;连接Vd、位线BL以及源极线SL的MOS晶体管为p型MOS晶体管。首先,采用差动信号能够进行高速且稳定的读出。另外,采用p型MOS晶体管具有锁存的电源电压即使为Vd也能够将Vd的电位提供给位线BL或源极线SL的特征。

具体而言,为了将输入输出线IO取为差动信号,输入输出线为IO和IOB这2条,在此信号线上表现差动信号。为此,第一写入控制信号WE和读出控制信号RE控制2个MOS晶体管。另外,读出放大器两端的输出经由用RE控制的MOS晶体管与输入输出线IO和IOB连接。另外,为了使连接Vd和位线BL或源极线SL的MOS晶体管为p型MOS晶体管,作为锁存电路的输出LTP和LTA,如上所述,输入到连接Vd和位线BL或源极线SL的p型晶体管的栅极。另外,第二写入控制信号也为两种,分别是WE1和与WE1相位相反的信号输出WE1B,由WE1B控制用于连接Vd和位线BL或源极线SL的另一p型晶体管。动作与图5相比仅具有以下不同点:成为差动的输入输出线IO和IOB;在WE1的基础上添加与WE1相位相反的信号输出WE1B;锁存电路的输出的高电位可以为Vd电位。在本实施例中,说明了使输入输出信号线IO成为差动信号线和使连接Vd和位线BL或源极线SL的MOS晶体管为p型MOS晶体管这两者,不言而喻,当然也可以仅选择合适的一者。

图10表示实现本发明时的写入电路的其它结构例。该电路的特征在于,不用字线电压进行前脉冲的动作,而用位线BL和源极线SL进行前脉冲的动作。因此,字线不用采用在图8中进行了说明的有2种高电位的结构,如后面所述,高电位可以为1种。因此,字驱动器WD也不用采用图7所示的电路,而能够使用通常的字驱动器WD。为了通过驱动位线、源极线实现前脉冲动作,在图10所示的电路中,能够对位线BL和源极线SL施加Vd和Vd2这2种高电位。此时,Vd2为比Vd1低的电位。在前脉冲动作时,使用该Vd2,在其后的重写动作时使用Vd。因此,如图10所示,Vd2和位线B1或源极线SL成为响应锁存电路的输出,利用WE1信号进行电连接的结构,并且Vd和位线BL或源极线SL成为响应锁存电路的输出,利用WE2信号进行电连接的结构。

图11表示图10所示的电路的动作例。与图6所示的动作的不同点在于,在此例子中,使用WE1信号进行控制,在源极线SL表现第一高电位,之后用WE2信号进行控制,在源极线SL表现第二高电位。通过由第一高电位产生的电流而使自旋的方向容易变化,通过由第二高电位产生的电流而使该自旋的方向容易反转。本例子是以在源极线SL上表现这样的电位作为例子的,但也有在位线BL上表现这样的电流的例子。这是由于如图31所说明的那样,在重写时根据要写入的信息而具有2个方向的缘故。该电路的动作如下所述。通过进行这样的动作,能够做成自旋方向容易变化的状态,因此能够实现重写电流的降低和重写时间的缩短,实现低功耗和高速化。

使用图12说明本发明的第二实施例。在读出动作和写入动作时,观察在存储器单元中流过的电流和其脉冲宽度。本发明的特征是读出和写入的电流量几乎相等,读出时的脉冲宽度比写入时小。即,电流值都等于i4,读出时的脉冲宽度t5与写入时的t6相比,t5小于t6。将此与闪速存储器相比,例如NAND型闪速存储器,每个存储器单元的写入电流比读出电流小,另外,所需的脉冲宽度在写入时比读出时大。利用电流在布线上产生磁场进行重写的MRAM,写入时的电流大。与这些例子不同,本发明进行具有如图12所示的特征的读出和写入。发明人发现这样能够大大地降低读出时的干扰。发现这是与通过缩短读出时的脉冲宽度,利用其施加时间而一般性地降低干扰完全不同的原理。用图13说明该原理。

图13表示使用了本发明的第二实施例时的实验结果的示意图。横轴取为重写时间,纵轴表示重写所需的电流。另外,与图3同样地分别用所希望的点进行标准化。这里,所谓读出干扰是指在读出动作中,引起弱重写动作,导致写入的数据变化的现象。如该图所示,当使重写时间逐渐缩短时,重写所需的电流逐渐增加。重写所需的电流的增加不利于用低电流进行重写,这表示相同的重写电流难以引起写入。例如,尝试用i4这样的电流值观察。此时,如果取重写时间为t6,则该电流比重写所需的电流足够大,因此能够可靠地进行重写。通常,不会用重写所需的最低限度的电流进行重写。这是由于在存储器单元中所具有的大量的自旋中,会残留没有变为重写所需要的方向的自旋。另一方面,此时,尝试将重写时间取为t5来进行观察。此时,i4这样的电流值比重写所需的电流足够小。这意味着即使流过该电流也不能引起重写。而利用该区域内的电流能够读取存储器单元的信息。即,如图30所述,利用自由层的自旋的方向,能够使隧道磁阻元件的电阻不同,能够读取该电阻的大小。此时,如上所述,该区域内的电流难以引起写入动作。由此,即使反复进行读出也难以引起干扰。根据利用了这种特征的本发明,若结合图12再次进行叙述,则能够利用在读出和重写中相同的电流值i4,仅改变其脉冲宽度地进行读出和重写。这样,在重写时和读出时,存储器单元施加的电压也可以相同,能够采用简单的电路结构,能够实现低成本的半导体存储器件。

图14是本发明的第二实施例的其它结构例。这里,在读出和写入中,最大电流i4的值几乎相等,但在写入中,还使用前脉冲动作。因此,能够使i4成为更小的值,能够缩短重写时间t7。与此相对应,能够选择读出的脉冲宽度t5和公共电流i4,实现低功耗化和高速化。图14示出电流值,但在写入时和读出时,能够通过在位线施加相同的电压来实现。

图15是用短的读出时间高速地放大信号的结构的一个例子。在位线BL上连接有读出放大器和由RE1控制的MOS晶体管,通过由PC1控制的MOS晶体管将位线BL连接至Vs,通过由PP1控制的MOS晶体管将与读出放大器的连接节点NS连接至Vd。此处的特征在于,NS的电压由PP1的信号而变为Vd,从而位线BL的电压被嵌位在比RE1的电压低了MOS晶体管的阈值电压量的电压。因此,当使存储器单元导通时,寄生电容比BL小的NS的电位高速地变化。因此,能够用读出放大器直接地放大该信号,可以使存储器单元断开。这样,能够缩短预先使存储器单元导通的时间。如上所示,流过的时间越短写入所需的电流越大,因此作为其结果,将大大提高读出动作中的抗干扰性。使用本结构,用难以引起干扰的短暂的读出时间,以读出放大器进行放大也能够得到足够的信号电压。对于源极线SL也可以具备同样的结构。如上所述,通过采用本实施例的电路结构,用PP1控制的MOS晶体管成为所谓的源极浮置模式,对于位线BL的电压变化使连接节点NS的电压高速地变化。由此能够进行高速的读出动作。

图16是表示图15的电路的动作例子的图。PC1由高电位成为低电位,之后,PP1成为低电位,则NS电连接至Vd。在此状态下,RE1成为高电位,通过在栅极上连接了RE1的n型MOS晶体管,位线BL预充电至比RE1的电压低了该n型MOS晶体管的阈值电压量的电压。这里,当选择字线W时,使电流流过存储器单元。但是,位线被嵌位在比RE1的电位低了上述n型MOS晶体管的阈值电压量的电压。该结果,NS的寄生电容远小于位线BL的寄生电容,因此NS的电位变大。其结果,能导通读出放大器,在此之前使RE1返回低电压,另外,能够关闭字线。由此,能够缩短电流流过存储器单元的时间。另外,本结构与将位线的大寄生电容直接放电的情况相比,能够高速地进行动作。

图17是表示本发明的第三实施例的图。在该实施例中,为了提供对位线BL的电位,准备了电容CS、用于将该电容与电源Vd连接的开关S1、以及用于将电容与位线BL连接的开关S2。即,至此的结构是为了对位线BL提供电位而用开关连接电源Vd、位线BL的结构。这样,当与电源直接连接时,由于构成存储器单元的MOS晶体管的性能等原因,流过的电流随每个存储器单元的不同而出现离差。本实施例与此不同,最初闭合开关S1,用Vd为电容CS充电。之后,断开开关S1,闭合开关S2,由电容CS电荷为位线BL提供电流。采用此种结构,因为仅使用由电容CS所存储的恒定的电荷,所以利用位线在存储器单元中流过的电流的总量、电荷的离差变小。通过该流过的电荷的自旋,存储器单元中的状态发生变化,成为电流源的恒定的电荷量与每个存储器单元的自旋的变化量相一致。因此,通过采用本实施例,能实现离差小的重写之后的状态。通过对源极线SL也形成相同的结构,改变重写电流的方向,能够重写所需要的信息。电容C能够用MOS电容和MIM电容形成。

图18表示图17的电路的动作例。最初,开关S1和开关S2都断开(打开)。首先,开关S1闭合。由此,虽未图示,但图17的电容CS开始充电。结束后,开关S1断开,然后开关S2闭合。由此,利用电容CS而流过电流i5。在此图中,示意性地标注为恒定的电流值,但这段时间内的总电荷量会影响重写后的状态。在本实施例中,因为在电容CS充完电的值返回原来的状态,所以在重写时,在存储器单元中流过的总电荷量的离差变小。

图19是表示本发明的第三实施例的其它的结构例子的图。在此结构例子中,准备CS1和CS2这两种电容。用开关S1对两种电容预充电至Vd。CS1经由S2连接在位线BL,CS2经由S3连接在位线BL。采用该结构,能够进行前脉冲动作,另外,能够使CS1电容变化来实现用于使此时的自旋方向容易变化的电流。另外,在重写时,因为对电容CS1和CS2充电的电荷返回原来的值,所以离差变小。为了进行前脉冲动作,C1的电容值比C2的电容值小。

图20是表示图19的电路的动作例子的图,并且,用S1对CS1和CS2进行预充电,用S2和S3使存储器单元与这些电容连接,使电流流过存储器单元。S2的脉冲宽度比S3的脉冲宽度小。由此,能够在存储器单元中提供前脉冲动作,能够变为容易改变自旋方向的状态。然后,利用S3提供重写电流(电荷)。闭合开关S2后,在开关S2断开前,闭合开关S3,则电容CS1和电容CS2暂时性地同时成为负载,因此存储器单元耗尽电荷的动作延迟。因此,当进行控制使得前脉冲和重写脉冲不发生重叠时,电容CS1不成为负载,因此存储器单元能高速地耗尽电容CS2的电荷。因此,在图20中,前脉冲和重写脉冲不连续。但是,如果缩短它们的间隔时间(数ns左右),能够充分地得到前脉冲的效果。也可以控制开关S2、S3使得前脉冲和重写脉冲连续。在该情况下,能够最大限度地实现用前脉冲扰动自旋的效果。当在写入过程中断开开关S2时,则会在电容CS1中残留一部分蓄积在电容CS2中的电荷,因此在使前脉冲和重写脉冲连续的情况下,最好是在写入结束之后再断开开关S2。

图21是表示本发明的第三实施例的其它结构例子的图。该例子的特征在于,由位线BL和源极线SL的寄生电容CB1、CB2构成在图17中说明过的CS。另外,为了实现在该寄生电容进行预充电的动作,设置用WEP控制的MOS晶体管。由WED控制,将位线BL或源极线SL的电位放电至Vs。由此,不需要形成MOS电容和MIM电容,能够减小面积。在还使用前脉冲动作的情况下,使用寄生电容形成电容CS1,使用MOS电容和MIM电容形成CS2即可。该情况下,开关仅为连接图19的位线和电容的开关S3,因此能够连续进行前脉冲动作和写入动作,最大程度地实现由前脉冲扰动自旋的效果。

图22表示图21的结构例的动作例。进行与至此说明过的动作相同的动作后,WEP成为高电位。由此根据写入数据,所指定的SL被充电。此时,该SL具有寄生电容。然后,使WEP返回到低电位,选择字线,并使WED为高电位。由此,使蓄积在源极线SL的寄生电容中的电荷流过存储器单元。利用存储器单元晶体管的性能,源极线(和位线)的电容的离差小,因此能在存储器单元中流过恒定的电荷。

图23是实现本发明的实施例的存储器单元阵列的布局例。在设字线或位线的布线节距为2F情况下,存储器单元的面积为8F2。另外,图24表示图23的A-A’间的剖面图和外围电路的剖面图。图25是图23的B-B’间的剖面图和C-C’间的剖面图。存储器单元MC由1个nMOS晶体管和隧道磁阻TMR构成。字线WL连接在晶体管的栅极GP上。栅极材料是P型多晶硅或者是在P型多晶硅的上部层叠硅化物或钨(W),形成低电阻化。存储器单元晶体管形成在P型半导体区域pWEL中。P型半导体区域pWEL形成在n型半导体区域DWEL中,该DWEL形成在P-Sub上。在nMOS晶体管的扩散层LN的一侧配置源极线触点SLC。源极线触点与相邻的存储器单元MC共用来实现小面积化。在源极线触点上沿与字线垂直的方向配置源极线。在未配置源极触点的扩散层LP上配置与隧道磁阻TMR连接的下部电极触点BEC。下部电极触点BEC连接在用于配置隧道磁阻的下部电极BE上。在下部电极BE上,配置由多个磁性体膜和隧道膜构成的隧道磁阻TMR。隧道磁阻TMR至少具有1层隧道膜TB和配置在其两侧的固定层PL、自由层FL。在磁性体的固定层PL中内部电子的自旋方向被固定为恒定方向。而在磁性体的自由层FL中,内部电子的自旋方向相对于固定层为平行、反平行状态这2种状态中的任一状态。在本结构中,在隧道膜TB和下部电极间配置固定层PL,在隧道磁阻TMR的上层布线的位线BL和隧道膜TB之间配置自由层FL。与字线垂直、与源极线平行地布置位线。隧道磁阻TMR,其位线布置方向与字线布置方向相比,呈较长的长方形或椭圆形。由此,通过做成长宽比不同的形状,具有以下的优点:能够表现出磁异向性,就是说使自由层的磁化难以在该自由层相对于固定层PL呈平行、反平行状态之外的方向进行,并且,自由层FL的自旋方向的保持特性优良。

图26是示出本发明的第4实施例的存储器阵列的布局例。仅表示对应图24的部分。本实施例的特征是在下部电极BE的下方配置与字线平行地进行布置的辅助字线AW。能够通过使电流流过该辅助字线AW来产生磁场,能够对TMR元件的动作产生影响。

图27是对应图26的剖面结构的存储器单元的电路图。字线W和辅助字线AW平行地配置,用箭头表示能够由使电流流过辅助字线AW而产生的磁场对TMR元件T1产生影响。用(A)和(B)表示作为此动作的例子。即,最初如(A)所示,仅使辅助字线导通来使电流流过。因此,通过实际产生的磁场,能够将T1内部的自旋方向做成容易改变的状态。接着,在(B)的动作中,使字线W导通,使重写电流流过。因为已经通过辅助字线AW的动作使自旋变得容易反转,所以能够用更小的电流进行重写。仅使电流流过辅助字线,自旋成为容易反转的状态,但会立即返回最初的状态。

这样的动作能够用非图26的结构的其它方法实现。图28表示本发明的第4实施例的其它结构例。这样,在位线BL和电流源i0之间设置开关S2即可。图29示出该动作。首先,如(A)所示,闭合开关S2,流过电流i0。由此,在位线BL产生磁场。根据图24的剖面图,位线BL连接在TMR元件上地进行配置。由此,根据该磁场,TMR元件受到影响,自旋变得容易反转。接着,如(B)所示,断开开关S2,通过激活字线W来流过重写电流i9。通过(A)的动作自旋变得容易反转,因此,能够用更小的电流进行重写。如果(A)的动作之后仅断开了开关2,则TMR元件直接返回到原来的状态。

以上,基于上述实施例对本发明进行了说明,但在不脱离本发明的主旨的范围内可以进行各种变更。

Claims (3)

1.一种半导体器件,其特征在于:

包括多条字线;多条位线,配置在与上述字线交叉的方向上;以及多个存储器单元,配置在上述字线和上述位线的预定的交点上,

上述多个存储器单元的每一个,包括隧道磁阻元件,该隧道磁阻元件层叠有固定层、隧道膜及自由层;和MOSFET,它的栅极连接在上述字线上,它的漏极连接在上述隧道磁阻元件的一端上,

上述固定层,邻接上述隧道膜地配置,该固定层的电子自旋的方向被固定在预定方向,

上述自由层,邻接上述隧道膜的一个面,该面为与上述隧道膜的邻接上述固定层的面相对的面,该自由层的电子自旋的方向相对于上述固定层取平行、反平行中的任一方向,

上述自由层的电子自旋,利用自旋注入磁化反转来写入信息,

在进行上述写入动作时,使第一电流流过上述隧道磁阻元件中后,使比上述第一电流大的第二电流流过。

2.根据权利要求1所述的半导体器件,其特征在于:

施加于在上述隧道磁阻元件中流过上述第一电流时的字线上的电压,比施加于在上述隧道磁阻元件中流过上述第二电流时的字线上的电压小。

3.根据权利要求1所述的半导体器件,其特征在于:

施加于在上述隧道磁阻元件中流过上述第一电流时的位线上的电压,比施加于在上述隧道磁阻元件中流过上述第二电流时的位线上的电压小。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP138429/2006 | 2006-05-18 | ||

| JP2006138429A JP4935183B2 (ja) | 2006-05-18 | 2006-05-18 | 半導体装置 |

Related Parent Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200710084807.8A Division CN101075628B (zh) | 2006-05-18 | 2007-02-27 | 半导体器件 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN101425328A CN101425328A (zh) | 2009-05-06 |

| CN101425328B true CN101425328B (zh) | 2011-11-30 |

Family

ID=38821767

Family Applications (2)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN2008101838307A Expired - Fee Related CN101425328B (zh) | 2006-05-18 | 2007-02-27 | 半导体器件 |

| CN200710084807.8A Expired - Fee Related CN101075628B (zh) | 2006-05-18 | 2007-02-27 | 半导体器件 |

Family Applications After (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN200710084807.8A Expired - Fee Related CN101075628B (zh) | 2006-05-18 | 2007-02-27 | 半导体器件 |

Country Status (5)

| Country | Link |

|---|---|

| US (2) | US7596014B2 (zh) |

| JP (1) | JP4935183B2 (zh) |

| KR (1) | KR101263048B1 (zh) |

| CN (2) | CN101425328B (zh) |

| TW (1) | TWI433147B (zh) |

Families Citing this family (33)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7646627B2 (en) * | 2006-05-18 | 2010-01-12 | Renesas Technology Corp. | Magnetic random access memory having improved read disturb suppression and thermal disturbance resistance |

| JP4250644B2 (ja) | 2006-08-21 | 2009-04-08 | 株式会社東芝 | 磁気記憶素子およびこの磁気記憶素子を備えた磁気メモリならびに磁気メモリの駆動方法 |

| JP5096886B2 (ja) * | 2007-11-20 | 2012-12-12 | シャープ株式会社 | 不揮発性半導体記憶装置及びその駆動方法 |

| JP5224803B2 (ja) | 2007-12-26 | 2013-07-03 | 株式会社日立製作所 | 磁気メモリ及び磁気メモリの書き込み方法 |

| JP2009211733A (ja) * | 2008-02-29 | 2009-09-17 | Toshiba Corp | 磁気記憶装置 |

| JP2009230798A (ja) * | 2008-03-21 | 2009-10-08 | Toshiba Corp | 磁気記憶装置 |

| TWI451410B (zh) * | 2008-04-18 | 2014-09-01 | Sony Corp | Recording method of magnetic memory element |

| KR101493868B1 (ko) * | 2008-07-10 | 2015-02-17 | 삼성전자주식회사 | 자기 메모리 소자의 구동 방법 |

| JP4738462B2 (ja) * | 2008-09-25 | 2011-08-03 | 株式会社東芝 | 磁気ランダムアクセスメモリ |

| US7876603B2 (en) * | 2008-09-30 | 2011-01-25 | Micron Technology, Inc. | Spin current generator for STT-MRAM or other spintronics applications |

| US7859891B2 (en) * | 2008-09-30 | 2010-12-28 | Seagate Technology Llc | Static source plane in stram |

| JP4970407B2 (ja) * | 2008-11-10 | 2012-07-04 | 株式会社東芝 | 磁気記憶素子およびこの磁気記憶素子を備えた磁気メモリならびに磁気メモリの駆動方法 |

| US8027206B2 (en) * | 2009-01-30 | 2011-09-27 | Qualcomm Incorporated | Bit line voltage control in spin transfer torque magnetoresistive random access memory |

| JP4649519B2 (ja) | 2009-03-13 | 2011-03-09 | 株式会社東芝 | 磁気ディスク装置及び磁気ヘッド駆動制御方法 |

| US7957183B2 (en) * | 2009-05-04 | 2011-06-07 | Magic Technologies, Inc. | Single bit line SMT MRAM array architecture and the programming method |

| WO2010140615A1 (ja) * | 2009-06-03 | 2010-12-09 | 株式会社日立製作所 | 半導体記憶装置 |

| JP2011034637A (ja) * | 2009-08-03 | 2011-02-17 | Toshiba Corp | 不揮発性半導体記憶装置 |

| US8385106B2 (en) * | 2009-09-11 | 2013-02-26 | Grandis, Inc. | Method and system for providing a hierarchical data path for spin transfer torque random access memory |

| JP4818426B2 (ja) | 2009-11-27 | 2011-11-16 | 株式会社東芝 | ヘッド駆動制御装置、磁気ディスク装置及びヘッド駆動制御方法 |

| WO2011101947A1 (ja) * | 2010-02-16 | 2011-08-25 | 株式会社日立製作所 | 半導体装置 |

| US8411497B2 (en) * | 2010-05-05 | 2013-04-02 | Grandis, Inc. | Method and system for providing a magnetic field aligned spin transfer torque random access memory |

| US8437181B2 (en) * | 2010-06-29 | 2013-05-07 | Magic Technologies, Inc. | Shared bit line SMT MRAM array with shunting transistors between the bit lines |

| KR20120010052A (ko) * | 2010-07-23 | 2012-02-02 | 삼성전자주식회사 | 이퀄라이징 기능을 갖는 저항성 메모리 및 이를 포함하는 3차원 반도체 장치 |

| US8929132B2 (en) * | 2011-11-17 | 2015-01-06 | Everspin Technologies, Inc. | Write driver circuit and method for writing to a spin-torque MRAM |

| US9424903B2 (en) | 2012-05-16 | 2016-08-23 | Sony Corporation | Memory apparatus and memory device |

| JP5916524B2 (ja) * | 2012-06-07 | 2016-05-11 | ルネサスエレクトロニクス株式会社 | 半導体装置 |

| JP6137180B2 (ja) * | 2012-06-26 | 2017-05-31 | 日本電気株式会社 | プログラミング回路、半導体装置及びプログラミング方法 |

| CN105074825B (zh) * | 2013-03-15 | 2019-01-08 | 英特尔公司 | 基于集成电容器的配电 |

| CN105531767B (zh) | 2013-06-28 | 2018-01-26 | 英特尔公司 | 电阻式存储器的低功率写和读操作的装置 |

| KR20170090293A (ko) | 2016-01-28 | 2017-08-07 | 삼성전자주식회사 | 분리 소스라인 구조를 갖는 메모리 장치 |

| US10109331B2 (en) | 2016-03-01 | 2018-10-23 | Toshiba Memory Corporation | Magnetic storage device with a wiring having a ferromagnetic layer |

| JP6625942B2 (ja) * | 2016-07-29 | 2019-12-25 | 株式会社東芝 | 半導体記憶装置 |

| TWI785299B (zh) | 2016-09-09 | 2022-12-01 | 日商鎧俠股份有限公司 | 記憶裝置 |

Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20020141231A1 (en) * | 2001-04-03 | 2002-10-03 | Shigeki Komori | Magnetic random-access memory |

| CN1480945A (zh) * | 2002-09-03 | 2004-03-10 | 三菱电机株式会社 | 具备磁隧道结的薄膜磁性体存储器 |

Family Cites Families (8)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP3970571B2 (ja) * | 2001-10-10 | 2007-09-05 | 独立行政法人科学技術振興機構 | 磁気記憶素子の書き込み回路 |

| JP2005116923A (ja) | 2003-10-10 | 2005-04-28 | Hitachi Ltd | スピントルクを用いた不揮発性磁気メモリセルおよびこれを用いた磁気ランダムアクセスメモリ |

| US7224601B2 (en) * | 2005-08-25 | 2007-05-29 | Grandis Inc. | Oscillating-field assisted spin torque switching of a magnetic tunnel junction memory element |

| JP2007081280A (ja) * | 2005-09-16 | 2007-03-29 | Fujitsu Ltd | 磁気抵抗効果素子及び磁気メモリ装置 |

| JP4999359B2 (ja) * | 2005-10-13 | 2012-08-15 | ルネサスエレクトロニクス株式会社 | 不揮発性記憶装置 |

| US7286395B2 (en) * | 2005-10-27 | 2007-10-23 | Grandis, Inc. | Current driven switched magnetic storage cells having improved read and write margins and magnetic memories using such cells |

| JP5193419B2 (ja) * | 2005-10-28 | 2013-05-08 | 株式会社東芝 | スピン注入磁気ランダムアクセスメモリとその書き込み方法 |

| US7430135B2 (en) * | 2005-12-23 | 2008-09-30 | Grandis Inc. | Current-switched spin-transfer magnetic devices with reduced spin-transfer switching current density |

-

2006

- 2006-05-18 JP JP2006138429A patent/JP4935183B2/ja not_active Expired - Fee Related

-

2007

- 2007-02-21 KR KR1020070017550A patent/KR101263048B1/ko not_active IP Right Cessation

- 2007-02-27 CN CN2008101838307A patent/CN101425328B/zh not_active Expired - Fee Related

- 2007-02-27 TW TW096106821A patent/TWI433147B/zh active

- 2007-02-27 CN CN200710084807.8A patent/CN101075628B/zh not_active Expired - Fee Related

- 2007-04-17 US US11/736,252 patent/US7596014B2/en not_active Expired - Fee Related

-

2009

- 2009-08-21 US US12/545,363 patent/US7778068B2/en not_active Expired - Fee Related

Patent Citations (2)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US20020141231A1 (en) * | 2001-04-03 | 2002-10-03 | Shigeki Komori | Magnetic random-access memory |

| CN1480945A (zh) * | 2002-09-03 | 2004-03-10 | 三菱电机株式会社 | 具备磁隧道结的薄膜磁性体存储器 |

Also Published As

| Publication number | Publication date |

|---|---|

| TWI433147B (zh) | 2014-04-01 |

| CN101075628B (zh) | 2014-01-08 |

| CN101075628A (zh) | 2007-11-21 |

| US7596014B2 (en) | 2009-09-29 |

| CN101425328A (zh) | 2009-05-06 |

| KR101263048B1 (ko) | 2013-05-14 |

| TW200807414A (en) | 2008-02-01 |

| US20090310399A1 (en) | 2009-12-17 |

| JP2007310949A (ja) | 2007-11-29 |

| KR20070111958A (ko) | 2007-11-22 |

| US20070285975A1 (en) | 2007-12-13 |

| JP4935183B2 (ja) | 2012-05-23 |

| US7778068B2 (en) | 2010-08-17 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN101425328B (zh) | 半导体器件 | |

| CN101075631B (zh) | 半导体器件 | |

| US7345912B2 (en) | Method and system for providing a magnetic memory structure utilizing spin transfer | |

| CN101859599B (zh) | 使用字线过度驱动和高k金属栅极提升磁性隧道结的编程电流 | |

| US8559253B2 (en) | Variable-resistance memory device with charge sharing that discharges pre-charge voltage of a selected bit line to share charge with unselected bit lines | |

| KR101038635B1 (ko) | 강화된 전류 및 강화된 전류 대칭성을 갖는 전류 구동 메모리 셀 | |

| TW508588B (en) | Semiconductor integrated circuit device | |

| KR101264518B1 (ko) | 반도체 장치 | |

| JP5221222B2 (ja) | 半導体記憶装置 | |

| US20050185474A1 (en) | Semiconductor integrated circuit | |

| CN102148055B (zh) | 使用自旋mos晶体管的非易失性存储器电路 | |

| EP1120791A1 (en) | Semiconductor device | |

| JP5227133B2 (ja) | 半導体記憶装置 | |

| CN101593551A (zh) | 半导体器件 | |

| CN100461297C (zh) | 半导体存储装置 | |

| CN107851451A (zh) | 阻变型存储器 | |

| JP5500289B2 (ja) | 半導体装置 | |

| JP5293795B2 (ja) | 半導体装置 | |

| KR100682212B1 (ko) | 불휘발성 강유전체 메모리 장치 | |

| US9911504B2 (en) | Non-volatile memory array using electromechanical switches for cell storage |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| CF01 | Termination of patent right due to non-payment of annual fee | ||

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20111130 Termination date: 20170227 |