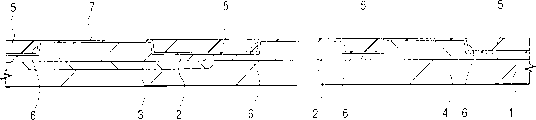

CN1210783C - 半导体集成电路器件的制造工艺 - Google Patents

半导体集成电路器件的制造工艺 Download PDFInfo

- Publication number

- CN1210783C CN1210783C CNB991183398A CN99118339A CN1210783C CN 1210783 C CN1210783 C CN 1210783C CN B991183398 A CNB991183398 A CN B991183398A CN 99118339 A CN99118339 A CN 99118339A CN 1210783 C CN1210783 C CN 1210783C

- Authority

- CN

- China

- Prior art keywords

- film

- dielectric film

- manufacturing process

- semiconductor device

- device manufacturing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Fee Related

Links

Images

Classifications

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76801—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing

- H01L21/76829—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers

- H01L21/76831—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the dielectrics, e.g. smoothing characterised by the formation of thin functional dielectric layers, e.g. dielectric etch-stop, barrier, capping or liner layers in via holes or trenches, e.g. non-conductive sidewall liners

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L27/00—Devices consisting of a plurality of semiconductor or other solid-state components formed in or on a common substrate

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76843—Barrier, adhesion or liner layers formed in openings in a dielectric

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76853—Barrier, adhesion or liner layers characterized by particular after-treatment steps

- H01L21/76855—After-treatment introducing at least one additional element into the layer

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76841—Barrier, adhesion or liner layers

- H01L21/76853—Barrier, adhesion or liner layers characterized by particular after-treatment steps

- H01L21/76855—After-treatment introducing at least one additional element into the layer

- H01L21/76856—After-treatment introducing at least one additional element into the layer by treatment in plasmas or gaseous environments, e.g. nitriding a refractory metal liner

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76838—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics characterised by the formation and the after-treatment of the conductors

- H01L21/76877—Filling of holes, grooves or trenches, e.g. vias, with conductive material

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L21/00—Processes or apparatus adapted for the manufacture or treatment of semiconductor or solid state devices or of parts thereof

- H01L21/70—Manufacture or treatment of devices consisting of a plurality of solid state components formed in or on a common substrate or of parts thereof; Manufacture of integrated circuit devices or of parts thereof

- H01L21/71—Manufacture of specific parts of devices defined in group H01L21/70

- H01L21/768—Applying interconnections to be used for carrying current between separate components within a device comprising conductors and dielectrics

- H01L21/76897—Formation of self-aligned vias or contact plugs, i.e. involving a lithographically uncritical step

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L28/00—Passive two-terminal components without a potential-jump or surface barrier for integrated circuits; Details thereof; Multistep manufacturing processes therefor

- H01L28/40—Capacitors

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/05—Making the transistor

-

- H—ELECTRICITY

- H01—ELECTRIC ELEMENTS

- H01L—SEMICONDUCTOR DEVICES NOT COVERED BY CLASS H10

- H01L2924/00—Indexing scheme for arrangements or methods for connecting or disconnecting semiconductor or solid-state bodies as covered by H01L24/00

- H01L2924/30—Technical effects

- H01L2924/301—Electrical effects

- H01L2924/3011—Impedance

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/02—Manufacture or treatment for one transistor one-capacitor [1T-1C] memory cells

- H10B12/03—Making the capacitor or connections thereto

- H10B12/033—Making the capacitor or connections thereto the capacitor extending over the transistor

- H10B12/0335—Making a connection between the transistor and the capacitor, e.g. plug

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/01—Manufacture or treatment

- H10B12/09—Manufacture or treatment with simultaneous manufacture of the peripheral circuit region and memory cells

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/31—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor

- H10B12/315—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells having a storage electrode stacked over the transistor with the capacitor higher than a bit line

-

- H—ELECTRICITY

- H10—SEMICONDUCTOR DEVICES; ELECTRIC SOLID-STATE DEVICES NOT OTHERWISE PROVIDED FOR

- H10B—ELECTRONIC MEMORY DEVICES

- H10B12/00—Dynamic random access memory [DRAM] devices

- H10B12/30—DRAM devices comprising one-transistor - one-capacitor [1T-1C] memory cells

- H10B12/48—Data lines or contacts therefor

- H10B12/485—Bit line contacts

Abstract

Description

Claims (48)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| JP246147/1998 | 1998-08-31 | ||

| JP10246147A JP2000077625A (ja) | 1998-08-31 | 1998-08-31 | 半導体集積回路装置の製造方法 |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| CN1246727A CN1246727A (zh) | 2000-03-08 |

| CN1210783C true CN1210783C (zh) | 2005-07-13 |

Family

ID=17144195

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CNB991183398A Expired - Fee Related CN1210783C (zh) | 1998-08-31 | 1999-08-31 | 半导体集成电路器件的制造工艺 |

Country Status (6)

| Country | Link |

|---|---|

| US (1) | US6235620B1 (zh) |

| JP (1) | JP2000077625A (zh) |

| KR (1) | KR100715260B1 (zh) |

| CN (1) | CN1210783C (zh) |

| SG (1) | SG75976A1 (zh) |

| TW (1) | TW451460B (zh) |

Families Citing this family (24)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6159818A (en) * | 1999-09-02 | 2000-12-12 | Micron Technology, Inc. | Method of forming a container capacitor structure |

| JP2001185552A (ja) * | 1999-12-27 | 2001-07-06 | Hitachi Ltd | 半導体集積回路装置およびその製造方法 |

| JP4142228B2 (ja) * | 2000-02-01 | 2008-09-03 | 株式会社ルネサステクノロジ | 半導体集積回路装置 |

| US7053005B2 (en) * | 2000-05-02 | 2006-05-30 | Samsung Electronics Co., Ltd. | Method of forming a silicon oxide layer in a semiconductor manufacturing process |

| KR100362834B1 (ko) | 2000-05-02 | 2002-11-29 | 삼성전자 주식회사 | 반도체 장치의 산화막 형성 방법 및 이에 의하여 제조된 반도체 장치 |

| US6683380B2 (en) | 2000-07-07 | 2004-01-27 | Texas Instruments Incorporated | Integrated circuit with bonding layer over active circuitry |

| JP2002118167A (ja) | 2000-10-06 | 2002-04-19 | Nec Corp | 半導体装置の製造方法 |

| US6479405B2 (en) * | 2000-10-12 | 2002-11-12 | Samsung Electronics Co., Ltd. | Method of forming silicon oxide layer in semiconductor manufacturing process using spin-on glass composition and isolation method using the same method |

| DE10120929A1 (de) * | 2001-04-30 | 2002-10-31 | Infineon Technologies Ag | Herstellungsverfahren für eine integrierte Schaltung |

| FR2832854B1 (fr) * | 2001-11-28 | 2004-03-12 | St Microelectronics Sa | Fabrication de memoire dram et de transistor mos |

| JP3612525B2 (ja) * | 2002-06-04 | 2005-01-19 | Nec液晶テクノロジー株式会社 | 薄膜半導体装置の製造方法及びそのレジストパターン形成方法 |

| JP4018954B2 (ja) * | 2002-08-20 | 2007-12-05 | エルピーダメモリ株式会社 | 半導体装置の製造方法 |

| US7037840B2 (en) * | 2004-01-26 | 2006-05-02 | Micron Technology, Inc. | Methods of forming planarized surfaces over semiconductor substrates |

| US7507661B2 (en) * | 2004-08-11 | 2009-03-24 | Spansion Llc | Method of forming narrowly spaced flash memory contact openings and lithography masks |

| US7605033B2 (en) * | 2004-09-01 | 2009-10-20 | Micron Technology, Inc. | Low resistance peripheral local interconnect contacts with selective wet strip of titanium |

| TWI242828B (en) * | 2004-12-20 | 2005-11-01 | Powerchip Semiconductor Corp | Inspection method for an semiconductor device |

| JP5096669B2 (ja) | 2005-07-06 | 2012-12-12 | ルネサスエレクトロニクス株式会社 | 半導体集積回路装置の製造方法 |

| KR100876957B1 (ko) * | 2006-10-20 | 2009-01-07 | 삼성전자주식회사 | 노어형 불 휘발성 메모리 소자 및 이를 형성하기 위한 형성방법 |

| JP2009054683A (ja) * | 2007-08-24 | 2009-03-12 | Panasonic Corp | 半導体装置およびその製造方法 |

| JP2010056156A (ja) * | 2008-08-26 | 2010-03-11 | Renesas Technology Corp | 半導体装置およびその製造方法 |

| US8373239B2 (en) | 2010-06-08 | 2013-02-12 | International Business Machines Corporation | Structure and method for replacement gate MOSFET with self-aligned contact using sacrificial mandrel dielectric |

| US9039909B2 (en) | 2011-02-28 | 2015-05-26 | Tokyo Electron Limited | Plasma etching method, semiconductor device manufacturing method and computer-readable storage medium |

| JP2015153870A (ja) | 2014-02-13 | 2015-08-24 | キヤノン株式会社 | 半導体装置の製造方法、光電変換装置 |

| CN115843175A (zh) * | 2021-08-20 | 2023-03-24 | 长鑫存储技术有限公司 | 半导体结构及其制备方法 |

Family Cites Families (13)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JP2765478B2 (ja) * | 1994-03-30 | 1998-06-18 | 日本電気株式会社 | 半導体装置およびその製造方法 |

| US5482894A (en) * | 1994-08-23 | 1996-01-09 | Texas Instruments Incorporated | Method of fabricating a self-aligned contact using organic dielectric materials |

| JP3571088B2 (ja) | 1994-10-25 | 2004-09-29 | 沖電気工業株式会社 | Dramセルコンタクトの構造及びその形成方法 |

| KR0141950B1 (ko) * | 1994-12-22 | 1998-06-01 | 문정환 | 반도체소자의 제조방법 |

| JPH08316313A (ja) | 1995-05-18 | 1996-11-29 | Sony Corp | コンタクトホールの形成方法 |

| JP3402022B2 (ja) * | 1995-11-07 | 2003-04-28 | 三菱電機株式会社 | 半導体装置の製造方法 |

| US5795820A (en) * | 1996-07-01 | 1998-08-18 | Advanced Micro Devices | Method for simplifying the manufacture of an interlayer dielectric stack |

| KR100192521B1 (ko) * | 1996-07-19 | 1999-06-15 | 구본준 | 반도체장치의 제조방법 |

| KR100226767B1 (ko) * | 1996-10-04 | 1999-10-15 | 김영환 | 반도체 소자의 제조 방법 |

| TW320765B (en) * | 1997-02-22 | 1997-11-21 | United Microelectronics Corp | Manufacturing method of self-aligned contact of dynamic random access memory |

| US5843816A (en) * | 1997-07-28 | 1998-12-01 | Taiwan Semiconductor Manufacturing Company, Ltd. | Integrated self-aligned butt contact process flow and structure for six transistor full complementary metal oxide semiconductor static random access memory cell |

| JPH11186236A (ja) * | 1997-12-24 | 1999-07-09 | Mitsubishi Electric Corp | エッチング方法 |

| US6046103A (en) * | 1999-08-02 | 2000-04-04 | Taiwan Semiconductor Manufacturing Company | Borderless contact process for a salicide devices |

-

1998

- 1998-08-31 JP JP10246147A patent/JP2000077625A/ja active Pending

-

1999

- 1999-08-05 SG SG1999003824A patent/SG75976A1/en unknown

- 1999-08-06 TW TW088113481A patent/TW451460B/zh not_active IP Right Cessation

- 1999-08-24 US US09/382,329 patent/US6235620B1/en not_active Expired - Lifetime

- 1999-08-26 KR KR1019990035596A patent/KR100715260B1/ko not_active IP Right Cessation

- 1999-08-31 CN CNB991183398A patent/CN1210783C/zh not_active Expired - Fee Related

Also Published As

| Publication number | Publication date |

|---|---|

| SG75976A1 (en) | 2000-10-24 |

| US6235620B1 (en) | 2001-05-22 |

| KR20000017559A (ko) | 2000-03-25 |

| JP2000077625A (ja) | 2000-03-14 |

| CN1246727A (zh) | 2000-03-08 |

| TW451460B (en) | 2001-08-21 |

| KR100715260B1 (ko) | 2007-05-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1210783C (zh) | 半导体集成电路器件的制造工艺 | |

| CN1267982C (zh) | 半导体器件的隔离方法 | |

| CN1271716C (zh) | 半导体器件的制造方法 | |

| CN1290194C (zh) | 电容元件、半导体存储器及其制备方法 | |

| CN1139129C (zh) | 半导体集成电路器件及其制造方法 | |

| CN1638131B (zh) | 具有阶梯状柱形结构的电容器的半导体器件及其制造方法 | |

| TW408433B (en) | Method for fabricating semiconductor integrated circuit | |

| CN1158708C (zh) | 半导体集成电路及其制造方法 | |

| CN1173394C (zh) | 制造半导体集成电路器件的方法 | |

| CN1162845A (zh) | 半导体集成电路装置及其制造方法 | |

| CN1905194A (zh) | 半导体器件及其制造方法 | |

| CN1808717A (zh) | 具有铁电电容器的半导体器件及其制造方法 | |

| CN1525553A (zh) | 半导体装置的制造方法 | |

| CN1943037A (zh) | 半导体器件及其制造方法 | |

| CN100343976C (zh) | 铁电随机存取存储器的制作方法 | |

| CN1622288A (zh) | 半导体装置的制造方法 | |

| CN1906741A (zh) | 半导体器件及其制造工艺 | |

| JP4257343B2 (ja) | 半導体装置の製造方法 | |

| JP4437301B2 (ja) | 半導体装置の製造方法 | |

| US6649465B2 (en) | Process for manufacturing a semiconductor memory device including a memory cell selecting transistor and a capacitor with metal electrodes | |

| US6426255B1 (en) | Process for making a semiconductor integrated circuit device having a dynamic random access memory | |

| US7297638B2 (en) | Method for manufacturing a semiconductor device | |

| JP2008135543A (ja) | 不揮発性記憶装置およびその製造方法 | |

| CN1149672C (zh) | 半导体装置及其制造方法 | |

| JP3648499B2 (ja) | 半導体装置の製造方法、及び、半導体装置 |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C14 | Grant of patent or utility model | ||

| GR01 | Patent grant | ||

| ASS | Succession or assignment of patent right |

Owner name: ELPIDA MEMORY INC. Free format text: FORMER OWNER: HITACHI CO., LTD. Effective date: 20061208 |

|

| C41 | Transfer of patent application or patent right or utility model | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20061208 Address after: Tokyo, Japan Patentee after: Nihitatsu Memory Co., Ltd. Address before: Tokyo, Japan Patentee before: Hitachi Ltd. |

|

| ASS | Succession or assignment of patent right |

Owner name: PS4 LASCO CO., LTD. Free format text: FORMER OWNER: NIHITATSU MEMORY CO., LTD. Effective date: 20130903 |

|

| C41 | Transfer of patent application or patent right or utility model | ||

| TR01 | Transfer of patent right |

Effective date of registration: 20130903 Address after: Luxemburg Luxemburg Patentee after: ELPIDA MEMORY INC. Address before: Tokyo, Japan Patentee before: Nihitatsu Memory Co., Ltd. |

|

| CF01 | Termination of patent right due to non-payment of annual fee |

Granted publication date: 20050713 Termination date: 20150831 |

|

| EXPY | Termination of patent right or utility model |