CN1716781A - 可编程逻辑的专用集成电路等价实现及相关方法 - Google Patents

可编程逻辑的专用集成电路等价实现及相关方法 Download PDFInfo

- Publication number

- CN1716781A CN1716781A CN 200510072989 CN200510072989A CN1716781A CN 1716781 A CN1716781 A CN 1716781A CN 200510072989 CN200510072989 CN 200510072989 CN 200510072989 A CN200510072989 A CN 200510072989A CN 1716781 A CN1716781 A CN 1716781A

- Authority

- CN

- China

- Prior art keywords

- hle

- circuit

- fpga

- asic

- design

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Pending

Links

Images

Classifications

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/177—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components arranged in matrix form

-

- H—ELECTRICITY

- H03—ELECTRONIC CIRCUITRY

- H03K—PULSE TECHNIQUE

- H03K19/00—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits

- H03K19/02—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components

- H03K19/173—Logic circuits, i.e. having at least two inputs acting on one output; Inverting circuits using specified components using elementary logic circuits as components

- H03K19/1733—Controllable logic circuits

- H03K19/1737—Controllable logic circuits using multiplexers

Abstract

通过使用某种ASIC体系结构来辅助提供FPGA的ASIC等效实现,并使其更加高效与经济,所述的ASIC结构包括多个所谓的混合逻辑单元(HLE),每个HLE能够提供一个FPGA逻辑单元(LE)的一部分功能。各个用以实现用户逻辑设计的FPGA LE的功能可以被映射到一个或多个HLE,而无需重新综合用户逻辑。只有实现各个LE的功能所必须的HLE才会被使用。各个LE与一个HLE或一组HLE之间的一对一等效有助于FPGA与ASIC设计之间的双向映射(无需再综合)。

Description

技术领域

本发明涉及可被用来等效或替代可编程逻辑电路(PLD或FPGA)的专用集成电路(ASIC)。本发明还涉及将特定用于ASIC或PLD(或FPGA)的设计在这两种类型的器件间进行转换,从而实现器件的互换性。

背景技术

一个典型的可编程逻辑器件(PLD)或现场可编程门阵列(FPGA)中包含许多固定大小的逻辑单元(LE)。(此处为了方便,用FPGA作为PLD与FPGA的通用名词。)例如,一个FPGA LE中可以包括一个四输入查找表(LUT)、一个寄存器以及一些布线电路,在需要顺序逻辑或运算时,这些布线电路允许使用寄存器(比如寄存LUT的输出),而在只需要组合逻辑或运算时则可以让LUT输出旁路寄存器。一个FPGA LE还可能具有其他特性或能力,但是以上述的例子作为示范已经足够了。除了许多LE之外,一个FPGA通常还具有可编程的布线电路,可以通过多种不同的方式向LE、从LE、以及/或在LE之间传递信号,从而通过组合或使用多个LE来完成各种各样的逻辑或逻辑类型的操作。除了LE之外,FPGA还具有其他类型的电路,比如输入/输出(I/O)电路、存储器块、微处理器、专用电路-如数字信号处理(DSP)模块、高速串行接口(HSSI)模块等等。这些其他类型的电路还可以通过上述的可编程布线电路彼此互连(并且与LE相连)。

FPGA所具有的许多优势是那些精通本技术的人所熟知的。然而在某些情况下,可能希望得到某个FPGA设计的ASIC等价实现,从而在大规模的应用中降低成本。例如,某个设计可能以FPGA的形式开始。但是在该设计被充分验证且已经达到足够高的产量后,用ASIC等价实现来替代FPGA能够大大降低成本。

提供FPGA的ASIC等价实现的一种已知方法是采用具有与初始FPGA的LE相同的基本组织结构的ASIC体系结构。例如,如果FPGA中包含LE阵列,每个LE具有一个四输入LUT(4-LUT)和一个寄存器,那么ASIC就具有相似的LE阵列,这些LE中也包含4-LUT和寄存器。ASIC中的某些层可以根据特定用户的设计进行定制,以便有效地“编程”LE并提供LE之间所需的互连布线。

上述提供FPGA的ASIC等价实现的方法具有许多优点,但是仍有改进的余地。例如,多数用户设计没有用到一个FPGA上的所有电路。FPGA电路中的某些部分经常不被使用。一个4-LUT仅被用于提供二输入或三输入的功能。某些LE中只有LUT或寄存器(但并非两者)被用到。在任意上述情况下,未被完全利用的LE中的大量电路就被浪费了。如果用相同的基本LE结构构成等价ASIC的基础,就会在ASIC造成同样的浪费。

发明内容

考虑到上述的情况,符合本发明的ASIC体系结构中包括了与等价FPGA中的LE不同的逻辑单元。这些ASIC逻辑单元在本文中被成为混合逻辑单元(HLE)。每个HLE中可以包括相对较小的、通用的组合逻辑元件(比如一输入LUT或1-LUT),相对较小的逻辑门阵列(比如二输入NAND门)以及一些相关的互连线或布线资源。HLE中的工作电路总量(比如1-LUT和NAND门)远远少于相关FPGA LE中的工作电路总量。HLE中的布线资源至少应该可编程(例如利用通孔的掩膜可编程)以实现某些目的,比如实现到HLE的输入连线、从HLE引出的输出连线以及HLE内的内部连线。对于某些利用率相对较低的FPGA LE,一个ASIC HLE就能实现LE的功能。如果一个LE具有较高的利用率,那么就需要用若干相邻(或至少是附近)的HLE来等效实现该LE的功能。HLE的布线资源帮助连接相邻(或附近)的HLE,这些HLE被组合在一起来实现任意LE的功能。在任何情况下,只使用实现LE功能所必需数量的HLE来提供那个LE的等价功能。由于在大多数设计中,许多LE都未被充分利用,因此在等效于FPGA的ASIC上提供的HLE数量远低于所有LE都被充分利用情况下所需的HLE数量。相较使用完全等效于FPGALE的LE的ASIC而言,上述方法能显著减小ASIC尺寸。

至少在很大程度上,每个LE最好与等效的HLE或HLE组之间存在着一对一的对应关系。这有助于将FPGA设计转换为等效的ASIC,反之亦然,而且不需要重新综合用户的逻辑。避免这种再综合能够节约时间和成本,而且能够更好地保证ASIC与FPGA等价实现能够大致相同的工作而不会出现偏差(假设FPGA与ASIC都已被验证工作正常)。

本发明的其他特性、其本质及各种优点将通过附图及下文的详细说明体现出来。

附图说明

图1示出了一个现有的范例FPGA LE的简化原理方框图。

图2示出了一个FPGA LE的现有的范例ASIC等效实现的简化原理方框图。

图3示出了符合本发明的一个范例ASIC HLE的简化原理方框图。

图4-9示出了用于符合本发明的ASIC的范例可编程互连线结构的简化视图或立体视图。

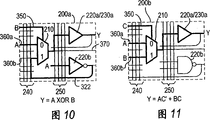

图10示出了符合本发明的范例可编程ASIC HLE的简化原理方框图。

图11示出了另一个符合本发明的范例可编程ASIC HLE的简化原理方框图。

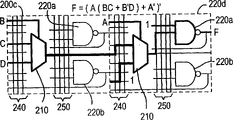

图12示出了一对符合本发明的范例可编程ASIC HLE的简化原理方框图。

图13示出了另一对符合本发明的范例可编程ASIC HLE的简化原理方框图。

图14示出了若干范例ASIC HLE的简化原理方框图,其中的HLE带有符合本发明的附加范例可编程互连线电路。

图15示出的简化框图展示了一个符合本发明的ASIC上的HLE的范例组织结构。

图16示出的简化框图展示了符合本发明的ASIC上的HLE的使用实例。

图17示出的简化框图展示了符合本发明的ASIC上的附加可编程互连线电路的实例。

图18示出了符合本发明的范例方法的流程图。

图19示出了符合本发明的范例方法的另一种流程图。

图20示出了符合本发明的范例方法的另一种流程图。

图21a-c、22a-c以及图23示出的原理方框图展示了符合本发明的HLE的某些可用元件的范例使用方法。

具体实施方式

在图1中示出了一种现有的范例FPGA LE 10。LE 10中包括一个4-LUT部分12和一个寄存器部分14。4-LUT部分12中包括16个可编程存储器(如RAM)单元20-0至20-15。RAM单元20的每一对输出分别被加载到8个二输入多路选择器(mux)22-0至22-7上。4-LUT输入A控制各个多路选择器22选择它的哪一个输入(来自RAM单元20)作为输出。例如,如果输入A是逻辑1,各个多路选择器22就选择其高位输入作为其输出。如果输入A为逻辑0,各个多路选择器22就选择其低位输入作为其输出。多路选择器22的每一对输出分别被加载到四个二输入多路选择器24的输入端。4-LUT输入端B控制各个多路选择器24选择它的哪一个输入作为输出。同样,如果B为逻辑1,多路选择器24就选择其高位输入作为输出。如果B为逻辑0,多路选择器24则选择其低位输入作为输出。多路选择器24的每一对输出分别被加载到两个二输入多路选择器26的输入端。4-LUT输入端C控制各个多路选择器26选择它的哪一个输入作为输出。逻辑功能与多路选择器22及24相似。多路选择器26的输出被加载到二输入多路选择器28上。4-LUT输入端D控制多路选择器28输出它的哪一个输入(与输入端A-C的逻辑相同)。

多路选择器30的输出信号被加载到驱动电路30。驱动器30的输出端是LE 10的一个输出(组合输出32)。驱动器30的输出被加载到多路选择器40的一个输入端上。送入多路选择器40的另一个输入是到LE 10的另一个输入。多路选择器40可以被控制(比如通过可编程RAM单元42)选择它两个输入中的一个来加载到寄存器44的数据输入端。这种安排使得寄存器44可以被用来在不需要寄存LUT12的输出时寄存另一个信号。寄存器44的输出是LE 10的寄存输出46。

图2示出了LE 10的一种现有可行的ASIC等效实现,它被设置成一个二输入AND(与)门(输出未经过寄存)。图2中与图1中相似的单元的引用标号是它们在图1中的引用标号加上100。因此在ASIC LE 10中,输入端C和D被相与来产生未寄存的LE输出132。多路选择器122-0和122-1的输入被绑定在逻辑1上。其他多路选择器122的输入被绑定为逻辑0。这样能够使得输入A和B与输入“无关”。只有输入C和D能够影响输出,输出是C和D相与的结果。LE110的这种用法意味着放入一个X的单元实际上未被使用。特别的,所有的元件122、124、126-1、140和144实际上都未被使用。因此,在用来等效一个利用率如此低的FPGA LE 10的ASIC电路上包括所有这些元件是一个极大的浪费。可以采用逻辑删减(例如可以参见于2004年6月4日提交(Attorney Docket 174/309(A877))的Foo美国专利申请_____)来减少必须在ASIC LE 10中提供的电路数量。例如,可以通过选择性使用输入A或它的补集作为下一级多路选择(124)的输入,来删减第一级多路选择(122)。然而,只要是用来实现一个低利用率的FPGA LE 100,那么即使在经过如此删减的ASIC LE 110中,也仍然有大量电路被浪费。

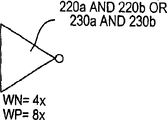

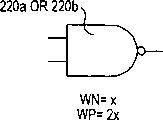

图3示出了一种所谓的混合逻辑单元(HLE)200的示例实施例,该逻辑单元是根据本发明构建的,用以单独或组合起来提供FPGA LE的浪费较小的ASIC等效实现。尽管下面要详细地说明图3中所示的特定HLE 200的结构,但是这里需要作为前提条件强调的是,该实施例仅仅是一个示例,这种结构的许多变形都是可行的,并且这些变形不会偏离本发明的范围与指导思想。

HLE 200中包括二输入多路选择器(mux)210、两个二输入NAND门220a和220b、两个反向缓冲器或驱动器230a和230b,以及互连线资源,接下来的文字将更详细地说明它们。图3中所示的互连线资源包括多条从多路选择器210引出的上行垂直导体240,在多路选择器210与NAND门220之间的多条垂直导体250,NAND门220与驱动器230之间的一条(或多条)垂直导体260,以及多条从驱动器230引出的垂直导体270。图3中所示的互连线资源还包括若干水平导体(比如导体310、320、330和340)。导体240、250、260、270、310、320、330以及340都是相对通用的导体,这意味着它们可以被用来产生若干不同来源中的任何一个与若干不同目的地中的任何一个之间的任意不同连接。除了这些相对通用的导体之外,HLE 200中还包括若干更为专用的导体。例如,导体350专门用于向多路选择起210提供控制输入(尽管有若干来源可以作为控制输入信号,这将在下文中详细说明,如果需要的话也可以用导体350做其他用途)。如另一个实例,导体360a与360b专门用于向多路选择器210提供两个可选的输入(同样可以来自若干可能来源中的任意一个,同样在需要的情况下可以用作其他用途)。如再另一个实例,导体370专门用于传导多路选择器210的输出,尽管该输出可以通往若干目的地中的任何一个。尽管某些导体被描述为相对通用的,而另一些导体则被描述为较为专用的,但是这些描述性的概念仅仅是为了方便才采用的。它们并不是为了产生限制,两者之间也没有任何明确的分别,且两种类型不必同时存在。

图3中位于导体交叉点处的小实心点410代表可以根据需要在交叉导体之间产生或不产生连接。这些连接因而是可编程的。在优选实施例中,这些连接是可以利用通孔进行掩膜编程的,所述的通孔可以被包括、也可以不被包括在含有交叉导体的层之间的一个或多个层中。(尽管本文中主要提及了通孔编程,但这仅仅是一个实例,可以按照需要采用任意其他的编程技术。在本说明书的后文中提到了可用编程技术的其他实例。)图4示出了分别位于不同金属层中的两个交叉导体240与320,所述的金属层位于一个含有HLE 200的集成电路器件上。在图4中,这些导体通过通孔420彼此相连,所述的通孔穿过两个金属层之间的绝缘层。在图5中示出了绝缘层中没有通孔的相同结构。因此,在图5中,导体240与320彼此没有相连。(导体240或320可以任意位于较高或较低的金属层中,这是设计选择。)

图3中的多个X 430代表了导体部分能根据需要可编程地彼此相连或不相连的位置。对于上文中所提及的小实心点410所采用的相同技术选择对于连接430同样适用。例如,图6示出了具有代表性的两段导体320,它们通过掩膜可编程的通孔440连接到桥接导体450。这样,这两段导体320就通过通孔440与桥接导体450连接到了一起。图7示出了相同的但没有通孔440的结构。因此在图7中,导体段没有彼此相连。它们彼此是电绝缘的。

图3中所示的大空心圆或椭圆460代表了带有那些圆环或椭圆的导体能被可编程地连接到所谓高层互连线资源(图3中未示出)的位置,所述的高层互连资源位于包括HLE 200的器件上。这种高层互连线资源可以被用于在元件(如HLE、器件输入/输出(I/O)端口等等)之间传递信号,所述的元件彼此不相邻,或是彼此不靠近。(短语“高层”并不表示物理上较高的层次,而仅仅是分级结构上的高层。)可编程连接460可以按照上述任意一种方式产生(例如用于可编程连接410的方法)。例如,图8示出了通过掩膜可编程通孔470与高层导体510相连的代表性导体360。图9示出了相同的结构位置460,但是其中的导体360与高层导体520间不存在连接。

如果图3中所示的在不同轴向上延伸的导体在另一个导体处终结(或者如果两个导体都在另一个导体处终结),那么它们总是彼此相连的。图中所示彼此交叉但在交叉点处没有小实心点的导体应该不能在所述的交叉点处彼此相接。

图3中示出某些导体具有特定的外部连接。其中最顶端的导体310被示为总是与VCC(比如逻辑1)相接。图3中次顶端的导体310被示为总是与VSS(比如逻辑0)相连。导体312、314以及316都被示为来自其他相邻HLE的输入连线,这些HLE分别位于所示HLE的上方、左边和下方。导体332向位于所示HLE上方的HLE提供输入316。导体272向位于所示HLE右边的HLE提供输入314。导体342向位于所示HLE下方的HLE提供输入312。相邻或相近HLE之间的这些所谓的“潜在”连接可以是器件的互连线资源中的常备或固定部分。它们实际上是否被使用(或是它们如何被使用)都是可编程的,这取决于位于潜在连线两端的可编程连线410被怎样编程。

位于所示导体如240和250两端的X 430代表了那些导体能够可编程地与位于所示HLE附近的其他HLE中的类似导体相连的位置。

一个HLE 200、或是相对较少但数量合适的相邻或相近的HLE200,可以被用来实现图1中所示的一个FPGA LE 10所能实现的任何功能。在各种情况下,只有实现LE的功能所必需数量的HLE被使用来产生所述FPGA LE的等效ASIC。

图10示出了一种形式略为简单的HLE 200a(至少是HLE 200(图3所示)的简化版本),该HLE被用来提供A XOR(异或)B得到的输出Y。在该示例中实际使用到的HLE 200a的互连线资源用更重(更粗)的线条画出。其他存在但未在该例中用到的互连线资源用较轻(较细)的线条表示。输入A被加载到多路选择器210的上输入端。例如,输入A可以通过可编程连线460(图3示出)进入HLE200a,所述的连线460在图3中被显示为连接在对应的多路选择器输入端IN0上。这样输入A就可以来自器件的更高层互连线电路中的导体(如图8中的510)。输入A还被加载到图3所示的NAND门220b的两个输入端上。这会导致NAND门220b以反相器形式工作,如图10所示。反相器220b(图10)的输出被反馈给多路选择器210的低输入端(比如通过导体322,到垂直导体240之一的可编程连线410(图3),所述垂直导体的一部分,到导体360b的另一条可编程连线410,以及所述导体360b的一部分)。

输入B通过导体350被加载到多路选择器210的控制输入端。例如,输入B可以通过可编程连线460被加载到导体350上,所述的连线460在图3中被示为连接在导体350上。这样输入B就可以从器件更高层的互连线电路进入HLE 200a。当输入B为逻辑0时,多路选择器210就输出位于其两个可选输入引脚中的上一个引脚(即导体360a)上的信号。当输入B为逻辑1时,多路选择器210就输出位于其两个可选输入引脚中的下一个引脚(即导体360b)上的信号。因此,多路选择器210的输出信号就是A XOR B。

多路选择器210的输出信号被加载到NAND门220a(图3)的两个输入端上,因此该NAND门就起一个反相器的作用。NAND门220a的输出被加载到反相驱动器230a,该反相驱动器再次反转信号。因而,元件220a与230a组合在一起的作用就是为多路选择器210的输出信号提供一个非反相的输出驱动器,即Y(=A XOR B)。

多路选择器210的输出信号到NAND门220a的两个输入端的连线可以通过导体370的一部分、从所述导体到垂直导体250之一的可编程连线410(图3)、垂直导体250的一部分、以及从所述导体到NAND门220a的两个输入端的另外两条可编程连线410来实现。驱动器220a/230a的输出Y可以通过反相器230a的输出引脚上的可编程连线460(图3)被接入更高层的互连线电路。

这样图10就示出了一种逻辑功能的一个实例,该功能可以在单个HLE中实现,且浪费的资源相对较少。在与一个FPGA LE(与图1、2中所示的类似)相当的ASIC LE中实现同样的功能会使该ASICLE中的一大部分资源不被使用,因而造成浪费(即使采用上述类型的逻辑删减也只能达到图2所示的结果)。本文中所示的HLE结构提供了一种浪费少的多的实现方式。

图11示出了另一种逻辑功能的实例,该功能可以在单个HLE200b(同样类似图3所示的HLE 200,或至少概念上相似)中实现。图11中所实现的功能是Y=(A AND C’)OR(B AND C)。在图11中使用的导体与元件都用粗线示出。在图11中未被用到的导体与元件都用较细的线条示出。信号接入、通过以及接出HLE 200b的方式都能从上文的说明中体现出来,因而不需要进一步的详细说明。

图12示出了一个四输入组合逻辑功能的实例,该逻辑功能通过两个相邻的HLE 200c与200d实现,其中各个HLE都与图3中所示的HLE 200相似,或是至少在概念上相似。图中所实现的逻辑功能为F=(A(BC+B’D)+A’)’。被使用来实现该功能的元件与导体在图12中都用较粗的线条示出。未被使用的元件及导体都用较细的线条示出。图12展示了使用潜在连线从一个HLE向另一个相邻或相近的HLE传递信号。在这种情况下,HLE 200c中的多路选择器210的输出信号通过图3中所示的潜在连线如272/314传递给HLE 200d。(从图3可见、且在本说明书上文中已经叙述过多路选择器210的输出是如何被连接到右端的潜在输出272,再从那连接到右边的HLE的潜在输入314,最后从所述输入连接到右边的HLE中的多路选择器210的输入端。)图12还展示了如何使用HLE 200d中的元件210及220a的VCC输入(逻辑1)。这可以利用图3中所示的一条导体310以及从所述导体连接到元件210和220a的所需输入端的可编程连线(比如可编程连线410)来实现。

图12示出了水平相邻的HLE之间的一些额外互连线,它们未在图3中示出(至少未明显示出)。这些连线是从每个HLE到其右边的HLE的更为广泛的连接线。图3表现出只有潜在连线可用于此类连接。但是图12示出了能从各个HLE传递到右边的HLE的3个信号(多路选择器210的输出以及NAND门220a与220b的输出),这些信号的传递是在HLE连线资源的结构层次上实现的。这种额外、相对直接、HLE到HLE的连接只是构建符合本发明的HLE的许多可行途径中的一种。当然,如果没有在HLE层次上提供这种额外的直接连接,也可以利用较高层的互连线电路产生类似的连接。然而,目前人们相信最好能够提供充足的、相对直接的、HLE到HLE的互连能力(包括潜在连线),以便实现HLE到HLE连线的主要部分(最好至少是大部分),所述的连线是用以实现任意FPGA LE功能的一组HLE所需要的。这样,高层互连线就可以被保留以供远距离互连使用。

图13示出了使用两个相邻HLE 200e和200f来提供一个触发器或寄存器(典型FPGA LE的功能之一)的实例。同样,HLE 200e和200f都与图3中的HLE 200相似(或至少在概念上相似)。用来提供触发器的元件及导体在图13中用粗线示出。未被使用的结构用较细的线条示出。此处不必详细描述图13中所述的所有连线,或是如何实现那些连线,因为从图3以及上文的说明中已经体现出了这些信息。要被寄存的信号D可以通过可编程连线460(图3)从器件的高层互连线电路、或是在较低的层次从另一个相邻或相近的HLE进入HLE200e,只要说明这一点就足够了。对于驱动触发器的时钟信号CLK来说也是一样。(该信号是HLE 200e和200f都需要的。)或者,CLK也可以按照图3中所示的用于VCC和VSS的方式进入每个HLE。图13示出了CLR’和SET’信号,它们通过导体250以及来自上方或下方相邻HLE内的类似导体的可编程连线430(图3)进入HLE 200e和200f。最终这些信号可以通过与图3中所示的VCC和VSS类似的方式进入HLE阵列,或是通过连接到器件的高层互连线电路的可编程连线460(图3)。触发器的寄存输出Q与Q’可以通过更多的可编程连线460进入器件的高层互连线电路,或者它们也可以通过较低层的连线进入其他相邻或相近的HLE。

图14示出了若干相邻的HLE 200g、200h、200i和200j,其中强调了HLE之间的某些(但并未全部)相对直接的连线资源。在图14所示的实施例中,HLE之间的互连线资源包括从HLE 200h的NAND门220a到其右边的HLE 200j的直接连线222(示为粗虚线)。图14中示出的另一条直接连线是从HLE 200h中的多路选择器210的输出端到其右边的HLE 200j的连线212(示为粗点线)。图中示出的另一条直接连线是潜在连线网络214(示为粗实线),该网络从HLE 200h的潜在输出端延伸到HLE 200g、200i以及位于HLE 200j右边的另一个HLE(未示出)。在该实施例中,潜在输出被示为可以编程选择来自导体212或222,但是也可以将其他来源用于该信号。图14中所强调的所有HLE到HLE连线资源(包括潜在连线)都可以实现在用于HLE内部连线资源的同一层金属中,因此就不需要依靠高层互连线电路,后者通常被用于长距离的互连。

图15示出了一个集成电路器件500上的HLE 200的示例排列。图15中的HLE 200可以如图3或本文中所有其他附图所示的那样构建,或者它们也可以包括本说明书中的任意一处提及的任何改进。在图15所示的示例排列中,HLE 200是以行列交叉的二维阵列形式排布在器件500上。器件500中还包括其他电路,如I/O模块、存储器模块等等(未示出)。因此符合本发明的ASIC可以被称为“结构化ASIC”,因为它们具有基本的电路组织或结构(比如图15所示的二维HLE阵列),并且可以对这些电路组织及结构作出自定义的修改及/或添加(比如HLE内部与/或HLE之间的互连线)。如果器件500不被当作FPGA的等效产品来使用,那么器件500上HLE 200的总数就可以少于FPGA上的LE数量乘以实现一个FPGA LE所有功能所需的HLE 200的最大数量。这是因为只有实现每个FPGA LE的功能所必需数量的HLE才是必要的,而在大多数情况下要实现这个目的所需的HLE数量要少于最大数量。随着下文的进一步说明,这一点的某些方面将变得愈加明了。

图16示出了器件500上的HLE 200是如何被单独或一起使用来实现一个等效FPGA中的LE功能的。在图16中,被一起使用的相邻或相近的HLE 200被打上同样的阴影,这与用于其他相邻或相近HLE的阴影不同。为了方便引用,图16中的HLE列被标号为1、2、3等等,HLE行则被标上字母A、B、C等等。利用行和列的引用号,图16示出了以下被一同使用的HLE:

组1:A1/A2/B1

组2:A3/A4

组3:B2/C1/C2/C3

组4:B3/B4

组5:D1/E1/E2/F1

组6:D2/D3/D4

组7:F2

上述的各个组合实现了等效FPGA中LE的以下功能:

组1:FPGA LE A1的组合逻辑

组2:FPGA LE A1的寄存器功能

组3:FPGA LE B1的组合逻辑

组4:FPGA LE B1的寄存器功能

组5:FPGA LE C1的组合逻辑

组6:FPGA LE D1的组合逻辑

组7:FPGA LE E1的组合逻辑

在以上的列表中,行字母与列数字(类似图16所示的那些)都被用来引用一个二维FPGA LE阵列中的LE。

可以理解的是,图16所示的HLE分组实例仅仅是示例性的,多种其它分组也同样可行。在特定情况下(ASIC)采用的实际分组是由需要在ASIC器件500中等效实现的FPGA LE功能决定的。但是,先前段落中的示例列表所建议的一个优选项如下文所述。它对于要实现在ASIC HLE结构中的FPGA LE功能而言是比较理想的。例如,由FPGA左上角附近的LE实现的一种或多种功能最好能够由ASIC中相应位置上(比如靠近左上角)的必要数量的HLE来实现。

结合图16,还要说明的一点是,ASIC 500中的某些HLE 200可能不会被用到。

为了完整性,图17示出了ASIC 500上的一些示例性的高层互连线电路510、520。530、540和550。例如,电路520可以被用来(在ASIC定制的基础上)产生从位于ASIC 500左上角附近的HLE 200的I/O端口460(比如一个输出)到位于ASIC正下方附近的另一个HLE 200的I/O端口460(比如一个输入)的连接。举另一个例子来说,电路550可以被用来(在ASIC定制的基础上)产生从位于ASIC500左下角附近的HLE 200的I/O端口460(比如一个输出)到ASIC的输出端口(未示出)的连接。这里可能需要两层可定制金属(以及穿插的可定制通孔)来提供非阻塞的、高层的布线,这些布线可以根据任何所需的安排进入、引出HLE 200以及/或是在HLE 200之间互连。

在ASIC设计中较理想的情况是,符合本发明的器件中需要自行定制(编程)的层数相对较小。在本文中至此已经提到过需要自定制的层主要是提供HLE的垂直与水平互连线导体之间的可编程通孔420/440(图4和图6)或类似结构的层、为连接高层互连线电路的I/O端口提供可编程通孔470(图8)的层,以及提供高层互连线电路本身的层。(或者,也可以总是提供全部的I/O端口通孔470,在需要时将它们与高层互连线电路相连(使用),而在不需要时则旁路(不使用))。

本发明的一个重要优点就是任何FPGA LE的功能都可以被映射到一个或多个ASIC HLE上(反之亦然)。这样就可以提供对应于任何用户的已编程或已配置FPGA的基于HLE的ASIC等效产品(反之亦然),而不需要在任何层次上(除了上文中提到的简单的重映射以外)重新综合用户的逻辑。这与大多数结构化ASIC厂商提供的FPGA等效实现相比有明显的优势。通常,这类厂商会采用复杂的多门或门阵列设计来构造逻辑结构。由于这些逻辑结构的构建模块与FPGA不相近,如果使用FPGA进行了原型设计,就要重新进行综合。这种不灵活性就要求额外的验证工作来保证FPGA中设计的原型产品与结构化ASIC中构造的设计在功能上相同。如果要产生一个与这种结构化ASIC等效的已编程FPGA,逻辑的重综合也同样是必要的。本发明避免了在已配置FPGA与基于HLE的ASIC之间进行迁移时所需的这种重新综合。另外,与结构上类似FPGA LE的ASIC LE相比,HLE还节省了空间(因为对于每个FPGA LE来说,只有实现对应已编程FPGA LE的功能所必须数量的HLE才被使用)。

图18示出了一系列示例性的流程单元(即步骤和/或结果),这些流程单元可被用来产生对应于等效的基于LE的FPGA以及基于HLE的ASIC的设计。图18示出了首先产生一个FPGA设计,然后再由所述的FPGA设计产生一个大致等效的ASIC设计。用户已经指定的必要逻辑(以及其他可能的功能)在流程单元610中示出,典型的标准形式为RTL(寄存器传输级)。在流程单元620中,所述的RTL由流程单元610中所提供的相对通用的规范被综合成可以在具有特定特性的FPGA中实现的形式(比如包含4-LUT和寄存器的LE等等)。流程单元620可以利用商用的FPGA综合软件工具来完成,比如位于California,San Jose的Altera公司所提供的Quatus II产品。综合620得到的结果接着在流程单元630中被映射到特定的FPGA产品中。

下一个流程单元640是将FPGA映射转换为对应于特定FPGA的网单及布局信息,所述的特定FPGA是属于流程单元630所设想的一般FPGA产品范围之内的。例如,流程单元640可以工作在具有特定数量及结构的资源的FPGA中。流程单元640规定了用这些资源中的哪一些来实现用户设计所需的各个功能。特定类型的FPGA可以根据在流程单元640中产生的信息通过比特流来编程。

为了产生一个与根据信息640编程的FPGA基本等效的基于HLE的ASIC,要根据本发明对640信息执行步骤650。步骤650是一种1对1的功能单元映射,它将640信息中的功能单元映射为一个或一组HLE,这些HLE可以最小化地实现所述的功能单元。在本说明书上文所讨论的例子中,所述的功能单元要么是给定的FPGA LE中的LUT所实现的组合逻辑,要么是给定的FPGA LE中的寄存器。如果所述的功能单元是组合逻辑,那么步骤650就将该逻辑映射为能够实现所述功能的最少数量的HLE。其中最好包括采用上述的逻辑删减来减少所需的选择级数。其他技术也可以被用来简化(优化)HLE中实现的逻辑。如果所述的功能单元是一个寄存器,那么步骤650就将该寄存器映射为两个HLE,就如图13中所示的那样。步骤650还选择让哪些HLE来实现哪些功能单元,以及各个HLE应该被如何配置以便让该HLE能够实现它在被分配到的功能单元中的作用。例如,步骤650在将FPGA上的功能定位到等效的ASIC上时,最好保持一般的功能布局(但是保持一般定位并不是必需的,且等效的HLE可以被放置在目标ASIC的其他部分中)。步骤650还规定了高层的布线,用以提供引入、引出HLE或HLE组、以及/或是在HLE或HLE组之间的连线,这些连线通常是不能在较低的、较为直接的、HLE间的层次上提供的。以上说明中假定了步骤650是在具有足够容量来实现起始FPGA中所规定功能的ASIC中执行的。

步骤650的结果660是ASIC网单和布局信息,这些信息可以被用来规定制造ASIC所需的掩膜,所述的ASIC是在功能上与起始FPGA(由640信息规定的)等效的。比较有利的一点是,所述的660信息是直接从640信息中得到的。这样在执行FPGA到ASIC的转换中,就不需要重新综合用户的起始逻辑规范(比如在步骤620中那样)。因此根据图18所示的步骤及结果所产生的FPGA与ASIC之间的等效性就不会存在缺陷。

图19示出了另一项符合本发明的用于产生等效的基于LE的FPGA与基于HLE的ASIC的技术。流程单元710与720分别与图18中的流程单元610和620相似。与特定FPGA技术相关联的综合720的结果被用来产生用户逻辑设计到FPGA器件、以及用户逻辑设计到基于HLE的ASIC器件的映射。换句话说,一种通用的逻辑综合720被用作映射730和750的共同基础。这两种映射的逻辑等效性就得到了保证。FPGA映射730被用来为特定的FPGA设计产生网单及布局信息(即编程或配置)。ASIC映射750则被用来为一个特定的掩膜可编程的基于HLE的ASIC的可编程掩膜产生规范760。根据信息740产生的FPGA在逻辑上等效于根据信息760产生的ASIC,反之亦然。例如,如果一开始只产生了ASIC版本,但是保留了根据初始综合720得到的FPGA映射730或FPGA信息740,那么无需重新综合,而只要使用信息740或映射730(再次产生信息740)就能得到与ASIC等效的FPGA。这一点对于从首先产生的FPGA转换到之后所需的等效ASIC而言同样适用,这里假定了最初产生的映射750或信息760都被保留了下来。根据信息760或映射750(现在被当作用于再次产生信息760的基础),可以在任何时候产生ASIC。无需进行逻辑再综合,而且之后产生的ASIC与最初产生的FPGA之间的等效性也有保证。

图20示出了另一种符合本发明的根据已有的基于HLE的ASIC产生基于LE的FPGA的技术。同样,图20中的流程单元810和820分别类似于图18中的流程单元610和620(或是图19中的流程单元710和720)。技术映射830与基于LE的FPGA体系相关联,但是它利用HLE库840来执行一个步骤,该步骤能够由基于FPGA LE的映射产生基于HLE的映射。流程单元850根据映射830为掩膜可编程的基于HLE的ASIC的可编程掩膜产生一个规范。ASIC可以根据该规范来产生。

如果今后需要一个等效的FPGA,就可以根据信息850来产生该FPGA,就如图20中进一步示出的那样。在流程单元860中,信息850从基于HLE的形式重新映射回基于LE的形式。这种映射可以是从各个HLE或HLE组回到LE的1对1映射,所述的HLE或HLE组是根据单元830和840中的LE功能得到的,而所述的LE则是最初具有所述功能的LE。为了便于进行这种1对1的映射,信息850中可以包括一个记录,其中记载了它的各个部分是如何从最初的LE得来的。在流程单元860中不需要逻辑再综合。根据单元860,就能得到FPGA网单与布局信息870,并且该信息可以被用来产生与根据信息850得到的ASIC逻辑等效的FPGA。

尽管在前文中至少已经有所暗示,这里还是要明确指出,技术映射830并不能任意地组合HLE来实现用户的逻辑设计。相反,映射830仅限于使用HLE来实现可以在FPGA LE中实现的功能。这使得之后在单元870中对信息850进行1对1的映射860,以便将其映射回基于LE的形式成为可能。

图21a-c、22a-c以及23示出了如图3所示的HLE中的NAND阵列220和可能的其他元件230(或等效电路)可以根据本发明其他方面内容进行各种配置(例如,掩膜编程)的实例。例如,图21a-c示出了提供反相器的各种形式。在图21a中,一个NAND门220的一个输入端被绑定为逻辑1。在图21b中,使用了一个反相器230。在图21c中,NAND门220a和220b或是两个反相器230a和230b被并联(通过对HLE中的互连线资源进行恰当的掩膜编程),以有效地提供一个更大的反相器,比如用于从HLE提供更强的输出驱动。

图22a-c示出了如何提供非反向缓冲器的若干实例。在图22a中,NAND门220a和220b被串连,其中各个NAND门都有一个输入端被绑定到逻辑1。同样,HLE的布线资源被掩膜编程以串连所述的NAND门。在图22b中,反相器230a和230b同样被串连。在图22c中,NAND门220a和b以反相器形式并联(如图21a中所示),以有效地提供一个更大的第一反相器220a/b,并且反相器230a和b被同样并联以有效地提供一个更大的第二反相器230a/b。如图21c中所示,图22c中的较大单元从HLE提供了更强的输出驱动。

图23示出了使用NAND门220a或220b中的一个来提供NAND功能。

在图21-23所示的多种选项中做出某些选择的动机可能是需要在某个使用符合本发明的HLE的器件中为不同的HLE提供不同量的输出驱动。一定尺寸的驱动器通常能够驱动一定数量的寄生负载。在ASIC流程中,如果输出数量非常巨大以至于原始的驱动单元不能驱动负载,往往就必须或希望增大标准单元或金属可编程单元或是插入另一个驱动器(缓冲器或反相器)来提升驱动力。这意味着尺寸增大或增加缓冲器/反相器会造成面积的扩大。然而,使用符合本发明的基于HLE的ASIC,就可以容易利用未被使用的单元(HLE或部分HLE)来提升驱动力(非反相或反相),比如通过低层可编程互连线资源。在各种不同配置中-比如在图21-23中展示的那些-可以一同使用的单元(如220和/或230)就不必位于相同的HLE中。它们可以在相邻或相近的HLE中。

就如上文中已经提到过的那样,可以使用各种技术来节省实现某些功能所需的HLE数量。如上所述,逻辑删减是这类HLE节省技术的一个实例。另一个实例是一个HLE驱动另一个HLE,而第二个HLE被设置为比如一个2输入NAND门。如果发生这种情况,那么ASIC流程就可以将所述的NAND门包含在第一个HLE中,从而将HLE数量从两个减为一个。有许多类似的例子,其中第n个HLE可以被包含到第n-1个HLE中,第n-1个HLE可以被包含到第n-2个HLE中,等等,特别是在包括如图3所示的反相器230的情况下。其他实例还包括(!A AND B),(A AND B)等等。

可以理解,以上说明只是本发明原理的示例,而那些精通本技术的人可以在不偏离本发明范围及指导思想的前提下作出各种改进。例如,本文中所述的FPGA与ASIC不必是纯粹的FPGA或ASIC。一个器件可以部分是FPGA或部分是ASIC与其他组成部分(比如部分FPGA和部分ASIC)。本文中所指的FPGA和ASIC可以被理解为这类混合器件的FPGA或ASIC部分。

尽管本文中主要说明了用通孔编程(参见例如图4-9)进行逻辑构建以及HLE内、HLE间的布线,但是可以理解,其他类型的编程(比如利用金属可选连线、熔丝、反熔丝、CRAM控制、Flash控制等等)也可以被用来作为替代或补充。如果用到了所述的其他技术中的某一些,那么上文中所述的掩膜编程就可以被认为是指代了这些其他编程技术,这些技术可以通过除了自定制或部分自定制掩膜以外的其他方式来实现。同样,尽管本文中的HLE都被描述为用于实现与FPGA LE等效的功能,但本文中所示的HLE都是高密度高性能的元件。因此它们同样可以被用来构成高性能的知识产权(IP)(比如数字信号处理(DSP)模块、微处理器、等等)、存储器,等等。

Claims (58)

1.一种逻辑单元电路,包括:

选择电路,它利用输入到该选择电路的第一选择电路输入信号来选择第二与第三选择电路输入信号中的一个作为选择电路输出信号;

用于提供一个逻辑电路输出信号的逻辑电路,所述的输出信号是第一与第二逻辑电路输入信号的逻辑函数;以及

可编程互连线电路,该电路使得第一与第二逻辑电路输入信号中的至少一个可以从所述选择电路输出信号或一个来自逻辑单元外部的信号得到。

2.根据权利要求1所述的电路,其中所述的选择电路包括多路选择器电路。

3.根据权利要求1所述的电路,其中所述的逻辑电路包括NAND电路。

4.根据权利要求1所述的电路,其中所述的可编程互连线电路包括掩膜可编程电路。

5.根据权利要求1所述的电路,其中所述的可编程电路包括可编程通孔电路。

6.根据权利要求1所述的电路,还包括:

其他可编程互连线电路,用于让第一、第二及第三选择电路输入信号中的至少一个能够从所述的逻辑电路输出信号得到。

7.根据权利要求6所述的电路,还包括:

额外的可编程互连线电路,用于让第一、第二及第三选择电路输入信号中的至少一个能够从来自逻辑单元外部的一个信号得到。

8.根据权利要求1所述的电路,还包括:

其他逻辑电路,用于提供其他的逻辑电路输出信号,所述的输出信号是第一与第二其他逻辑电路输入信号的逻辑函数。

9.根据权利要求8所述的电路,还包括:

其他可编程互连线电路,用于让第一与第二其他逻辑电路输入信号中的至少一个能够从所述的选择电路输出信号或是一个来自逻辑单元外部的信号得出。

10.根据权利要求8所述的电路,还包括:

其他可编程互连线电路,用于让第一与第二其他逻辑电路输入信号中的至少一个能够从所述的逻辑电路输出信号得出。

11.根据权利要求10所述的电路,还包括:

额外的可编程互连线电路,用于让第一与第二其他逻辑电路输入信号中的至少一个能够从所述的选择电路输出信号或是从来自逻辑单元外部的一个信号得出。

12.一种集成电路器件,包括:

多个逻辑单元电路,每个单元都如权利要求1所述的一样。

13.根据权利要求12所述的器件,还包括:

其他可编程互连线电路,用于让来自至少一部分所述逻辑单元电路中每一个的信号被加载到与上述逻辑单元电路相邻的多个逻辑单元电路中的另一个逻辑单元电路上。

14.根据权利要求13所述的器件,其中所述的可编程互连线电路被设置在所述器件的第一子集层中,并且其中所述的其他可编程互连线电路也被设置在所述器件的第一子集层中。

15.根据权利要求14所述的器件,还包括:

额外的可编程互连线电路,用于让来自至少一部分所述逻辑单元电路中每一个的信号被加载到与所述逻辑单元电路不相邻的多个逻辑单元电路中的另一个逻辑单元电路上。

16.根据权利要求15所述的器件,其中所述的额外可编程互连线电路至少部分地被设置在不是所述器件中的第一子集层的层中。

17.一种利用ASIC体系结构来设计基本等效于FPGA的ASIC的方法,所述的ASIC体系结构中包括多个HLE,每个HLE都能够提供所述FPGA的LE的一部分功能,并且这些HLE可以在必要时被组合在一起来实现任意一个LE所能所现的全部功能,所述的方法包括:

综合一个用户逻辑设计;

将综合后的逻辑设计映射为一个FPGA设计;以及

将FPGA设计中的各个LE重新映射为ASIC设计中的一个或多个HLE。

18.根据权利要求17所述的方法,其中所述的映射包括:

生成FPGA网单及布局信息。

19.根据权利要求18所述的方法,其中所述的重新映射是对所述的FPGA网单及布局信息执行的。

20.根据权利要求17所述的方法,其中所述的重新映射包括:

产生ASIC网单与布局信息。

21.根据权利要求19所述的方法,其中所述的重新映射包括:

产生ASIC网单与布局信息。

22.利用权利要求17中所述的方法制造的ASIC。

23.根据权利要求17所述的方法,其中所述的重新映射包括:

利用彼此相邻的多个HLE来实现单个HLE所不能实现的任意LE的功能。

24.根据权利要求17所述的方法,其中所述的重新映射包括:

在将FPGA LE的功能重新映射到一个或多个HLE时使用逻辑删减。

25.根据权利要求17所述的方法,其中所述的重新映射包括:

将每个FPGA LE的(1)逻辑功能与(2)寄存器功能进一步重新映射到各个不同的HLE或HLE组。

26.一种利用ASIC体系结构来设计基本等效的FPGA与ASIC的方法,所述的体系结构中包括多个HLE,每个HLE都能够提供FPGA的LE的一部分功能,并且这些HLE可以在必要时被组合在一起来实现任意一个LE所能所现的全部功能,所述的方法包括:

综合用户的逻辑设计;

将经过综合的逻辑设计映射为一个FPGA设计;以及

将经过综合的逻辑设计映射为一个ASIC设计。

27.根据权利要求26所述的方法,其中所述的映射为FPGA设计包括:

生成FPGA网单及布局信息。

28.根据权利要求26所述的方法,其中所述的映射为ASIC设计包括:

生成ASIC网单及布局信息。

29.利用权利要求26所述的方法制造的ASIC。

30.根据权利要求26所述的方法,其中所述的映射为ASIC设计包括:

使用多个HLE来实现FPGA LE的功能。

31.根据权利要求30所述的方法,其中所述的使用包括:

使用彼此相邻的多个HLE来实现单个HLE无法实现的任意LE的功能。

32.根据权利要求30所述的方法,其中所述的使用包括:

使用逻辑删减来帮助用一个或多个HLE实现一个FPGA LE的功能。

33.根据权利要求30所述的方法,其中所述的使用包括:

使用彼此不同的HLE或HLE组来实现一个FPGA LE的(1)逻辑功能及(2)寄存器功能。

34.一种设计等效于ASIC的FPGA的方法,所述ASIC的结构中包括多个HLE,每个HLE能够提供FPGA LE的一部分功能,并且所述的HLE可以在必要时被组合起来实现任何一个LE所能实现的全部功能,所述的方法包括:

综合用户的逻辑设计;以及

以使用HLE实现FPGA LE功能为基础,将经过综合的逻辑设计映射为一个ASIC设计。

35.一种设计等效于ASIC的FPGA的方法,所述ASIC的结构中包括多个HLE,每个HLE都能构提供FPGA LE的部分功能,并且这些HLE在必要时可以被组合在一起来实现任何一个LE所能实现的全部功能,所述的方法包括:

综合用户的逻辑设计;

以使用HLE实现FPGA LE功能为基础,将经过综合的逻辑设计映射为一个ASIC设计;以及

将ASIC设计重新映射为FPGA设计。

36.根据权利要求35所述的方法,其中所述的映射包括:

生成ASIC网单及布局信息。

37.根据权利要求36所述的方法,其中所述的重映射是对所述的FPGA网单及布局信息执行的。

38.根据权利要求35所述的方法,其中所述的重映射包括:

产生FPGA网单及布局信息。

39.根据权利要求37所述的方法,其中所述的重映射包括:

生成FPGA网单及布局信息。

40.利用权利要求35所述的方法制造的FPGA。

41.根据权利要求35所述的方法,其中所述的映射包括:

利用彼此相邻的多个HLE来实现单个HLE所不能实现的任意LE的功能。

42.根据权利要求41所述的方法,其中所述的映射还包括:

记录哪些HLE被一起使用来实现单个HLE所不能实现的任意LE的功能。

43.根据权利要求42所述的方法,其中所述的重映射还包括:

利用所述的记录来识别HLE组以重映射为各个LE。

44.根据权利要求35所述的方法,其中所述的映射包括:

在利用HLE实现至少一部分FPGA LE的功能时,运用逻辑删减。

45.根据权利要求35所述的方法,其中所述的映射包括:

将每个FPGA LE的(1)逻辑功能及(2)寄存器功能进一步映射到各个不同的HLE或HLE组。

46.一种在功能上等效于一个已编程FPGA的ASIC,其中包括:

多个HLE,每个HLE在被充分利用的情况下也只能实现FPGA中一个被充分利用的LE的一部分功能,每个所述LE的功能被映射到相应一个HLE或HLE组。

47.逻辑单元电路,其组合逻辑能力主要包括单输入查找表电路以及两个二输入NAND门或是这类NAND门的逻辑等效电路。

48.根据权利要求47所述的电路,其中所述的查找表电路包括:

具有两个可选输入端以及一个选择控制输入端的多路选择器电路。

49.根据权利要求47所述的电路,还包括:

可编程互连线电路,用于可选择地将信号引入、引出所述的查找表电路及NAND门或是它们的逻辑等效电路,以及在所述电路之间传递信号。

50.根据权利要求47所述的电路,还包括:

输出缓冲器电路。

51.根据权利要求50所述的电路,还包括:

可编程互连线电路,用于可选择地将所述查找表电路或至少一个NAND门或所述逻辑等效电路的输出信号加载到所述输出缓冲器电路上。

52.根据权利要求49所述的电路,其中所述的可编程互连线电路至少是部分掩膜可编程的。

53.根据权利要求49所述的电路,其中所述的可编程互连线电路至少是部分通孔可编程的。

54.一种包括多个逻辑单元电路的ASIC,每个逻辑单元电路与权利要求47所述的一样。

55.根据权利要求54所述的ASIC,一个功能上等效的FPGA中的每个逻辑单元的所有功能都由所述的相应一个逻辑单元电路或是逻辑单元电路组实现。

56.一种包括HLE的结构化ASIC,其中所述的结构化ASIC能实现能被综合为FPGA LE的逻辑。

57.根据权利要求56所述的结构化ASIC,其中所述的逻辑被映射为LE,再被重映射回HLE。

58.根据权利要求56所述的结构化ASIC,其中所述的每个LE的全部功能都由HLE单独或组合完成。

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| US10/884,460 US7243329B2 (en) | 2004-07-02 | 2004-07-02 | Application-specific integrated circuit equivalents of programmable logic and associated methods |

| US10/884,460 | 2004-07-02 |

Publications (1)

| Publication Number | Publication Date |

|---|---|

| CN1716781A true CN1716781A (zh) | 2006-01-04 |

Family

ID=34993053

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| CN 200510072989 Pending CN1716781A (zh) | 2004-07-02 | 2005-05-25 | 可编程逻辑的专用集成电路等价实现及相关方法 |

Country Status (4)

| Country | Link |

|---|---|

| US (5) | US7243329B2 (zh) |

| EP (1) | EP1612940A3 (zh) |

| JP (5) | JP5036146B2 (zh) |

| CN (1) | CN1716781A (zh) |

Cited By (3)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN103155414A (zh) * | 2010-08-06 | 2013-06-12 | 阿尔特拉公司 | 硬化的可编程器件 |

| CN101272141B (zh) * | 2007-03-21 | 2015-11-25 | 阿尔特拉公司 | 交错逻辑阵列块结构 |

| CN105281892A (zh) * | 2014-06-03 | 2016-01-27 | 英派尔科技开发有限公司 | 现场可编程门阵列码的微扰以防止边信道攻击 |

Families Citing this family (32)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US7373631B1 (en) * | 2004-08-11 | 2008-05-13 | Altera Corporation | Methods of producing application-specific integrated circuit equivalents of programmable logic |

| US7392498B1 (en) * | 2004-11-19 | 2008-06-24 | Xilinx, Inc | Method and apparatus for implementing a pre-implemented circuit design for a programmable logic device |

| US7441223B1 (en) * | 2005-01-07 | 2008-10-21 | Altera Corporation | Method and apparatus for performing synthesis to improve density on field programmable gate arrays |

| US7620924B2 (en) * | 2005-03-14 | 2009-11-17 | Lsi Corporation | Base platforms with combined ASIC and FPGA features and process of using the same |

| US7275232B2 (en) * | 2005-04-01 | 2007-09-25 | Altera Corporation | Methods for producing equivalent field-programmable gate arrays and structured application specific integrated circuits |

| US7304497B2 (en) * | 2005-04-29 | 2007-12-04 | Altera Corporation | Methods and apparatus for programmably powering down structured application-specific integrated circuits |

| US7404169B2 (en) | 2005-05-31 | 2008-07-22 | Altera Corporation | Clock signal networks for structured ASIC devices |

| US7386819B1 (en) | 2005-07-28 | 2008-06-10 | Altera Corporation | Methods of verifying functional equivalence between FPGA and structured ASIC logic cells |

| US7373630B1 (en) | 2005-12-12 | 2008-05-13 | Altera Corporation | Methods for improved structured ASIC design |

| US8037444B1 (en) | 2006-07-20 | 2011-10-11 | Altera Corporation | Programmable control of mask-programmable integrated circuit devices |

| US7587686B1 (en) | 2006-08-01 | 2009-09-08 | Altera Corporation | Clock gating in a structured ASIC |

| US7472370B1 (en) | 2006-08-11 | 2008-12-30 | Xilinx, Inc. | Comparing graphical and netlist connections of a programmable logic device |

| US7584448B1 (en) * | 2006-08-11 | 2009-09-01 | Xilinx, Inc. | Constructing a model of a programmable logic device |

| US7451424B1 (en) | 2006-08-11 | 2008-11-11 | Xilinx, Inc. | Determining programmable connections through a switchbox of a programmable logic device |

| US7451423B1 (en) | 2006-08-11 | 2008-11-11 | Xilinx, Inc. | Determining indices of configuration memory cell modules of a programmable logic device |

| US7536668B1 (en) | 2006-08-11 | 2009-05-19 | Xilinx, Inc. | Determining networks of a tile module of a programmable logic device |

| US7451425B1 (en) | 2006-08-11 | 2008-11-11 | Xilinx, Inc. | Determining controlling pins for a tile module of a programmable logic device |

| US7451420B1 (en) | 2006-08-11 | 2008-11-11 | Xilinx, Inc. | Determining reachable pins of a network of a programmable logic device |

| US7478359B1 (en) | 2006-10-02 | 2009-01-13 | Xilinx, Inc. | Formation of columnar application specific circuitry using a columnar programmable logic device |

| US7589555B1 (en) * | 2007-01-08 | 2009-09-15 | Altera Corporation | Variable sized soft memory macros in structured cell arrays, and related methods |

| JP2008192967A (ja) * | 2007-02-07 | 2008-08-21 | Elpida Memory Inc | 半導体装置及びその配線切り替えオプション |

| US7924052B1 (en) | 2008-01-30 | 2011-04-12 | Actel Corporation | Field programmable gate array architecture having Clos network-based input interconnect |

| US7586327B1 (en) | 2008-03-25 | 2009-09-08 | Altera Corporation | Distributed memory circuitry on structured application-specific integrated circuit devices |

| US7622952B1 (en) | 2008-05-28 | 2009-11-24 | Altera Corporation | Periphery clock signal distribution circuitry for structured ASIC devices |

| JP5453850B2 (ja) * | 2009-03-06 | 2014-03-26 | 富士通セミコンダクター株式会社 | 半導体集積回路 |

| US8878566B2 (en) | 2010-09-08 | 2014-11-04 | Nec Corporation | Reconfigurable circuit |

| WO2012047735A2 (en) * | 2010-09-29 | 2012-04-12 | The Regents Of The University Of California | In-place resynthesis and remapping techniques for soft error mitigation in fpga |

| US8533641B2 (en) | 2011-10-07 | 2013-09-10 | Baysand Inc. | Gate array architecture with multiple programmable regions |

| US20180062654A9 (en) * | 2011-11-30 | 2018-03-01 | Agate Logic Inc. | Method and apparatus for facilitating communication between programmable logic circuit and application specific integrated circuit with clock adjustment |

| US20160239313A1 (en) * | 2013-11-08 | 2016-08-18 | Empire Technology Development Llc | Control of router in cloud system |

| US10394991B2 (en) | 2016-10-06 | 2019-08-27 | Altera Corporation | Methods and apparatus for dynamically configuring soft processors on an integrated circuit |

| US10353709B2 (en) * | 2017-09-13 | 2019-07-16 | Nextera Video, Inc. | Digital signal processing array using integrated processing elements |

Family Cites Families (53)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US5451887A (en) * | 1986-09-19 | 1995-09-19 | Actel Corporation | Programmable logic module and architecture for field programmable gate array device |

| US4910417A (en) * | 1986-09-19 | 1990-03-20 | Actel Corporation | Universal logic module comprising multiplexers |

| JPH03139863A (ja) * | 1989-10-25 | 1991-06-14 | Hitachi Ltd | 半導体集積回路 |

| JPH046913A (ja) * | 1990-04-24 | 1992-01-10 | Kawasaki Steel Corp | プログラマブル論理素子 |

| US5068547A (en) * | 1990-09-05 | 1991-11-26 | Lsi Logic Corporation | Process monitor circuit |

| US5717928A (en) * | 1990-11-07 | 1998-02-10 | Matra Hachette Sa | System and a method for obtaining a mask programmable device using a logic description and a field programmable device implementing the logic description |

| US5122685A (en) * | 1991-03-06 | 1992-06-16 | Quicklogic Corporation | Programmable application specific integrated circuit and logic cell therefor |

| JPH05252025A (ja) * | 1991-10-28 | 1993-09-28 | Texas Instr Inc <Ti> | 論理モジュールおよび集積回路 |

| JPH06176102A (ja) * | 1992-10-09 | 1994-06-24 | Ricoh Co Ltd | ゲートアレイ用ネットリスト発生装置 |

| US5550839A (en) | 1993-03-12 | 1996-08-27 | Xilinx, Inc. | Mask-programmed integrated circuits having timing and logic compatibility to user-configured logic arrays |

| JPH0785115A (ja) * | 1993-09-10 | 1995-03-31 | Toshiba Corp | 論理回路の検査用データ収集装置及び検査用データ収集方法 |

| KR960002333B1 (ko) * | 1993-12-23 | 1996-02-16 | 재단법인한국전자통신연구소 | 논리 집적회로 모듈 |

| TW396312B (en) * | 1993-12-30 | 2000-07-01 | At & T Corp | Method and apparatus for converting field-programmable gate array implementations into mask-programmable logic cell implementations |

| US5502402A (en) * | 1995-01-05 | 1996-03-26 | Texas Instruments Incorporated | FPGA architecture based on a single configurable logic module |

| US5671432A (en) * | 1995-06-02 | 1997-09-23 | International Business Machines Corporation | Programmable array I/O-routing resource |

| JP3072888B2 (ja) * | 1995-12-14 | 2000-08-07 | 川崎製鉄株式会社 | フィールドプログラマブルゲートアレイ |

| US5841295A (en) * | 1996-02-09 | 1998-11-24 | Hewlett-Packard Company | Hybrid programmable logic device |

| US5894565A (en) | 1996-05-20 | 1999-04-13 | Atmel Corporation | Field programmable gate array with distributed RAM and increased cell utilization |

| US5825202A (en) | 1996-09-26 | 1998-10-20 | Xilinx, Inc. | Integrated circuit with field programmable and application specific logic areas |

| US5963050A (en) * | 1997-02-26 | 1999-10-05 | Xilinx, Inc. | Configurable logic element with fast feedback paths |

| US5874834A (en) | 1997-03-04 | 1999-02-23 | Xilinx, Inc. | Field programmable gate array with distributed gate-array functionality |

| JPH10320451A (ja) * | 1997-05-21 | 1998-12-04 | Hitachi Telecom Technol Ltd | ゲートアレイ用ネットデータ作成方法 |

| US6097212A (en) * | 1997-10-09 | 2000-08-01 | Lattice Semiconductor Corporation | Variable grain architecture for FPGA integrated circuits |

| JP3123977B2 (ja) * | 1998-06-04 | 2001-01-15 | 日本電気株式会社 | プログラマブル機能ブロック |

| US6150838A (en) * | 1999-02-25 | 2000-11-21 | Xilinx, Inc. | FPGA configurable logic block with multi-purpose logic/memory circuit |

| EP1533904A1 (en) * | 1999-03-11 | 2005-05-25 | Easic Corporation | Integrated circuit technology |

| US6294926B1 (en) | 1999-07-16 | 2001-09-25 | Philips Electronics North America Corporation | Very fine-grain field programmable gate array architecture and circuitry |

| US6331790B1 (en) * | 2000-03-10 | 2001-12-18 | Easic Corporation | Customizable and programmable cell array |

| US6629294B2 (en) * | 2000-03-10 | 2003-09-30 | General Electric Company | Tool and method for improving the quality of board design and modeling |

| US6490707B1 (en) | 2000-07-13 | 2002-12-03 | Xilinx, Inc. | Method for converting programmable logic devices into standard cell devices |

| US6515509B1 (en) | 2000-07-13 | 2003-02-04 | Xilinx, Inc. | Programmable logic device structures in standard cell devices |

| US6526563B1 (en) | 2000-07-13 | 2003-02-25 | Xilinx, Inc. | Method for improving area in reduced programmable logic devices |

| WO2002093745A2 (en) * | 2001-05-16 | 2002-11-21 | Koninklijke Philips Electronics N.V. | Reconfigurable logic device |

| US6580289B2 (en) * | 2001-06-08 | 2003-06-17 | Viasic, Inc. | Cell architecture to reduce customization in a semiconductor device |

| US6769107B1 (en) * | 2001-12-03 | 2004-07-27 | Lsi Logic Corporation | Method and system for implementing incremental change to circuit design |

| US6911842B1 (en) * | 2002-03-01 | 2005-06-28 | Xilinx, Inc. | Low jitter clock for a physical media access sublayer on a field programmable gate array |

| JP2003273727A (ja) * | 2002-03-14 | 2003-09-26 | Shinji Kimura | 半導体集積回路装置 |

| KR100788112B1 (ko) * | 2002-04-17 | 2007-12-21 | 후지쯔 가부시끼가이샤 | Asic과 프로그래머블 로직 디바이스의 컨커런트 개발 방법 및 그 개발 시스템, 개발 프로그램을 기록한 기록 매체, 및 네트리스트 생성 방법 |

| US6759869B1 (en) * | 2002-06-05 | 2004-07-06 | Xilinx, Inc. | Large crossbar switch implemented in FPGA |

| US6873185B2 (en) * | 2002-06-19 | 2005-03-29 | Viasic, Inc. | Logic array devices having complex macro-cell architecture and methods facilitating use of same |

| US7064579B2 (en) * | 2002-07-08 | 2006-06-20 | Viciciv Technology | Alterable application specific integrated circuit (ASIC) |

| US7112994B2 (en) * | 2002-07-08 | 2006-09-26 | Viciciv Technology | Three dimensional integrated circuits |

| US7679398B2 (en) * | 2002-07-17 | 2010-03-16 | Osann Jr Robert | Reprogrammable instruction DSP |

| US7346876B2 (en) * | 2002-09-04 | 2008-03-18 | Darien K. Wallace | ASIC having dense mask-programmable portion and related system development method |

| US6829756B1 (en) * | 2002-09-23 | 2004-12-07 | Xilinx, Inc. | Programmable logic device with time-multiplexed interconnect |

| US6988258B2 (en) | 2002-12-09 | 2006-01-17 | Altera Corporation | Mask-programmable logic device with building block architecture |

| US6870395B2 (en) * | 2003-03-18 | 2005-03-22 | Lattice Semiconductor Corporation | Programmable logic devices with integrated standard-cell logic blocks |

| US7290237B2 (en) | 2003-06-23 | 2007-10-30 | Altera Corporation | Method for programming a mask-programmable logic device and device so programmed |

| US7038490B1 (en) * | 2003-09-12 | 2006-05-02 | Lattice Semiconductor Corporation | Delay-matched ASIC conversion of a programmable logic device |

| US7003746B2 (en) * | 2003-10-14 | 2006-02-21 | Hyduke Stanley M | Method and apparatus for accelerating the verification of application specific integrated circuit designs |

| US7019557B2 (en) * | 2003-12-24 | 2006-03-28 | Viciciv Technology | Look-up table based logic macro-cells |

| US7100142B2 (en) * | 2004-04-07 | 2006-08-29 | Synopsys, Inc. | Method and apparatus for creating a mask-programmable architecture from standard cells |

| US7081772B1 (en) | 2004-06-04 | 2006-07-25 | Altera Corporation | Optimizing logic in non-reprogrammable logic devices |

-

2004

- 2004-07-02 US US10/884,460 patent/US7243329B2/en not_active Expired - Fee Related

-

2005

- 2005-05-25 CN CN 200510072989 patent/CN1716781A/zh active Pending

- 2005-06-24 EP EP05253922A patent/EP1612940A3/en not_active Withdrawn

- 2005-07-01 JP JP2005193749A patent/JP5036146B2/ja not_active Expired - Fee Related

-

2007

- 2007-05-07 US US11/801,082 patent/US7870513B2/en not_active Expired - Fee Related

-

2010

- 2010-12-14 US US12/967,851 patent/US8291355B2/en not_active Expired - Fee Related

-

2012

- 2012-04-06 JP JP2012087199A patent/JP5475045B2/ja not_active Expired - Fee Related

- 2012-07-09 JP JP2012153545A patent/JP5623471B2/ja not_active Expired - Fee Related

- 2012-09-13 US US13/614,819 patent/US8504963B2/en active Active

-

2013

- 2013-07-31 US US13/955,200 patent/US8863061B2/en not_active Expired - Fee Related

-

2014

- 2014-04-11 JP JP2014081749A patent/JP2014131365A/ja not_active Withdrawn

- 2014-10-10 JP JP2014208874A patent/JP5859089B2/ja not_active Expired - Fee Related

Cited By (5)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| CN101272141B (zh) * | 2007-03-21 | 2015-11-25 | 阿尔特拉公司 | 交错逻辑阵列块结构 |

| CN103155414A (zh) * | 2010-08-06 | 2013-06-12 | 阿尔特拉公司 | 硬化的可编程器件 |

| US9654109B2 (en) | 2010-08-06 | 2017-05-16 | Altera Corporation | Hardened programmable devices |

| CN105281892A (zh) * | 2014-06-03 | 2016-01-27 | 英派尔科技开发有限公司 | 现场可编程门阵列码的微扰以防止边信道攻击 |

| CN105281892B (zh) * | 2014-06-03 | 2018-11-02 | 英派尔科技开发有限公司 | 现场可编程门阵列码的微扰以防止边信道攻击 |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1612940A2 (en) | 2006-01-04 |

| US20130314122A1 (en) | 2013-11-28 |

| US20070210827A1 (en) | 2007-09-13 |

| US8504963B2 (en) | 2013-08-06 |

| US8863061B2 (en) | 2014-10-14 |

| US7870513B2 (en) | 2011-01-11 |

| US8291355B2 (en) | 2012-10-16 |

| US20060001444A1 (en) | 2006-01-05 |

| EP1612940A3 (en) | 2007-08-22 |

| JP5475045B2 (ja) | 2014-04-16 |

| US20130002295A1 (en) | 2013-01-03 |

| JP2014131365A (ja) | 2014-07-10 |

| JP5623471B2 (ja) | 2014-11-12 |

| JP2015008539A (ja) | 2015-01-15 |

| US20110084727A1 (en) | 2011-04-14 |

| JP5859089B2 (ja) | 2016-02-10 |

| JP2012235499A (ja) | 2012-11-29 |

| JP5036146B2 (ja) | 2012-09-26 |

| US7243329B2 (en) | 2007-07-10 |

| JP2006020329A (ja) | 2006-01-19 |

| JP2012157054A (ja) | 2012-08-16 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| CN1716781A (zh) | 可编程逻辑的专用集成电路等价实现及相关方法 | |

| CN1124690C (zh) | 用于可缩放多层互联结构的平面布局图 | |

| CN1117432C (zh) | 可缩放的多层互联结构 | |

| CN1188948C (zh) | 用于配置可编程逻辑单元阵列的方法及装置 | |

| US8555218B2 (en) | Decision modules | |

| CN1841389B (zh) | 产生等效现场可编程门阵列和结构化专用集成电路的方法 | |

| Karplus | Amap: a technology mapper for selector-based field-programmable gate arrays | |

| CN1194702A (zh) | 具有分布ram并提高了单元利用率的现场可编程门阵列 | |

| CN1845461A (zh) | 用于产生和扩展结构化asic逻辑库和其他功能的方法 | |

| CN1125006A (zh) | 动态互连于一个动态逻辑内核的现场可编程逻辑设备 | |

| CN1101082C (zh) | 用于可编程逻辑电路的结构和互连方案 | |

| CN1992071A (zh) | 现场可编程门阵列集成电路器件的分布式存储器 | |

| US6941540B2 (en) | Design method for gate array integrated circuit | |

| CN1862968A (zh) | 电路布置以及设计电路布置的方法 | |

| CN1203706A (zh) | 一种半导体集成电路 | |

| US8046729B1 (en) | Method and apparatus for composing and decomposing low-skew networks | |

| Small | The flexibility of the quicklogic FPGA architecture | |

| Anderson | Architectures and algorithms for laser-programmed gate arrays with foldable logic blocks | |

| Mayerhofer | Shapeshifter: a parameterisable Field-Programmable Gate Array |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| C06 | Publication | ||

| PB01 | Publication | ||

| C10 | Entry into substantive examination | ||

| SE01 | Entry into force of request for substantive examination | ||

| C02 | Deemed withdrawal of patent application after publication (patent law 2001) | ||

| WD01 | Invention patent application deemed withdrawn after publication |

Open date: 20060104 |