EP0604423B1 - Method for writing data to an electrophoretic display panel - Google Patents

Method for writing data to an electrophoretic display panel Download PDFInfo

- Publication number

- EP0604423B1 EP0604423B1 EP92904723A EP92904723A EP0604423B1 EP 0604423 B1 EP0604423 B1 EP 0604423B1 EP 92904723 A EP92904723 A EP 92904723A EP 92904723 A EP92904723 A EP 92904723A EP 0604423 B1 EP0604423 B1 EP 0604423B1

- Authority

- EP

- European Patent Office

- Prior art keywords

- line

- written

- lines

- writing

- time period

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Expired - Lifetime

Links

Images

Classifications

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G3/00—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes

- G09G3/20—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters

- G09G3/34—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source

- G09G3/3433—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using light modulating elements actuated by an electric field and being other than liquid crystal devices and electrochromic devices

- G09G3/344—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using light modulating elements actuated by an electric field and being other than liquid crystal devices and electrochromic devices based on particles moving in a fluid or in a gas, e.g. electrophoretic devices

- G09G3/3446—Control arrangements or circuits, of interest only in connection with visual indicators other than cathode-ray tubes for presentation of an assembly of a number of characters, e.g. a page, by composing the assembly by combination of individual elements arranged in a matrix no fixed position being assigned to or needed to be assigned to the individual characters or partial characters by control of light from an independent source using light modulating elements actuated by an electric field and being other than liquid crystal devices and electrochromic devices based on particles moving in a fluid or in a gas, e.g. electrophoretic devices with more than two electrodes controlling the modulating element

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2300/00—Aspects of the constitution of display devices

- G09G2300/06—Passive matrix structure, i.e. with direct application of both column and row voltages to the light emitting or modulating elements, other than LCD or OLED

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2310/00—Command of the display device

- G09G2310/02—Addressing, scanning or driving the display screen or processing steps related thereto

- G09G2310/0202—Addressing of scan or signal lines

- G09G2310/0205—Simultaneous scanning of several lines in flat panels

- G09G2310/021—Double addressing, i.e. scanning two or more lines, e.g. lines 2 and 3; 4 and 5, at a time in a first field, followed by scanning two or more lines in another combination, e.g. lines 1 and 2; 3 and 4, in a second field

-

- G—PHYSICS

- G09—EDUCATION; CRYPTOGRAPHY; DISPLAY; ADVERTISING; SEALS

- G09G—ARRANGEMENTS OR CIRCUITS FOR CONTROL OF INDICATING DEVICES USING STATIC MEANS TO PRESENT VARIABLE INFORMATION

- G09G2320/00—Control of display operating conditions

- G09G2320/06—Adjustment of display parameters

Definitions

- the present invention relates to a method for operating an electrophoretic display panel apparatus and, more particularly, to a method which increases the speed with which information can be written to an electrophoretic display panel.

- Electrophoretic displays are now well known. A variety of display types and features are taught in several patents issued in the names of Frank J. DiSanto and Denis A. Krusos and assigned to the assignee herein, Copytele, Inc. of Huntington Station, New York. For example, U.S Patent Nos. 4,655,897 and 4,732,830, each entitled ELECTROPHORETIC DISPLAY PANELS AND ASSOCIATED METHODS describe the basic operation and construction of an electrophoretic display. U.S. Patent No. 4,742,345, entitled ELECTROPHORETIC DISPLAY PANELS AND METHODS THEREFOR, describes a display having improved alignment and contrast. U.S. Patent No.

- the display panels shown in the abovementioned patents operate upon the same basic principle, viz., if a suspension of electrically charged pigment particles in a dielectric fluid is subjected to an applied electrostatic field, the pigment particles will migrate through the fluid in response to the electrostatic field. Given a substantially homogeneous suspension of particles having a pigment color different from that of the dielectric fluid, if the applied electrostatic field is localized, it will cause a visually observable localized pigment particle migration. The localized pigment particle migration results either in a localized area of concentration or rarefaction of particles depending upon the sign and direction of the electrostatic field and the charge on the pigment particles.

- Patents are "triode-type" displays having a plurality of independent, parallel, cathode row conductor elements or "lines” deposited in the horizontal on one surface of a glass viewing screen.

- a glass cap member forms a fluid-tight seal with the viewing window along the cap's peripheral edge for containing the fluid suspension and also acts as a substrate for an anode plate deposited on the interior flat surface of the cap.

- the anode surface is in spaced parallel relation to both the cathode elements and the grid elements.

- the cathode element voltage, the anode voltage, and the grid element voltage can then be ascertained such that when a particular voltage is applied to the cathode and another voltage is applied to the grid, the area proximate their intersection will assume a net charge sufficient to attract or repel pigment particles in suspension in the dielectric fluid. Since numerous cathode and grid lines are employed, there are numerous discrete intersection points which can be controlled by varying the voltage on the cathode and grid elements to cause localized visible regions of pigment concentration and rarefaction.

- the operating voltages on both cathode and grid must be able to assume at least two states corresponding to a logical one and a logical zero.

- Logical one for the cathode may either correspond to attraction or repulsion of pigment.

- the cathode and grid voltages are selected such that only when both are a logical one at a particular intersection point, will a sufficient electrostatic field be present at the intersection relative to the anode to cause the writing of a visual bit of information on the display through migration of pigment particles.

- the bit may be erased, e.g., upon a reversal of polarity and a logical zero-zero state occurring at the intersection coordinated with an erase voltage gradient between anode and cathode. In this manner, digitized data can be displayed on the electrophoretic display.

- a computer with a visual output device for displaying character information such as a CRT

- the writing and erasure of displayed information is not fast enough, it will slow the operator of the word processor in the completion of his task.

- the computer memory and processing unit can operate at speeds far exceeding the capacity of a human user, if the input and output devices through which the computer communicates with the user are slow, the computer and the user must wait for the output devices. Thus, if a word processor user is paging through a document at high speed, a slow visual output device may well slow the speed of paging below that at which the user and/or the computer could potentially perform.

- one factor which contributes to the speed with which the display can operate is the speed with which the pigment particles can travel through the electrophoretic fluid under the influence of a particular voltage gradient.

- Pigment particle migration speed depends, inter alia, upon particle size and electrophoretic fluid viscosity.

- particle speed there is also the factor of spatial distribution within the EPID envelope, i.e., because the particles are in suspension they are distributed, prior to being exposed to voltage gradients, relatively evenly within the fluid envelope. Accordingly, there is a range of particle proximity to the "target" element, the target element being that element to which the particles are sought to be directed to perform an operation, such as write or erase.

- FIG. 1 is a cross-sectional view of a typical triode-type EPID showing the essential electrical components thereof.

- FIG. 2 is a simplified schematic diagram illustrating an addressable display matrix comprised of horizontal and vertical elements, such as, a plurality of cathode lines and a plurality of grid lines, driven by display drivers, as would be used in known EPID devices like that shown in FIG. 1.

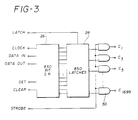

- FIG. 3 is a simplified schematic diagram illustrating circuitry for controlling the x and y display drivers illustrated in FIG. 2.

- FIG. 4 shows a character which could be displayed upon an x-y matrix using the circuitry and apparatus as illustrated in FIGS. 1-3, as controlled and operated in accordance with the method of the present invention.

- FIG. 5 is a flowchart showing a method for EPID writing in accordance with the present invention.

- FIG. 1 which is taken from U.S. Patent No. 4,732,830, shows an electrophoretic display 10 as is now known in the art.

- the display 10 has an anode faceplate 12 and a cathode faceplate 14 which are sealably affixed on either side of an interstitial spacer (not shown) to form a fluid-tight envelope for containing a dielectric/pigment particle suspension or electrophoretic fluid.

- the faceplates 12 and 14 are typically flat glass plates upon which are deposited conductor elements to comprise the situs of electrostatic charge for inducing motion of the pigment particles 16 in the electrophoretic fluid.

- the techniques, materials and dimensions used to form the conductor elements upon the faceplates and the methods for making and using EPIDS, in general, are shown in U.S. Patent Nos. 4,655,897, 4,732,830 and 4,742,345.

- EPIDS as depicted in FIG. 1, for example, have a plurality of independent, electrically conductive cathode lines 18, shown here as horizontal rows, deposited upon the cathode faceplate 14 using conventional deposition and etching techniques.

- the orientation of the cathode lines 18 depends upon the orientation of the screen, which, if rotated 90 degrees, would position the cathode lines vertically.

- the cathode lines are arbitrarily defined as horizontal or in the x-axis.

- the cathode elements 18 be composed of Indium Tin Oxide (ITO) as set forth in U.S. Patent No. 4,742,345.

- ITO Indium Tin Oxide

- a plurality of independent grid conductor lines 20 are superposed in the vertical (parallel with the ⁇ -axis) over the cathode elements 18. i.e. at right angles thereto, and are insulated therefrom by an interstitial photoresist layer 22.

- the grid elements 20 may be formed by coating the photoresist layer 22 with a metal, such as nickel or chrome, using sputtering techniques or the like, and then selectively masking and etching to yield the intersecting but insulated configuration shown in FIG. 1.

- Each cathode and grid element 18, 20 terminates at one end in a contact pad, or is otherwise adapted to permit connection to display driver circuitry.

- An anode 26 is formed on an interior surface of the anode faceplate 12 by plating with a thin layer of conductor material, such as, chrome.

- FIG. 2 also taken from U.S. Patent No. 4,732,830, shows, in the simplest schematic form, how the cathode 18 and grid lines 20 comprise an addressable x-y matrix allowing pixels at the intersection points to be selectively displayed.

- Each horizontal 18 and vertical 20 line has an associated amplifer/driver 24R and 24C, respectively, for impressing either a logical "1" or "0" thereon, such that when both are "1" at an intersection, that intersection is written.

- the horiziontal lines have been labelled R1...R2200 to signify that 2200 display lines 18 or rows would typically be present.

- 1700 vertical lines 20 or columns are common, as depicted by the labels C1...C1700.

- FIG. 3, taken from Patent No. 4,742,345, shows exemplary circuitry for suplying input data to the x and y drivers, 24R and 24C.

- a large capacity, composite, serial-to-parallel register 26 may be used as a buffer for collecting a large number of bits of display data, e.g. 850 bits. After sequentially clocking data into the register 26 and filling it to capacity, the data is latched in parallel into a latch array 28 having an equal capacity. The data is then strobed into the display driver amplifiers 24 through a plurality of AND gates 30. Data may be accumulated in the serial register while the transfer from latch array 28 to drivers 24 occurs.

- FIG. 4 shows exemplary circuitry for suplying input data to the x and y drivers, 24R and 24C.

- a large capacity, composite, serial-to-parallel register 26 may be used as a buffer for collecting a large number of bits of display data, e.g. 850 bits. After sequentially clocking data into

- the output of the AND gates are labelled with odd number columns 1 through 1699.

- the data for even number columns would be supplied, in this case, by a twin circuit disposed on the cathode faceplate opposite to that for the odd columns. This configuration prevents overcrowding of electrical connections to the grid lines as explained in Patent No. 4,742,345.

- FIGS. 1 and 2 The proportions of the grid 20 and cathode 18 lines as shown in FIGS. 1 and 2 have been greatly enlarged for the purposes of illustration.

- the grid 20 and cathode 18 lines are very thin and elongated.

- a workable panel would have a large number of intersections, e.g., 2,200 X 1,700 or a total of 3,740,000 separately addressable intersection points in a panel approximately 8" X 11".

- cathode lines 18, and grid lines 20 are depicted. Additional illustrations of electrophoretic displays, their components and electrical circuitry can be seen by referring to U.S. Patents Nos. 4,742,345 and 4,772,820, each being awarded to the inventors herein.

- FIG. 4 illustrates a character, i.e. the letter "T" written on a EPID as described above in reference to FIGS. 1-3 by utilizing the algorithm flow chartered in FIG. 5.

- the writing time of the EPID can be reduced by simultaneously writing more than one line at a time. That is, in the above-described previously known EPIDS, an entire set of column data for a particular row is impressed upon the columns, e.g. the grid lines. A single row is then enabled with a logica "1" and thereby written. The next set of column data is loaded onto the grid lines and the next row is enabled or written. This goes on sequentially until the entire screen is written.

- each row in pas operation had to be held in the logical "1" state for the required writing period or writing cycle time.

- a set of rows greater than one row e.g., two rows

- the two rows will both be dimly written with the same display information in one half the cycle time. For instance, if column data for row 1 is loaded and rows 1 and 2 are written, both row 1 and row 2 will be dimly written with row 1 display information.

- a 70 line X 25 line matrix with 1750 pixels may be used as the area for expressing a single character.

- the pattern of pixels comprising the common characters is very repetitive.

- Fig. 4 illustrates this principle using a matrix of only 22 X 22 lines, i.e., those lines centrally located within the entire 29 X 31 line matrix depicted.

- the top of the "T” begins at (r5,c5) and ends at (r9,c26). The significance of the X's on row 5 will be explained below.

- the stem of the "T” starts at (r10,c13) and ends at (r26,c17).

- the top of the "T” is composed of 5 identical rows of pixels and the stem of the "T” is composed of 17 identical rows of pixels.

- the "T” depicted in FIG. 4 is an example of applying the present inventive method in writing in two row sets at one half the normal write cycle time (twice the writing speed). Specifically, one would execute the following steps in order to display the "T" shown in FIG. 4.:

- r5 has been selected as the first line that has "ls" or written pixels in it and it should be the first line of the "top" of the "T". Due to the fact, however, that r5 is a transition line, i.e., a transition from non-written to written pixels, it will not be completely written and instead will only be dimly written or half written. This is so because each write cycle, since it is at twice the speed as a normal cycle, only "half writes” the information. The next cycle is necessary to fully write the information, but only if the next cycle uses the same data. In the case of a transition line, succeeding rows have different data.

- Load r10 Write r10,r11 repeats until row 26 where: Load r26 Write r26,r27 (constitutes another transition line) Write r27, r28, etc. Load r27

- FIG. 5 is a generalized flowchart of the steps of the present inventive method for operating an EPID in a multi-line write mode. It would be expected that operator selection of display writing speed would be offered so that the operator can choose the speed and clarity. This sort of selection is presently offered to operators upon printing on dot-matrix printers, i.e. enhanced printing has greater pixel density but takes longer to print. Accordingly, the operator first enters the number of lines to be written in each write cycle 32. From, this input the write cycle time (writing speed) is adjusted 34. The greater the number of lines simultaneously written in each write cycle, the faster the writing speed.

- the operator input could be expressed as a selection of writing speed, wherein the operator would select from a range of speeds corresponding to the number of lines simultaneously written.

- the flowchart shown in FIG. 5 pertains to the display of a single complete image (frame) on the EPID. This algorithm would be utilized over and over under the control of programming at the next higher level. The operator would not be queried as to the operating speed on each frame displayed. Information of that type would be initially set by query or default then changed by interrupt if desired. Having determined the line set size for writing, the writing is begun at the first row 36. (Of course, it would be equally feasible to load rows with data and write columns.) The processor then enters a loop wherein data for the current row is loaded onto the column lines (here grid lines) 38.

- the data is simultaneously written on the current row and the next x-1 rows by enabling those rows with a logical "1" 40, x being the number of rows in the write set selected.

- row 1 and the next (4-1) or 3 rows i.e., rows 2, 3 and 4 are written.

- the "1" state may correspond to a variety of voltages depending upon the EPID in question, e.g., whether the EPID is a triode or tetrode. A voltage of 0 volts has been used to enable writing in triodes and, in those instances, represent a logical "1" or enable state.

- the row set is written for a write cycle time that has been adjusted by the size of the row set (divided by). This is continued until all rows are written 42,44, whereupon control is returned to the next higher level in the program.

- line writing sequences could be employed using a multi-line write strategy, for example, vertical lines can be written from left to right or right to left, horizontal lines could be written from bottom to top or from the middle to the outer periphery, etc.

Abstract

Description

- The present invention relates to a method for operating an electrophoretic display panel apparatus and, more particularly, to a method which increases the speed with which information can be written to an electrophoretic display panel.

- Electrophoretic displays (EPIDS) are now well known. A variety of display types and features are taught in several patents issued in the names of Frank J. DiSanto and Denis A. Krusos and assigned to the assignee herein, Copytele, Inc. of Huntington Station, New York. For example, U.S Patent Nos. 4,655,897 and 4,732,830, each entitled ELECTROPHORETIC DISPLAY PANELS AND ASSOCIATED METHODS describe the basic operation and construction of an electrophoretic display. U.S. Patent No. 4,742,345, entitled ELECTROPHORETIC DISPLAY PANELS AND METHODS THEREFOR, describes a display having improved alignment and contrast. U.S. Patent No. 4,833,464 entitled ELECTROPHORETIC INFORMATION DISPLAY (EPID) APPARATUS EMPLOYING GREY SCALE CAPABILITY relates to an EPID with the capability to display pixels of varying grey scale intensity. This patent recognizes, inter alia, that the duration of application of a voltage gradient at a particular pixel location effects the quantity of pigment particles at that location. Hence, by controlling the time duration of the write pulse one can achieve grey scale capability - the shorter the pulse, the lighter the line.

- The display panels shown in the abovementioned patents operate upon the same basic principle, viz., if a suspension of electrically charged pigment particles in a dielectric fluid is subjected to an applied electrostatic field, the pigment particles will migrate through the fluid in response to the electrostatic field. Given a substantially homogeneous suspension of particles having a pigment color different from that of the dielectric fluid, if the applied electrostatic field is localized, it will cause a visually observable localized pigment particle migration. The localized pigment particle migration results either in a localized area of concentration or rarefaction of particles depending upon the sign and direction of the electrostatic field and the charge on the pigment particles. The electrophoretic display apparatus taught in the foregoing U.S. Patents are "triode-type" displays having a plurality of independent, parallel, cathode row conductor elements or "lines" deposited in the horizontal on one surface of a glass viewing screen. A layer of insulating photoresist material deposited over the cathode elements and photoetched down to the cathode elements to yield a plurality of insulator strips positioned at right angles to the cathode elements, forms the substrate for a plurality of independent, parallel column or grid conductor elements or "lines" running in the vertical direction. A glass cap member forms a fluid-tight seal with the viewing window along the cap's peripheral edge for containing the fluid suspension and also acts as a substrate for an anode plate deposited on the interior flat surface of the cap. When the cap is in place, the anode surface is in spaced parallel relation to both the cathode elements and the grid elements. Given a specific particulate suspension, the sign of the electrostatic charge which will attract and repel the pigment particles will be known. The cathode element voltage, the anode voltage, and the grid element voltage can then be ascertained such that when a particular voltage is applied to the cathode and another voltage is applied to the grid, the area proximate their intersection will assume a net charge sufficient to attract or repel pigment particles in suspension in the dielectric fluid. Since numerous cathode and grid lines are employed, there are numerous discrete intersection points which can be controlled by varying the voltage on the cathode and grid elements to cause localized visible regions of pigment concentration and rarefaction. Essentially then, the operating voltages on both cathode and grid must be able to assume at least two states corresponding to a logical one and a logical zero. Logical one for the cathode may either correspond to attraction or repulsion of pigment. Typically, the cathode and grid voltages are selected such that only when both are a logical one at a particular intersection point, will a sufficient electrostatic field be present at the intersection relative to the anode to cause the writing of a visual bit of information on the display through migration of pigment particles. The bit may be erased, e.g., upon a reversal of polarity and a logical zero-zero state occurring at the intersection coordinated with an erase voltage gradient between anode and cathode. In this manner, digitized data can be displayed on the electrophoretic display.

- An alternative EPID construction is described in Application No. 07/345,825 entitled DUAL ANODE FLAT PANEL DISPLAY APPARATUS and filed on May 1, 1989 for the assignee herein, which relates to an electrophoretic display in which the cathode/grid matrix as is found in triode-type displays is overlayed by a plurality of independent separately addressable "local" anode lines. The local anode lines are deposited upon and aligned with the grid lines and are insulated therefrom by interstitial lines of photoresist. The local anode lines are in addition to the "remote" anode, which is the layer deposited upon the anode faceplate or cap as in triode displays. The dual anode structure aforesaid provides enhanced operation by eliminating unwanted variations in display brightness between frames, increasing the speed of the display and decreasing the anode voltage required during Write and Hold cycles, all as explained in Application No. 07/345,825.

- A commonly sought objective for EPIDS of both triode and tetrode types, and for digital display equipment and computer and digital apparatus in general, is increased speed of operation. With respect to displays, it is desirable for the display to be able to write, erase and edit the displayed image as quickly as possible in response to operator input and computer processing. For example, when a computer with a visual output device for displaying character information, such as a CRT, is used as a word processor, if the writing and erasure of displayed information is not fast enough, it will slow the operator of the word processor in the completion of his task. Even though the computer memory and processing unit can operate at speeds far exceeding the capacity of a human user, if the input and output devices through which the computer communicates with the user are slow, the computer and the user must wait for the output devices. Thus, if a word processor user is paging through a document at high speed, a slow visual output device may well slow the speed of paging below that at which the user and/or the computer could potentially perform.

- In EPIDS and in other display apparatus, because there are a plurality of pixels arranged on a coordinate grid or matrix, and because the pixels must be independently addressable, display operations are frequently conducted at the pixel level, e.g., each pixel is sequentially written to. Sequential operations are intrinsically time consuming, in that the prior operation must be completed before the subsequent can be started. Further, even though the writing of a single pixel can be done very quickly, there are such a large number that even a small write time is significant. A process for independently controlling individual pixel display whereby a degree of parallel display processing is accomplished is described, e.g., in U.S. Patent No. 4,742,345, wherein display information pertaining to an entire line of pixels, i.e., On or Off, is accumulated in an accumulator or register during a first phase, placed in parallel into a latch array in a second phase and placed in parallel on one of the coordinate grids in a third phase. Placing the display information onto one of the coordinate line sets, e.g., the grid lines which may be oriented in the vertical direction, has been termed "loading" the data on the grid. When the bits of information (voltages corresponding to logical "1" and "0") are placed or "loaded" on, e.g., all the vertical coordinate lines, a single horizontal line can be written by enabling that line, i.e., by placing a voltage corresponding to a logical "1" on that horizontal line. The operation of placing an enabling voltage upon the line to be written, in this case a horizontal cathode line, has been referred to as "writing the line". Of course, this line-by-line writing method also has a upper limit of speed.

- With respect to EPIDS, one factor which contributes to the speed with which the display can operate is the speed with which the pigment particles can travel through the electrophoretic fluid under the influence of a particular voltage gradient. Pigment particle migration speed depends, inter alia, upon particle size and electrophoretic fluid viscosity. In addition to the particle speed, there is also the factor of spatial distribution within the EPID envelope, i.e., because the particles are in suspension they are distributed, prior to being exposed to voltage gradients, relatively evenly within the fluid envelope. Accordingly, there is a range of particle proximity to the "target" element, the target element being that element to which the particles are sought to be directed to perform an operation, such as write or erase.

- These speed and proximity factors in EPIDS are utilized in U.S. Patent No. 4,833,464 to control pixel display intensity or grey scale. Namely, if a voltage gradient of shorter or longer duration is applied, fewer or greater particles will accumulate at the "target" electrode thereby affecting pixel intensity, i.e., the greater the number of particles, the greater the intensity. Note that pixel intensity is discernable at both sides of the typical EPID so that an intense accumulation of e.g., light colored particles, on one face of the EPID is accompanied by a correspondingly intense lack of light particles on the other face, which, in all probability, will appear dark due to the selection of a dark solution or background for the light colored particles. Thus writing a character on one faceplate of an EPID results in its reverse image being written on the other plate. The writing of a blank character may be termed selective character erasure.

- In US 4804951 there is disclosed a display in which alternate lines of a frame of display data are written by a first electrode scan, and the remaining lines are written by a second electrode scan. such that a second of a pair of adjacent lines can be written immediately sequentially, without having to wait for the first electrode scan to "flyback" before writing the second of the lines. However, it is still necessary to perform the same number of scans to write the entire display frame and hence there is no substantial saving in the overall time for writing the display frame.

- It is an objective of the present invention to provide a method for operating an EPID having any particular pigment particle size, electrophoretic fluid viscosity, electrode arrangement and operating voltage levels, such that the speed of operation is increased.

- The problems and disadvantages associated with conventional methods of operating electrophoretic displays are overcome by the present inventive method which enables a decrease in the time to write a frame of display data composed of a plurality of lines of displayable pixels on an electrophoretic display requiring a minimum time period for a line to be fully written.

- According to the invention we provide a method for decreasing the time period to write a frame of display data composed of a plurality of lines of displayable pixels, on a high line density electrophoretic display requiring a predetermined time period for a line to be fully written, said method comprising the steps of:

- (a) simultaneously writing a set of at least two adjacent lines with said display data in a first time period which is less than said predetermined time period for a line to be fully written;

- (b) shifting the elements of said line set such that said set includes at least one new line and at least one original line;

- (c) writing said shifted line set in a second time period which is less than said predetermined time period, following said step of shifting; and

- (d) repeating steps (b) and (c) until said frame is completely written.

- For a better understanding of the present invention, reference is made to the following detailed description of an exemplary embodiment considered in conjunction with the accompanying drawings, in which:

- FIG. 1 is a cross-sectional view of a typical triode-type EPID showing the essential electrical components thereof.

- FIG. 2 is a simplified schematic diagram illustrating an addressable display matrix comprised of horizontal and vertical elements, such as, a plurality of cathode lines and a plurality of grid lines, driven by display drivers, as would be used in known EPID devices like that shown in FIG. 1.

- FIG. 3 is a simplified schematic diagram illustrating circuitry for controlling the x and y display drivers illustrated in FIG. 2.

- FIG. 4 shows a character which could be displayed upon an x-y matrix using the circuitry and apparatus as illustrated in FIGS. 1-3, as controlled and operated in accordance with the method of the present invention.

- FIG. 5 is a flowchart showing a method for EPID writing in accordance with the present invention.

- FIG. 1, which is taken from U.S. Patent No. 4,732,830, shows an

electrophoretic display 10 as is now known in the art. Thedisplay 10 has ananode faceplate 12 and acathode faceplate 14 which are sealably affixed on either side of an interstitial spacer (not shown) to form a fluid-tight envelope for containing a dielectric/pigment particle suspension or electrophoretic fluid. Thefaceplates pigment particles 16 in the electrophoretic fluid. The techniques, materials and dimensions used to form the conductor elements upon the faceplates and the methods for making and using EPIDS, in general, are shown in U.S. Patent Nos. 4,655,897, 4,732,830 and 4,742,345. - Known EPIDS, as depicted in FIG. 1, for example, have a plurality of independent, electrically

conductive cathode lines 18, shown here as horizontal rows, deposited upon thecathode faceplate 14 using conventional deposition and etching techniques. Of course, the orientation of thecathode lines 18 depends upon the orientation of the screen, which, if rotated 90 degrees, would position the cathode lines vertically. Thus, the cathode lines are arbitrarily defined as horizontal or in the x-axis. It is preferred that thecathode elements 18 be composed of Indium Tin Oxide (ITO) as set forth in U.S. Patent No. 4,742,345. A plurality of independentgrid conductor lines 20 are superposed in the vertical (parallel with the γ-axis) over thecathode elements 18. i.e. at right angles thereto, and are insulated therefrom by aninterstitial photoresist layer 22. Thegrid elements 20 may be formed by coating thephotoresist layer 22 with a metal, such as nickel or chrome, using sputtering techniques or the like, and then selectively masking and etching to yield the intersecting but insulated configuration shown in FIG. 1. Each cathode andgrid element anode 26 is formed on an interior surface of theanode faceplate 12 by plating with a thin layer of conductor material, such as, chrome. - The foregoing components have been previously described in prior patent and applications of the present Applicants. In addition to these teachings, the benefits and operation of an EPID having a local anode have been recognised and described in Application No. 07/345,825 by the present Applicants. The present inventive method could find application in any of these disclosed devices.

- FIG. 2, also taken from U.S. Patent No. 4,732,830, shows, in the simplest schematic form, how the

cathode 18 andgrid lines 20 comprise an addressable x-y matrix allowing pixels at the intersection points to be selectively displayed. Each horizontal 18 and vertical 20 line has an associated amplifer/driver display lines 18 or rows would typically be present. 1700vertical lines 20 or columns are common, as depicted by the labels C1...C1700. - FIG. 3, taken from Patent No. 4,742,345, shows exemplary circuitry for suplying input data to the x and y drivers, 24R and 24C. As explained fully in patent No. 4,742,345, a large capacity, composite, serial-to-

parallel register 26 may be used as a buffer for collecting a large number of bits of display data, e.g. 850 bits. After sequentially clocking data into theregister 26 and filling it to capacity, the data is latched in parallel into alatch array 28 having an equal capacity. The data is then strobed into the display driver amplifiers 24 through a plurality of ANDgates 30. Data may be accumulated in the serial register while the transfer fromlatch array 28 to drivers 24 occurs. In FIG. 3 the output of the AND gates are labelled withodd number columns 1 through 1699. The data for even number columns would be supplied, in this case, by a twin circuit disposed on the cathode faceplate opposite to that for the odd columns. This configuration prevents overcrowding of electrical connections to the grid lines as explained in Patent No. 4,742,345. Once the column data is supplied to all columns, a row can then be written by sending a "1" along the row orcathode 18 to be written. The row "1" in combination with any column "1" will cause the writing of a pixel at the intersection thereof, i.e., a voltage gradient at that point sufficient to cause a visually observable migration and agglomeration ofpigment particles 16. - The proportions of the

grid 20 andcathode 18 lines as shown in FIGS. 1 and 2 have been greatly enlarged for the purposes of illustration. In operational displays, thegrid 20 andcathode 18 lines are very thin and elongated. A workable panel would have a large number of intersections, e.g., 2,200 X 1,700 or a total of 3,740,000 separately addressable intersection points in a panel approximately 8" X 11". For ease of illustration, only afew cathode lines 18, andgrid lines 20 are depicted. Additional illustrations of electrophoretic displays, their components and electrical circuitry can be seen by referring to U.S. Patents Nos. 4,742,345 and 4,772,820, each being awarded to the inventors herein. - FIG. 4 illustrates a character, i.e. the letter "T" written on a EPID as described above in reference to FIGS. 1-3 by utilizing the algorithm flow chartered in FIG. 5. In accordance with the present inventive method, it has been observed that the writing time of the EPID can be reduced by simultaneously writing more than one line at a time. That is, in the above-described previously known EPIDS, an entire set of column data for a particular row is impressed upon the columns, e.g. the grid lines. A single row is then enabled with a logica "1" and thereby written. The next set of column data is loaded onto the grid lines and the next row is enabled or written. This goes on sequentially until the entire screen is written. There is a certain period required for the pigment particles to migrate through the electrophoretic fluid to their "write" position, i.e., to make an agglomeration sufficient in size to be clearly visible. Therefore each row in pas operation had to be held in the logical "1" state for the required writing period or writing cycle time. In accordance with the present invention, if a set of rows greater than one row, e.g., two rows, is enabled simultaneously for a period approximately one-half as long in duration as was previously done, then the two rows will both be dimly written with the same display information in one half the cycle time. For instance, if column data for

row 1 is loaded androws 1 and 2 are written, bothrow 1 and row 2 will be dimly written withrow 1 display information. If new column data, i.e., for row 2, is loaded and the row set is shifted down one and written, i.e., row set 2 and 3 are written using row 2 data, the first row which was half-written will be left untouched. The second row, however, will be fully written assuming the new column data associated with row 2 is the same as that associated withrow 1. Row 3 is also dimly written with row 2 data. Thus, by partially writing subsequent overlapping row sets with shortened writing cycles, the entire display can be written much faster than if single rows are sequentially fully written. This row set writing strategy depends upon the fact that there is repetition in the pixel pattern from one row to the next. In fact, there is a high probability of that condition occurring. Because of high line density in the EPIDS in question, the number of lines comprising a single character is great. For example, a 70 line X 25 line matrix with 1750 pixels may be used as the area for expressing a single character. As such, the pattern of pixels comprising the common characters is very repetitive. Fig. 4 illustrates this principle using a matrix of only 22X 22 lines, i.e., those lines centrally located within the entire 29 X 31 line matrix depicted. The top of the "T" begins at (r5,c5) and ends at (r9,c26). The significance of the X's on row 5 will be explained below. The stem of the "T" starts at (r10,c13) and ends at (r26,c17). As can readily be seen, the top of the "T" is composed of 5 identical rows of pixels and the stem of the "T" is composed of 17 identical rows of pixels. The "T" depicted in FIG. 4 is an example of applying the present inventive method in writing in two row sets at one half the normal write cycle time (twice the writing speed). Specifically, one would execute the following steps in order to display the "T" shown in FIG. 4.: - Load c1-c29 with data for r1

(0,0,0,0,0,0,0,0.......0)

Write r1 and r2 simultaneously (put "1" on r1 and r2)

Load c1-c29 (the grid lines) with data for r2

(0,0,0,0,...0)

Write r2,r3

Load grid with r3 data

Write r3, r4

Load grid with r4 data

Write r4,r5 - Note: for the purposes of this example, r5 has been selected as the first line that has "ls" or written pixels in it and it should be the first line of the "top" of the "T". Due to the fact, however, that r5 is a transition line, i.e., a transition from non-written to written pixels, it will not be completely written and instead will only be dimly written or half written. This is so because each write cycle, since it is at twice the speed as a normal cycle, only "half writes" the information. The next cycle is necessary to fully write the information, but only if the next cycle uses the same data. In the case of a transition line, succeeding rows have different data. Since there are so many lines of pixels in operable displays, the loss of small numbers of transition lines and/or pixels does not cause a significant loss in readability. Returning now to the writing process:

Load grid with r5 data

(0,0,0,0,1,1, 1,1,1,1,1,1...1,0,0,0)

Write r5,r6

Load grid with r6 data (same as r5 data)

Write r6, r7 (since r6 was previously "half" written with r5 data in the prior cycle and since the r5 data was the same as the r6 data, r6 is written completely on the subsequent cycle.)

Load r7 data

Write r7,r8

Load r8

Write r8,r9

Load r9

Write r9,r10 (r10 is another partial transition line, i.e., it is the transition from the top of the "T" to the stem of the "T". Since the r9 data is written online 10, a portion thereof, i.e., that which should contain non-written pixels - the X's - will be dimly or half written.)

Load r10

Write r10,r11

repeats untilrow 26 where:

Load r26

Write r26,r27 (constitutes another transition line)

Write r27, r28, etc.

Load r27 - The foregoing should illustrate one embodiment of the present inventive method. Further, it can be understood that in lieu of two line set writing, three, four, or more lines can be written simultaneously with corresponding increases in speed and in transition lines which will be of varying intensity depending upon the number of repetitions of writes to those transition lines. For example, in four line set writing, when a transition from blank to written pixels occurs, there are three transition lines, the first being the dimmest and the last, the darkest. The fourth line written will be fully written. Similarly, in a transition from written to non-written pixels, there will be three transition lines, the first being the darkest and the last the dimmest. The fourth line will be non-written. Of course, in four line set writing, the benefit of increasing writing speed over the normal speed would be utilized to produce a fourfold increase in speed.

- FIG. 5 is a generalized flowchart of the steps of the present inventive method for operating an EPID in a multi-line write mode. It would be expected that operator selection of display writing speed would be offered so that the operator can choose the speed and clarity. This sort of selection is presently offered to operators upon printing on dot-matrix printers, i.e. enhanced printing has greater pixel density but takes longer to print. Accordingly, the operator first enters the number of lines to be written in each

write cycle 32. From, this input the write cycle time (writing speed) is adjusted 34. The greater the number of lines simultaneously written in each write cycle, the faster the writing speed. Of course, the operator input could be expressed as a selection of writing speed, wherein the operator would select from a range of speeds corresponding to the number of lines simultaneously written. The flowchart shown in FIG. 5 pertains to the display of a single complete image (frame) on the EPID. This algorithm would be utilized over and over under the control of programming at the next higher level. The operator would not be queried as to the operating speed on each frame displayed. Information of that type would be initially set by query or default then changed by interrupt if desired. Having determined the line set size for writing, the writing is begun at thefirst row 36. (Of course, it would be equally feasible to load rows with data and write columns.) The processor then enters a loop wherein data for the current row is loaded onto the column lines (here grid lines) 38. The data is simultaneously written on the current row and the next x-1 rows by enabling those rows with a logical "1" 40, x being the number of rows in the write set selected. Thus, on the first write cycle in a 4 line set write mode,row 1 and the next (4-1) or 3 rows, i.e., rows 2, 3 and 4 are written. Note that the "1" state may correspond to a variety of voltages depending upon the EPID in question, e.g., whether the EPID is a triode or tetrode. A voltage of 0 volts has been used to enable writing in triodes and, in those instances, represent a logical "1" or enable state. The row set is written for a write cycle time that has been adjusted by the size of the row set (divided by). This is continued until all rows are written 42,44, whereupon control is returned to the next higher level in the program. Of course, other line writing sequences could be employed using a multi-line write strategy, for example, vertical lines can be written from left to right or right to left, horizontal lines could be written from bottom to top or from the middle to the outer periphery, etc.

Claims (7)

- A method for decreasing the time period to write a frame of display data (36,38) composed of a plurality of lines (20) of displayable pixels, on a high line density electrophoretic display (10) requiring a predetermined time period for a line to be fully written, said method comprising the steps of:(a) simultaneously writing (40) a set of at least two adjacent lines (20) with said display data (36,38) in a first time period which is less than said predetermined time period for a line to be fully written;(b) shifting the elements (44) of said line set such that said set includes at least one new line and at least one original line;(c) writing said shifted line set (40) in a second time period which is less than said predetermined time period, following said step of shifting (44); and(d) repeating steps (b) and (c) until said frame is completely written.

- The method of Claim 1, wherein each of said first and second time periods decreases in duration with increasing numbers of said elements in said line set.

- The method of Claim 2, wherein each of said first and second time periods approximates said predetermined time period divided by the number of elements in said line set.

- The method of Claim 1, wherein said pixels of said original line are written at a pixel intensity, which approximates to a predetermined pixel intensity for a pixel written for said predetermined time period for a line to be fully written, when said new line contains pixels of a predetermined displacement.

- The method of Claim 4, wherein the method further includes the step of selecting the number of lines in said set (32).

- The method of Claim 5, wherein the method further includes the step of adjusting the duration of said time period (34), which is less than said predetermined time period for a line to be fully written, when a change in the number of lines in said set occurs.

- The method of Claim 6, wherein said predetermined displacement is equal to the displacement of a reference line that is located on an edge of said display (10).

Applications Claiming Priority (1)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| PCT/US1991/006601 WO1993006585A1 (en) | 1991-09-17 | 1991-09-17 | Method for writing data to an electrophoretic display panel |

Publications (3)

| Publication Number | Publication Date |

|---|---|

| EP0604423A1 EP0604423A1 (en) | 1994-07-06 |

| EP0604423A4 EP0604423A4 (en) | 1995-03-01 |

| EP0604423B1 true EP0604423B1 (en) | 1996-12-11 |

Family

ID=1239540

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| EP92904723A Expired - Lifetime EP0604423B1 (en) | 1991-09-17 | 1991-09-17 | Method for writing data to an electrophoretic display panel |

Country Status (4)

| Country | Link |

|---|---|

| EP (1) | EP0604423B1 (en) |

| CA (1) | CA2119247C (en) |

| DE (1) | DE69123605T2 (en) |

| WO (1) | WO1993006585A1 (en) |

Cited By (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6124851A (en) | 1995-07-20 | 2000-09-26 | E Ink Corporation | Electronic book with multiple page displays |

| US6473072B1 (en) | 1998-05-12 | 2002-10-29 | E Ink Corporation | Microencapsulated electrophoretic electrostatically-addressed media for drawing device applications |

| US6504524B1 (en) | 2000-03-08 | 2003-01-07 | E Ink Corporation | Addressing methods for displays having zero time-average field |

| US6531997B1 (en) | 1999-04-30 | 2003-03-11 | E Ink Corporation | Methods for addressing electrophoretic displays |

| US6683333B2 (en) | 2000-07-14 | 2004-01-27 | E Ink Corporation | Fabrication of electronic circuit elements using unpatterned semiconductor layers |

| US6704133B2 (en) | 1998-03-18 | 2004-03-09 | E-Ink Corporation | Electro-optic display overlays and systems for addressing such displays |

| US8466852B2 (en) | 1998-04-10 | 2013-06-18 | E Ink Corporation | Full color reflective display with multichromatic sub-pixels |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6291925B1 (en) | 1998-01-12 | 2001-09-18 | Massachusetts Institute Of Technology | Apparatus and methods for reversible imaging of nonemissive display systems |

| AU3190499A (en) * | 1998-03-18 | 1999-10-11 | E-Ink Corporation | Electrophoretic displays and systems for addressing such displays |

| EP0971336A3 (en) * | 1998-07-10 | 2000-04-05 | Massachusetts Institute Of Technology | Apparatus and methods for selective imaging in nonemissive display systems |

| US6762744B2 (en) | 2000-06-22 | 2004-07-13 | Seiko Epson Corporation | Method and circuit for driving electrophoretic display, electrophoretic display and electronic device using same |

| JP2005531801A (en) * | 2002-07-01 | 2005-10-20 | コーニンクレッカ フィリップス エレクトロニクス エヌ ヴィ | Electrophoretic display panel |

| JP2005266178A (en) | 2004-03-17 | 2005-09-29 | Sharp Corp | Driver for display device, the display device and method for driving the display device |

| EP1739650A1 (en) * | 2005-06-30 | 2007-01-03 | Thomson Licensing | Driving method of a passive matrix display device with multi-line selection |

Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4742345A (en) * | 1985-11-19 | 1988-05-03 | Copytele, Inc. | Electrophoretic display panel apparatus and methods therefor |

Family Cites Families (4)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| JPH07113819B2 (en) * | 1984-11-06 | 1995-12-06 | キヤノン株式会社 | Display device and driving method thereof |

| US5049865A (en) * | 1987-10-29 | 1991-09-17 | Nec Corporation | Display apparatus |

| US4982183A (en) * | 1988-03-10 | 1991-01-01 | Planar Systems, Inc. | Alternate polarity symmetric drive for scanning electrodes in a split-screen AC TFEL display device |

| US5066946A (en) * | 1989-07-03 | 1991-11-19 | Copytele, Inc. | Electrophoretic display panel with selective line erasure |

-

1991

- 1991-09-17 DE DE69123605T patent/DE69123605T2/en not_active Expired - Fee Related

- 1991-09-17 CA CA 2119247 patent/CA2119247C/en not_active Expired - Fee Related

- 1991-09-17 EP EP92904723A patent/EP0604423B1/en not_active Expired - Lifetime

- 1991-09-17 WO PCT/US1991/006601 patent/WO1993006585A1/en active IP Right Grant

Patent Citations (1)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US4742345A (en) * | 1985-11-19 | 1988-05-03 | Copytele, Inc. | Electrophoretic display panel apparatus and methods therefor |

Cited By (9)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US6124851A (en) | 1995-07-20 | 2000-09-26 | E Ink Corporation | Electronic book with multiple page displays |

| US6680725B1 (en) | 1995-07-20 | 2004-01-20 | E Ink Corporation | Methods of manufacturing electronically addressable displays |

| US6704133B2 (en) | 1998-03-18 | 2004-03-09 | E-Ink Corporation | Electro-optic display overlays and systems for addressing such displays |

| US8466852B2 (en) | 1998-04-10 | 2013-06-18 | E Ink Corporation | Full color reflective display with multichromatic sub-pixels |

| US6473072B1 (en) | 1998-05-12 | 2002-10-29 | E Ink Corporation | Microencapsulated electrophoretic electrostatically-addressed media for drawing device applications |

| US6738050B2 (en) | 1998-05-12 | 2004-05-18 | E Ink Corporation | Microencapsulated electrophoretic electrostatically addressed media for drawing device applications |

| US6531997B1 (en) | 1999-04-30 | 2003-03-11 | E Ink Corporation | Methods for addressing electrophoretic displays |

| US6504524B1 (en) | 2000-03-08 | 2003-01-07 | E Ink Corporation | Addressing methods for displays having zero time-average field |

| US6683333B2 (en) | 2000-07-14 | 2004-01-27 | E Ink Corporation | Fabrication of electronic circuit elements using unpatterned semiconductor layers |

Also Published As

| Publication number | Publication date |

|---|---|

| EP0604423A4 (en) | 1995-03-01 |

| CA2119247A1 (en) | 1993-04-01 |

| DE69123605D1 (en) | 1997-01-23 |

| JPH06510370A (en) | 1994-11-17 |

| DE69123605T2 (en) | 1997-04-03 |

| CA2119247C (en) | 1999-07-06 |

| WO1993006585A1 (en) | 1993-04-01 |

| EP0604423A1 (en) | 1994-07-06 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5266937A (en) | Method for writing data to an electrophoretic display panel | |

| US5467107A (en) | Electrophoretic display panel with selective character addressability | |

| EP0601075B1 (en) | Electrophoretic display with single character erasure | |

| US5412398A (en) | Electrophoretic display panel and associated methods for blinking displayed characters | |

| EP0632919B1 (en) | Electrophoretic display panel for blinking displayed characters | |

| US5066946A (en) | Electrophoretic display panel with selective line erasure | |

| KR101214877B1 (en) | Methods for driving electro-optic displays | |

| US5627561A (en) | Electrophoretic display panel with selective character addressability | |

| EP0604423B1 (en) | Method for writing data to an electrophoretic display panel | |

| EP0628194A1 (en) | Electrophoretic display panel and associated methods providing single pixel erase capability | |

| WO1995006307A1 (en) | Electrophoretic display having reduced writing time | |

| US8350802B2 (en) | Electrophoretic device with capacitive storage and applied fluctuating signal, method of driving the same, and electronic apparatus | |

| JP5406526B2 (en) | In-plane switching display | |

| WO1995006307B1 (en) | Electrophoretic display having reduced writing time | |

| JP3002537B2 (en) | Method for writing data to electrophoretic display panel | |

| GB2175726A (en) | Display devices | |

| KR100565196B1 (en) | Apparatus and method for driving electronic ink display panel | |

| KR100575641B1 (en) | Method for driving electronic ink display panel | |

| JPS6193432A (en) | Liquid crystal display device | |

| JPS63132223A (en) | Method for driving optical modulating element |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| PUAI | Public reference made under article 153(3) epc to a published international application that has entered the european phase |

Free format text: ORIGINAL CODE: 0009012 |

|

| 17P | Request for examination filed |

Effective date: 19940303 |

|

| AK | Designated contracting states |

Kind code of ref document: A1 Designated state(s): BE DE FR GB NL |

|

| A4 | Supplementary search report drawn up and despatched | ||

| AK | Designated contracting states |

Kind code of ref document: A4 Designated state(s): BE DE FR GB NL |

|

| 17Q | First examination report despatched |

Effective date: 19950627 |

|

| GRAH | Despatch of communication of intention to grant a patent |

Free format text: ORIGINAL CODE: EPIDOS IGRA |

|

| GRAH | Despatch of communication of intention to grant a patent |

Free format text: ORIGINAL CODE: EPIDOS IGRA |

|

| GRAA | (expected) grant |

Free format text: ORIGINAL CODE: 0009210 |

|

| AK | Designated contracting states |

Kind code of ref document: B1 Designated state(s): BE DE FR GB NL |

|

| REF | Corresponds to: |

Ref document number: 69123605 Country of ref document: DE Date of ref document: 19970123 |

|

| ET | Fr: translation filed | ||

| PLBE | No opposition filed within time limit |

Free format text: ORIGINAL CODE: 0009261 |

|

| STAA | Information on the status of an ep patent application or granted ep patent |

Free format text: STATUS: NO OPPOSITION FILED WITHIN TIME LIMIT |

|

| 26N | No opposition filed | ||

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: DE Payment date: 20000911 Year of fee payment: 10 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: FR Payment date: 20000912 Year of fee payment: 10 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: GB Payment date: 20000913 Year of fee payment: 10 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: NL Payment date: 20000928 Year of fee payment: 10 |

|

| PGFP | Annual fee paid to national office [announced via postgrant information from national office to epo] |

Ref country code: BE Payment date: 20001117 Year of fee payment: 10 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: GB Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20010917 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: BE Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20010930 |

|

| REG | Reference to a national code |

Ref country code: GB Ref legal event code: IF02 |

|

| BERE | Be: lapsed |

Owner name: COPYTELE INC. Effective date: 20010930 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: NL Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20020401 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: DE Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20020501 |

|

| GBPC | Gb: european patent ceased through non-payment of renewal fee |

Effective date: 20010917 |

|

| PG25 | Lapsed in a contracting state [announced via postgrant information from national office to epo] |

Ref country code: FR Free format text: LAPSE BECAUSE OF NON-PAYMENT OF DUE FEES Effective date: 20020531 |

|

| NLV4 | Nl: lapsed or anulled due to non-payment of the annual fee |

Effective date: 20020401 |

|

| REG | Reference to a national code |

Ref country code: FR Ref legal event code: ST |

|

| NLV4 | Nl: lapsed or anulled due to non-payment of the annual fee |

Effective date: 20020401 |