US7797700B2 - Method of executing concurrent tasks by a subsystem managed by a central processor - Google Patents

Method of executing concurrent tasks by a subsystem managed by a central processor Download PDFInfo

- Publication number

- US7797700B2 US7797700B2 US10/831,539 US83153904A US7797700B2 US 7797700 B2 US7797700 B2 US 7797700B2 US 83153904 A US83153904 A US 83153904A US 7797700 B2 US7797700 B2 US 7797700B2

- Authority

- US

- United States

- Prior art keywords

- task

- message

- subsystem

- counter

- processing

- Prior art date

- Legal status (The legal status is an assumption and is not a legal conclusion. Google has not performed a legal analysis and makes no representation as to the accuracy of the status listed.)

- Active, expires

Links

- 238000000034 method Methods 0.000 title claims abstract description 37

- 238000012545 processing Methods 0.000 claims abstract description 81

- 238000003860 storage Methods 0.000 claims abstract description 21

- 230000004044 response Effects 0.000 claims description 7

- 230000006870 function Effects 0.000 claims description 6

- 230000001143 conditioned effect Effects 0.000 claims description 2

- 230000008569 process Effects 0.000 description 6

- 238000004590 computer program Methods 0.000 description 4

- 238000012986 modification Methods 0.000 description 3

- 230000004048 modification Effects 0.000 description 3

- 238000012360 testing method Methods 0.000 description 3

- 230000010365 information processing Effects 0.000 description 2

- 230000010354 integration Effects 0.000 description 2

- 238000013475 authorization Methods 0.000 description 1

- 239000000872 buffer Substances 0.000 description 1

- 238000006243 chemical reaction Methods 0.000 description 1

- 230000006837 decompression Effects 0.000 description 1

- 230000003247 decreasing effect Effects 0.000 description 1

- 238000011161 development Methods 0.000 description 1

- 238000010586 diagram Methods 0.000 description 1

- 238000012432 intermediate storage Methods 0.000 description 1

- 238000012544 monitoring process Methods 0.000 description 1

- 238000012797 qualification Methods 0.000 description 1

- 230000009467 reduction Effects 0.000 description 1

- 230000011664 signaling Effects 0.000 description 1

- 238000012546 transfer Methods 0.000 description 1

Images

Classifications

-

- G—PHYSICS

- G06—COMPUTING; CALCULATING OR COUNTING

- G06F—ELECTRIC DIGITAL DATA PROCESSING

- G06F9/00—Arrangements for program control, e.g. control units

- G06F9/06—Arrangements for program control, e.g. control units using stored programs, i.e. using an internal store of processing equipment to receive or retain programs

- G06F9/46—Multiprogramming arrangements

- G06F9/52—Program synchronisation; Mutual exclusion, e.g. by means of semaphores

-

- H—ELECTRICITY

- H04—ELECTRIC COMMUNICATION TECHNIQUE

- H04N—PICTORIAL COMMUNICATION, e.g. TELEVISION

- H04N19/00—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals

- H04N19/42—Methods or arrangements for coding, decoding, compressing or decompressing digital video signals characterised by implementation details or hardware specially adapted for video compression or decompression, e.g. dedicated software implementation

Definitions

- the present invention relates to managing tasks executed by a subsystem, and more particularly to the management by a central processor of a subsystem which processes tasks in real time.

- a system that includes a central processor, possibly operating with a real-time operating system, and a subsystem managed by the processor is typically used in multimedia applications.

- the subsystems are used to execute audio or video decompression tasks on data flows (streams).

- the processor sends a task to be executed by the decoder.

- a flow of elementary subtasks constitutes a task (e.g., for a task of decoding successive images).

- the video decoder comprises a digital signal processor (generally referred to as a “DSP”).

- DSP digital signal processor

- the processor's management of responses from the subsystem slows down the execution of other tasks by the processor.

- the central processor's memory can then be insufficient and cause an erasure of data to be processed.

- the precision in the timing of subtasks by the subsystem is insufficient.

- Multimedia functions such as pause, fast forward, and the like are not easy to manage, and the synchronization of image and sound is also difficult to manage.

- One embodiment of the present invention provides a method of processing concurrent tasks by a subsystem managed by a central processor.

- Each of the tasks is comprised of successive messages including a first message, intermediate messages, and a last message, and each of the intermediate messages comprises at least one subtask parameter and a link to the next message that indicates a time of processing of the next message.

- the method for each task, there is a step of writing by the central processor, and a step of processing by the subsystem.

- the writing step including the sub-step of writing a message in a memory. If a counter is initially free for access, access to the counter is prohibited by the subsystem. And then if the counter has a zero value, a link is written in the subsystem that indicates a time of processing of the first message by the subsystem.

- a link to the next message is written in the subsystem, with the link to the next message being included in the message written in the memory.

- the writing step also includes the sub-steps of incrementing the counter by a number representative of presence of the message of the task in the memory, and ending the prohibition against accessing the counter.

- the processing step includes the sub-steps of if the counter is initially free for access, prohibiting access to the counter by the central processor; if the counter has a non-zero value, reading the link to the next message and decrementing the counter; ending the prohibition against accessing the counter; and processing the subtask parameters of the next message at the time indicated in the link to the next message.

- the system includes a storage memory, a central processor capable of generating and writing messages of the concurrent tasks in the storage memory, a subsystem capable of reading the messages from the storage memory, counters, and semaphores associated with the counters.

- Each of the tasks is comprised of a first message, a plurality of intermediate messages, and a last message, and each intermediate message comprises at least one subtask parameter and a link to the next message.

- the subsystem comprises command means for requesting the processing of one of the messages at the time specified in the link of the preceding message, and processing means for processing the message in response to the request.

- Each of the counters is associated with one of the tasks, is capable of being incremented by the central processor, and is capable of being decremented by the subsystem.

- Each of the semaphores authorizes an access by the central processor to the counter associated with that semaphore only in the absence of an access by the subsystem to that counter, and authorizes an access by the subsystem to the associated counter only in the absence of an access by the central processor to that counter.

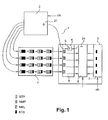

- FIG. 1 shows a block diagram of a system in accordance with one embodiment of the present invention

- FIG. 2 shows the structure of three successive packets belonging to the same task in accordance with one exemplary embodiment of the present invention.

- FIG. 3 shows a representation of a semaphore used in one exemplary embodiment of the present invention.

- Preferred embodiments of the present invention provide a method of processing different concurrent tasks by a subsystem managed by a central processor.

- the tasks are comprised of successive messages that include a first message, intermediate messages, and a last message.

- Each intermediate message comprises at least one subtask parameter and a link to the next message indicating the time of processing the next message.

- the central processor and the subsystem are connected to a plurality of counters associated to respective tasks and to a storage memory.

- the central processor for each task, there is a sub-step of writing by the central processor, and a sub-step of processing by the subsystem.

- a message is written in the memory, and then if the counter is initially free for access, access to the associated counter by the subsystem is prohibited. And then, if the counter has a zero value, the central processor writes in the subsystem a link indicating the time of processing of the first message by the subsystem. Otherwise, the link to the next message is written in the subsystem, with this link being included in the message written in the memory.

- the counter is incremented by the central processor by a number representative of the presence of a message of the task in the memory, and then the prohibition against accessing the counter is ended.

- the subsystem if the counter is initially free for access, access to the associated counter by the central processor is prohibited, and then if the counter has a non-zero value, the subsystem reads the link to the next message previously written and decrements the associated counter. Then, the prohibition against accessing the associated counter is ended, and then the subsystem processes the subtask parameters of the next message at the time indicated in that link.

- the link to the next message also indicates the length of the next message.

- the messages of a task are arranged sequentially in the memory.

- the link to the next message does not comprise the address of the next message in the memory.

- the link to the next message also indicates the address of the next message in the memory.

- the central processor consults the list of available addresses in the memory, determines an address at which to store the message in the memory, and writes the address of the message in the link of the preceding message.

- the link to the next message also indicates the type of the next message.

- at least one link of a message indicates an immediate processing of the next message, and the method further includes immediately processing the next message.

- at least one link to the next message indicates a processing conditioned by an external event, and the method further includes: receiving by the subsystem a signal representative of an external event, and then processing the next message by the subsystem.

- the signal is a video synchronization signal.

- the link to the next message indicates the time of processing the next message by a relative time interval separating the processing of the next message and that of the message comprising the link.

- the first message of a task does not contain subtask parameters

- the last message comprises a link indicating the end of the task.

- the indication of the time of processing the next message in the link of the last message comprises a zero value.

- the subsystem executes video processing tasks comprising the management of image acquisition, the management of image display, and image encoding/decoding; and when several links indicate the same time of execution for several messages, the subsystem gives priority to processing the subtask parameters of an image acquisition management message, then to the subtask parameters of an image display message, and then to the subtask parameters of an image encoding/decoding message.

- the subsystem and the central processor receive as input a common clock signal and determine their respective system times on the basis of that clock signal.

- the processing of parameters of a message is performed when the system time of the subsystem is equal to the time indicated for the processing of the message.

- the present invention also provides electronic systems for executing concurrent tasks.

- One preferred system includes storage memory, a central processor, a subsystem capable of reading the messages written in the storage memory, counters, and semaphores.

- the central processor is capable of generating and writing successive messages constituting a plurality of concurrent tasks in the storage memory, with each task being comprised of a first message, a plurality of intermediate messages, and a last message, and with each written intermediate message comprising at least one subtask parameter and a link to the next message.

- the subsystem comprises command means requesting the processing of a message at the time specified in the link of the preceding message, and processing means for processing the message at that time in response to the request.

- Each counter is associated with one of the tasks, and is capable of being incremented by the central processor and decremented by the subsystem.

- Each semaphore authorizes an access by the central processor to a counter associated to that semaphore only in the absence of an access by the subsystem to the counter, and authorizes an access by the subsystem to the associated counter only in the absence of an access by the central processor to the counter.

- the memory comprises at least a plurality of FIFO-type parallel storage lines, whose input is connected to the central processor and whose output is connected to the subsystem.

- the system has a clock that supplies the same clock signal to the central processor and to the subsystem.

- the central processor and the subsystem each have means for determining a system time as a function of the clock signals.

- the subsystem comprises a time module for comparing the system time and the time of execution of a message, and generating the request upon an equality between the system time and the time of execution.

- the subsystem has an input for receiving external events other than clock signals.

- the subsystem is capable of synchronizing the processing of at least one message with a received external event.

- the counter comprises the number of messages of a task stored in the memory.

- preferred embodiments of the present invention propose processing different concurrent tasks formed by a first message, intermediate messages, and a last message.

- the intermediate messages comprise a subtask parameter and a link to the next message, with this link indicating the time for processing the next message.

- a counter is associated with each task.

- a semaphore is used to avoid conflicts in accessing the counter, from the central processor or the subsystem.

- the counter can also discriminate whether the message is a first message, an intermediate message, or a last message.

- Such a system can notably reduce, or even eliminate, the sending of information from the subsystem to the central processor to manage the execution of tasks.

- This system further enables a reduction in the response time requirements for the central processor.

- This system moreover allows the subtasks of a task to execute at a determined time.

- This system also allows the subsystem and the central processor to access common data without conflict.

- the system allows the load on the central processor's memory to be to relieved.

- FIG. 1 shows an exemplary embodiment of a system for implementing processes of the present invention.

- the system 1 comprises a central processor 2 , a message processing subsystem 3 , and a memory 4 .

- the central processor 2 has write access to the memory 4

- the subsystem 3 has read access to the memory 4 .

- the system 1 further comprises counters 5 that are each associated with a respective task. Each counter 5 is associated with an access management semaphore 6 , which manages read and write access of the central processor 2 or the subsystem 3 .

- a time module 7 commands the execution of subtasks by a processing module 8 of the subsystem 3 at determined times.

- the system 1 of this embodiment also comprises an intermediate storage register 9 , which is connected between the memory 4 and the processing module 8 .

- the subsystem can be implemented by integrating or not integrating the different elements described above. Further, the dimensions of the busses between the different elements of the system 1 are designed so as to ensure sufficient flow rates for the particular application.

- the general operation of the system of FIG. 1 in accordance with an embodiment of the present invention is as follows.

- the central processor 2 generates the messages and determines the times when subtasks are to be executed by the subsystem 3 .

- This management of processing times allows the central processor 2 to easily manage multimedia functions such as fast forward, pause, and the like in audiovisual flows (streams).

- the synchronization of audio and video flows is moreover easier to manage, especially in the case where one system manages audio flows and another system manages video flows. Examples of message structures are described in detail below.

- the central processor 2 For each subtask, the central processor 2 carries out a step of writing a message in the memory 4 . During this writing step, the central processor 2 writes a message in the memory 4 , and a test is made to determine whether the counter 5 is free for access, via the associated semaphore. If the counter is free for access, the central processor 2 prohibits the subsystem 3 from accessing the counter 5 . If the counter is not free for access, the central processor 2 renews the test until the counter 5 is free for access. The central processor 2 then reads the value in the counter 5 . If the counter 5 has a zero value, the processor writes a link indicating the time of processing of the first message in the subsystem 3 , for example in the time module 7 .

- the central processor 2 If the counter 5 has a non-zero value, the central processor 2 writes in the subsystem 3 a link to the next message, initially included in the message written in the memory. The counter is incremented by the central processor 2 by a number representing the presence of a message of the task in the memory 4 . The central processor 2 thus has an incrementation output 21 . The central processor 2 then ends the prohibition against accessing the counter 5 .

- the subsystem 3 processes the parameters of the messages stored in the memory 4 .

- the subsystem 3 tests beforehand whether the counter 5 is free for access. If the counter 5 is free for access, the subsystem 3 prohibits the central processor 2 from accessing the counter 5 . If the counter 5 has a non-zero value, the subsystem 3 reads the link to the message currently being processed, with this link being contained in the previous message. The counter 5 is then decremented and the prohibition against accessing counter 5 is then ended.

- the subsystem 3 has an output 31 for decrementing the counter 5 .

- the subsystem 3 processes the subtask parameters of the current message at the time indicated in the link of the previous message.

- the time when a message is processed is, for example, managed by the time module 7 .

- the time module 7 compares, for example, the time indicated in the link of the previous message with the current time, for example obtained from a system time shared with the subsystem 3 . When the indicated time is equal to the current time, the time module 7 orders the processing of the corresponding message by the subsystem 3 .

- FIG. 3 An exemplary one-bit semaphore is illustrated in FIG. 3 .

- the illustrated semaphore 6 forbids access to an element other than the one being accessed when the bit is equal to 1, and authorizes all access when the bit is equal to 0.

- the semaphore 6 serves to avoid simultaneous access to the counter 5 by the central processor 2 and the subsystem 3 . This prevents erroneous entries in the counter 5 .

- the counter 5 can be made to memorize the number of subtasks or messages that remain to be processed for a task, or, again, the counter 5 can produce just a binary state to indicate whether or not a message from the task is present in the memory 4 . If the counter 5 memorizes the number of messages that remain to be processed, the central processor 2 can consult the counter 5 to determine whether a defined subtask has been executed. In particular, the counter can serve to discriminate whether the message is a first message of a task, an intermediate message, or a last message. The counter also allows the central processor 2 to reset or erase a task; to do this, the central processor 2 needs only to write a zero value in the counter 5 .

- FIG. 2 shows the structure of three successive packets belonging to the same task in accordance with one exemplary embodiment of the present invention in which the system comprises a central processor and a subsystem.

- the message structures of a task T comprise three messages M 0 to M 2 . These messages have been generated successively by the central processor.

- “successively” means that for a given task the messages have been generated in a determined order.

- the processor can generate messages for other tasks, for example in the interval separating the generation of messages M 0 and M 1 .

- Message M 0 is the first message of task T

- message M 1 is an intermediate message

- message M 2 is the last message of that task.

- the message M 0 in this embodiment just comprises a link L 0 to message M 1 .

- This first message M 0 preferably does not comprise subtask parameters, since it has not been preceded by any message of task T. Accordingly, the execution time of possible parameters of M 0 could not have been defined in another message of task T.

- Link L 0 comprises a pointer to the address of M 1 in memory 4 , an indicator of the type of the message M 1 , and an indicator of the execution time of M 1 .

- Link L 0 can also include an indicator of the length of message M 1 , a request for the immediate execution of message M 1 (which implies the immediate processing of M 1 by the subsystem), a request for the conditional execution of message M 1 (e.g., by monitoring external events: a signal representing an external event indicated in the request is received, and then message M 0 is processed; it is also possible to monitor a video synchronization signal).

- the address pointer is fundamental in embodiments in which successive messages of a task are not written one after the other in a FIFO memory.

- the length indicator allows use of subtask parameters of variable length.

- the execution time indicator specifies the execution time of parameters P 1 of M 1 , defined subsequently.

- the indicator of the execution time of the next message can be implemented in several ways. There can be used either an absolute indicator that indicates the absolute time of execution relative to the system time, or a relative indicator that defines the time interval separating a message from the next message.

- the relative indicator makes it easier to modify the execution time of a set of subtasks, since all that is required is to modify one indicator to modify the execution time of the next messages. This type of link is particularly advantageous for managing multimedia functions such as those described above.

- the time can be defined by a numerical value, whose increment is a unit time interval, for example the period of one cycle of the system clock.

- the central processor 2 and the subsystem 3 preferably use the same clock signal.

- each first message and each intermediate message can include the information of L 0 described for M 0 , concerning the next message.

- Message M 1 has a link L 1 to the next message M 2 , with a structure similar to that of link L 0 .

- Message M 1 further comprises a zone P 1 containing parameters corresponding to data of the task to be processed by the subsystem 3 .

- Message M 2 also comprises a link L 2 to a next message, and a zone P 2 comprising subtask parameters.

- Link L 2 and zone P 2 have the same overall structure as L 1 and P 1 respectively.

- Message M 2 preferably comprises a link L 2 indicating that M 2 is the last message of a task. This reduces requirements for other signaling means for the central processor 2 .

- unused zones or indicators of L 2 are utilized to indicate that M 2 is the last message of task T. It is possible to assign a zero value to an indicator of link L 2 to provide that information. Provisions can be made to include a zero value as an indication of the execution time of the next message in L 2 .

- a link to the next message having the following structure: a 28-bit size pointer to the next message, an 8-bit size indicator of the type of the next message, and a 32-bit size indicator of the execution time.

- FIG. 1 With each task processed by the central processor 2 there is associated a line in the FIFO memory. Accordingly, the central processor 2 writes successive messages of a given task at the FIFO memory input. This embodiment enables, if need be, an address pointer not to be written in the link of a message, since successive messages are arranged in the memory one after the other, in the order of processing by the subsystem 3 . With each line of the FIFO memory 4 , there is associated a memory space of a register 9 . Once a message at the FIFO memory output is processed, its link is stored in the subsystem 3 .

- the indicator of the execution time of the next message is stored in the time module, while the next message pointer and the indicator of the length of the next message are stored in register 9 .

- the following labels identify portions of messages: STP corresponds to subtask parameters, NMP corresponds to a next message pointer, NML corresponds to next message length indicator, and ETS corresponds to a next message execution time indicator.

- STP corresponds to subtask parameters

- NMP corresponds to a next message pointer

- NML corresponds to next message length indicator

- ETS corresponds to a next message execution time indicator.

- the next message is then placed at the output of the corresponding line of the FIFO memory 4 . This message can be processed since the subsystem 3 has all the information.

- the use of the address pointers NMP is optional since messages of the same task are placed one after the other in a FIFO line by the central processor 2 .

- register 9 can be considered as forming a whole with the memory 4 .

- the messages or message parameters are stored in an arbitrary memory 4 , which is accessible for writing by the central processor and accessible for reading by the subsystem 3 .

- This memory can be of any type, for example integrated into the subsystem, or split between a memory of the subsystem and an extra external memory.

- a subsystem for managing video can implement the following tasks: video decoding, video display, video acquisition (capture), video encoding, video decoding and display, or video acquisition and encoding.

- An adapted central processor is used to determine the execution times of different messages of a task, and to define the order of execution of messages belonging to different tasks.

- the central processor could generate several messages having a link containing the same execution time indication, or orders of priority could have to be modified due to disruptions on a task.

- the subsystem 3 can carry out several tasks amongst the following: video processing tasks (comprising image acquisition management), image display, and image encoding/decoding management.

- the subsystem then processes, in decreasing order of priority: the subtask parameters of an image acquisition management message, the subtask parameters of an image display message, and then the subtask parameters of an image encoding/decoding message.

- the present invention is not limited to the examples and embodiments described and illustrated above, but is amenable to many variants.

- the system has been presented schematically in independent blocks, it can be envisaged in practice to integrate the central processor, subsystem, and memory, or simply to integrate the subsystem and the memory.

- a common clock signal to determine a system time in the central processor and in the subsystem, there could alternatively be provided an absolute time common to the central processor and to the subsystem.

- Embodiments of the present invention can be embedded in hardware, software, or a combination of hardware and software. Any processor, controller, or other apparatus adapted for carrying out the functionality described herein is suitable.

- the present invention can also be embedded in a computer program product, which comprises all the features enabling the implementation of the methods described herein, and which—when loaded in an information processing system—is able to carry out these methods.

- Computer program means or computer program in the present context mean any expression, in any language, code or notation, of a set of instructions intended to cause a system having an information processing capability to perform a particular function either directly or after conversion to another language.

- Such a computer program can be stored on a computer or machine readable medium allowing data, instructions, messages or message packets, and other machine readable information to be read from the medium.

- the computer or machine readable medium may include non-volatile memory, such as ROM, Flash memory, Disk drive memory, CD-ROM, and other permanent storage. Additionally, a computer or machine readable medium may include, for example, volatile storage such as RAM, buffers, cache memory, and network circuits.

- the computer or machine readable medium may comprise computer or machine readable information in a transitory state medium such as a network link and/or a network interface, including a wired network or a wireless network, that allow a device to read such computer or machine readable information.

Abstract

Description

Claims (29)

Applications Claiming Priority (2)

| Application Number | Priority Date | Filing Date | Title |

|---|---|---|---|

| FR0305064 | 2003-04-24 | ||

| FR0305064A FR2854263A1 (en) | 2003-04-24 | 2003-04-24 | METHOD FOR PERFORMING COMPETITIVE TASKS BY A SUBSYSTEM MANAGED BY A CENTRAL PROCESSOR |

Publications (2)

| Publication Number | Publication Date |

|---|---|

| US20040268355A1 US20040268355A1 (en) | 2004-12-30 |

| US7797700B2 true US7797700B2 (en) | 2010-09-14 |

Family

ID=32947376

Family Applications (1)

| Application Number | Title | Priority Date | Filing Date |

|---|---|---|---|

| US10/831,539 Active 2029-03-14 US7797700B2 (en) | 2003-04-24 | 2004-04-23 | Method of executing concurrent tasks by a subsystem managed by a central processor |

Country Status (4)

| Country | Link |

|---|---|

| US (1) | US7797700B2 (en) |

| EP (1) | EP1471435B1 (en) |

| DE (1) | DE602004014558D1 (en) |

| FR (1) | FR2854263A1 (en) |

Families Citing this family (7)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| GB0909701D0 (en) * | 2009-06-08 | 2009-07-22 | Young Arthur P | Testing completion of concurrent logical operations |

| US9195618B2 (en) | 2009-06-16 | 2015-11-24 | Nvidia Corporation | Method and system for scheduling memory requests |

| US9158610B2 (en) * | 2011-08-04 | 2015-10-13 | Microsoft Technology Licensing, Llc. | Fault tolerance for tasks using stages to manage dependencies |

| US8949853B2 (en) | 2011-08-04 | 2015-02-03 | Microsoft Corporation | Using stages to handle dependencies in parallel tasks |

| AU2012333237B2 (en) * | 2011-11-04 | 2015-12-10 | Apple Inc. | Coordination of self-optimization operations in a self organizing network |

| US9086925B2 (en) * | 2013-01-18 | 2015-07-21 | Nec Laboratories America, Inc. | Methods of processing core selection for applications on manycore processors |

| US9891949B2 (en) * | 2013-03-06 | 2018-02-13 | Nvidia Corporation | System and method for runtime scheduling of GPU tasks |

Citations (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3891974A (en) * | 1973-12-17 | 1975-06-24 | Honeywell Inf Systems | Data processing system having emulation capability for providing wait state simulation function |

| US4318173A (en) * | 1980-02-05 | 1982-03-02 | The Bendix Corporation | Scheduler for a multiple computer system |

| US5005122A (en) * | 1987-09-08 | 1991-04-02 | Digital Equipment Corporation | Arrangement with cooperating management server node and network service node |

| US5563986A (en) * | 1992-04-10 | 1996-10-08 | Fuji Xerox Co., Ltd. | Image processing system |

| US5675796A (en) * | 1994-04-08 | 1997-10-07 | Microsoft Corporation | Concurrency management component for use by a computer program during the transfer of a message |

| US5818967A (en) | 1995-06-12 | 1998-10-06 | S3, Incorporated | Video decoder engine |

| WO1998044745A1 (en) | 1997-03-31 | 1998-10-08 | Sharp Kabushiki Kaisha | Apparatus and method for simultaneous video decompression |

| US5889983A (en) * | 1997-01-21 | 1999-03-30 | Intel Corporation | Compare and exchange operation in a processing system |

| US5902352A (en) * | 1995-03-06 | 1999-05-11 | Intel Corporation | Method and apparatus for task scheduling across multiple execution sessions |

| US6061709A (en) * | 1998-07-31 | 2000-05-09 | Integrated Systems Design Center, Inc. | Integrated hardware and software task control executive |

| US6065089A (en) * | 1998-06-25 | 2000-05-16 | Lsi Logic Corporation | Method and apparatus for coalescing I/O interrupts that efficiently balances performance and latency |

| US6122668A (en) * | 1995-11-02 | 2000-09-19 | Starlight Networks | Synchronization of audio and video signals in a live multicast in a LAN |

| US6260058B1 (en) * | 1994-07-19 | 2001-07-10 | Robert Bosch Gmbh | Process for controlling technological operations or processes |

| US20020124064A1 (en) * | 2001-01-12 | 2002-09-05 | Epstein Mark E. | Method and apparatus for managing a network |

| US6542541B1 (en) | 2000-01-12 | 2003-04-01 | Sony Corporation | Method and apparatus for decoding MPEG video signals using multiple data transfer units |

| US6877157B2 (en) * | 1999-12-30 | 2005-04-05 | Koninklijke Philips Electronics N.V. | Multi-tasking software architecture |

| US6912610B2 (en) * | 2003-03-28 | 2005-06-28 | Emulex Design & Manufacturing Corporation | Hardware assisted firmware task scheduling and management |

| US7150016B2 (en) * | 2000-05-19 | 2006-12-12 | Micro-Epsilon Messtechnik Gmbh & Co. Kg | Systems, methods and computer program products for controlling and visualizing processes |

| US7322033B2 (en) * | 2002-03-29 | 2008-01-22 | Denso Corporation | Distributed control method and apparatus |

-

2003

- 2003-04-24 FR FR0305064A patent/FR2854263A1/en active Pending

-

2004

- 2004-04-16 DE DE602004014558T patent/DE602004014558D1/en not_active Expired - Fee Related

- 2004-04-16 EP EP04291024A patent/EP1471435B1/en not_active Expired - Fee Related

- 2004-04-23 US US10/831,539 patent/US7797700B2/en active Active

Patent Citations (19)

| Publication number | Priority date | Publication date | Assignee | Title |

|---|---|---|---|---|

| US3891974A (en) * | 1973-12-17 | 1975-06-24 | Honeywell Inf Systems | Data processing system having emulation capability for providing wait state simulation function |

| US4318173A (en) * | 1980-02-05 | 1982-03-02 | The Bendix Corporation | Scheduler for a multiple computer system |

| US5005122A (en) * | 1987-09-08 | 1991-04-02 | Digital Equipment Corporation | Arrangement with cooperating management server node and network service node |

| US5563986A (en) * | 1992-04-10 | 1996-10-08 | Fuji Xerox Co., Ltd. | Image processing system |

| US5675796A (en) * | 1994-04-08 | 1997-10-07 | Microsoft Corporation | Concurrency management component for use by a computer program during the transfer of a message |

| US6260058B1 (en) * | 1994-07-19 | 2001-07-10 | Robert Bosch Gmbh | Process for controlling technological operations or processes |

| US5902352A (en) * | 1995-03-06 | 1999-05-11 | Intel Corporation | Method and apparatus for task scheduling across multiple execution sessions |

| US5818967A (en) | 1995-06-12 | 1998-10-06 | S3, Incorporated | Video decoder engine |

| US6122668A (en) * | 1995-11-02 | 2000-09-19 | Starlight Networks | Synchronization of audio and video signals in a live multicast in a LAN |

| US5889983A (en) * | 1997-01-21 | 1999-03-30 | Intel Corporation | Compare and exchange operation in a processing system |

| WO1998044745A1 (en) | 1997-03-31 | 1998-10-08 | Sharp Kabushiki Kaisha | Apparatus and method for simultaneous video decompression |

| US6065089A (en) * | 1998-06-25 | 2000-05-16 | Lsi Logic Corporation | Method and apparatus for coalescing I/O interrupts that efficiently balances performance and latency |

| US6061709A (en) * | 1998-07-31 | 2000-05-09 | Integrated Systems Design Center, Inc. | Integrated hardware and software task control executive |

| US6877157B2 (en) * | 1999-12-30 | 2005-04-05 | Koninklijke Philips Electronics N.V. | Multi-tasking software architecture |

| US6542541B1 (en) | 2000-01-12 | 2003-04-01 | Sony Corporation | Method and apparatus for decoding MPEG video signals using multiple data transfer units |

| US7150016B2 (en) * | 2000-05-19 | 2006-12-12 | Micro-Epsilon Messtechnik Gmbh & Co. Kg | Systems, methods and computer program products for controlling and visualizing processes |

| US20020124064A1 (en) * | 2001-01-12 | 2002-09-05 | Epstein Mark E. | Method and apparatus for managing a network |

| US7322033B2 (en) * | 2002-03-29 | 2008-01-22 | Denso Corporation | Distributed control method and apparatus |

| US6912610B2 (en) * | 2003-03-28 | 2005-06-28 | Emulex Design & Manufacturing Corporation | Hardware assisted firmware task scheduling and management |

Non-Patent Citations (1)

| Title |

|---|

| French Preliminary Search Report dated Feb. 17, 2004 for French Application No. 03-05064. |

Also Published As

| Publication number | Publication date |

|---|---|

| EP1471435B1 (en) | 2008-06-25 |

| US20040268355A1 (en) | 2004-12-30 |

| EP1471435A1 (en) | 2004-10-27 |

| FR2854263A1 (en) | 2004-10-29 |

| DE602004014558D1 (en) | 2008-08-07 |

Similar Documents

| Publication | Publication Date | Title |

|---|---|---|

| US5473754A (en) | Branch decision encoding scheme | |

| US8601192B2 (en) | Arbitration device, arbitration system, arbitration method, semiconductor integrated circuit, and image processing device | |

| WO2009119009A1 (en) | Access controller | |

| JP3312039B2 (en) | Data driven information processor | |

| JP2006259898A (en) | I/o controller, signal processing system and data transferring method | |

| US7797700B2 (en) | Method of executing concurrent tasks by a subsystem managed by a central processor | |

| US6571332B1 (en) | Method and apparatus for combined transaction reordering and buffer management | |

| KR19980032195A (en) | DMA controller with channel tagging | |

| US6742083B1 (en) | Method and apparatus for multi-part processing of program code by a single processor | |

| US8667233B2 (en) | Competition testing device | |

| WO2018042935A1 (en) | Electronic control device and analysis system | |

| JPH11110214A (en) | Command control system and method for the same | |

| US20050262314A1 (en) | System and method for circular buffer | |

| JP2012113502A (en) | Verification device for semiconductor integrated circuit | |

| JP3402581B2 (en) | Data restoration device | |

| JP4335327B2 (en) | Arbitration apparatus and method | |

| JPH0540698A (en) | Main storage page managing system | |

| JP2007241922A (en) | Arbitration method for use of shared resource, and arbitration device therefor | |

| JP2010140440A (en) | Bus arbitration device | |

| JP5171062B2 (en) | Memory access circuit | |

| JPH11119922A (en) | Data storage system and redundant data write control method | |

| CN100412831C (en) | Data processing system and memory device arbitrating method | |

| JP2004220309A (en) | Multiprocessor system | |

| US20030046506A1 (en) | Dynamic access control of a function to a collective resource | |

| JP2007058424A (en) | Memory access controller |

Legal Events

| Date | Code | Title | Description |

|---|---|---|---|

| AS | Assignment |

Owner name: STMICROELECTRONICS SA, FRANCE Free format text: ASSIGNMENT OF ASSIGNORS INTEREST;ASSIGNORS:ROBIN, FREDERIC;ARTIERI, ALAIN;AUDRAIN, STEPHANE;AND OTHERS;REEL/FRAME:015114/0513;SIGNING DATES FROM 20040727 TO 20040825 Owner name: STMICROELECTRONICS SA, FRANCE Free format text: ASSIGNMENT OF ASSIGNORS INTEREST;ASSIGNORS:ROBIN, FREDERIC;ARTIERI, ALAIN;AUDRAIN, STEPHANE;AND OTHERS;SIGNING DATES FROM 20040727 TO 20040825;REEL/FRAME:015114/0513 |

|

| STCF | Information on status: patent grant |

Free format text: PATENTED CASE |

|

| FPAY | Fee payment |

Year of fee payment: 4 |

|

| MAFP | Maintenance fee payment |

Free format text: PAYMENT OF MAINTENANCE FEE, 8TH YEAR, LARGE ENTITY (ORIGINAL EVENT CODE: M1552) Year of fee payment: 8 |

|

| MAFP | Maintenance fee payment |

Free format text: PAYMENT OF MAINTENANCE FEE, 12TH YEAR, LARGE ENTITY (ORIGINAL EVENT CODE: M1553); ENTITY STATUS OF PATENT OWNER: LARGE ENTITY Year of fee payment: 12 |

|

| AS | Assignment |

Owner name: STMICROELECTRONICS FRANCE, FRANCE Free format text: CHANGE OF NAME;ASSIGNOR:STMICROELECTRONICS SA;REEL/FRAME:066357/0182 Effective date: 20230126 |