THIN FILM TRANSISTORS USING THIN FILM SEMICONDUCTOR MATERIALS

BACKGROUND OF THE INVENTION Field of the Invention

[0001] Embodiments of the present invention generally relate to field effect transistors (FETs) and thin film transistors (TFTs) having semiconductor materials comprising oxygen, nitrogen, and one or more elements selected from the group consisting of zinc, gallium, cadmium, indium, and tin.

Description of the Related Art

[0002] Current interest in TFT arrays is particularly high because these devices may be used in liquid crystal active matrix displays (LCDs) of the kind often employed for computer and television flat panels. The LCDs may also contain light emitting diodes (LEDs) for back lighting. Further, organic light emitting diodes (OLEDs) have been used for active matrix displays, and these OLEDs require TFTs for addressing the activity of the displays.

[0003] TFTs made with amorphous silicon have become the key components of the flat panel display industry. Unfortunately amorphous silicon does have its limitations such as low mobility. The mobility required for OLEDs is at least 10 times higher than that achievable with amorphous silicon. The deposition temperature for amorphous silicon may be high, which can cause a Vth shift. A high current may be necessary for amorphous silicon, which can lead to stability issues in OLEDs. Polysilicon, on the other hand, has a higher mobility than amorphous silicon. Polysilicon is crystalline, which leads to non-uniform deposition. Due to the limitations of amorphous silicon, OLED advancement has been difficult.

[0004] In recent years, transparent TFTs have been created in which zinc oxide has been used as the active channel layer. Zinc oxide is a compound semiconductor that can be grown as a crystalline material at relatively low deposition temperatures on various substrates such as glass and plastic. Zinc oxide based TFTs may not degrade upon exposure to visible light. Therefore, a shield layer, as

is necessary for silicon based TFTs, is not present. Without the shield layer, the TFT remains transparent. Zinc oxide, while having a mobility greater than amorphous silicon, still has a low mobility.

[0005] Therefore, there is a need in the art for TFTs having transparent active channels with high mobility.

SUMMARY OF THE INVENTION

[0006] The present invention generally comprises TFTs having semiconductor material comprising oxygen, nitrogen, and one or more element selected from the group consisting of zinc, tin, gallium, cadmium, and indium as the active channel. The semiconductor material may be used in bottom gate TFTs, top gate TFTs, and other types of TFTs. The TFTs may be patterned by etching to create both the channel and the metal electrodes. Then, the source-drain electrodes may be defined by dry etching using the semiconductor material as an etch stop layer. The active layer carrier concentration, mobility, and interface with other layers of the TFT can be tuned to predetermined values. The tuning may be accomplished by changing the nitrogen containing gas to oxygen containing gas flow ratio, annealing and/or plasma treating the deposited semiconductor film, or changing the concentration of aluminum doping.

[0007] In one embodiment, a TFT is disclosed. The transistor comprises a semiconductor layer comprising oxygen, nitrogen and one or more elements selected from the group consisting of zinc, indium, tin, cadmium, gallium, and combinations thereof. In another embodiment, a TFT fabrication method is disclosed. The method comprises depositing a semiconductor layer over a substrate, the semiconductor layer comprising oxygen, nitrogen and one or more elements selected from the group consisting of zinc, indium, tin, cadmium, gallium, and combinations thereof.

[0008] In another embodiment, a TFT fabrication method is disclosed. The method comprises depositing a semiconductor layer over a substrate, the

semiconductor layer comprising oxygen, nitrogen and one or more elements selected from the group consisting of an element having filled s and d orbitals, an element having a filled f orbital, and combinations thereof. The method also includes depositing a source-drain electrode layer over the active channel layer, first etching the source-drain electrode layer and the active channel layer to create an active channel, and second etching the source-drain electrode layer to define source-drain electrodes.

BRIEF DESCRIPTION OF THE DRAWINGS

[0009] So that the manner in which the above recited features of the present invention can be understood in detail, a more particular description of the invention, briefly summarized above, may be had by reference to embodiments, some of which are illustrated in the appended drawings. It is to be noted, however, that the appended drawings illustrate only typical embodiments of this invention and are therefore not to be considered limiting of its scope, for the invention may admit to other equally effective embodiments.

[0010] Figure 1 is a schematic cross sectional view of a PVD chamber according to one embodiment of the invention.

[0011] Figures 2A-2E are XRD graphs for films showing the formation of zinc and zinc oxide peaks as a function of oxygen gas flow.

[0012] Figures 3A-3F are XRD graphs for showing the formation of a semiconductor film according at various nitrogen gas flow rates according to one embodiment of the invention.

[0013] Figures 4A-4G show a process sequence for forming a bottom gate TFT according to one embodiment of the invention.

[0014] Figure 5 is a schematic cross sectional view of an etch stop TFT according to one embodiment of the invention.

[0015] Figure 6 is a schematic cross sectional view of a top gate TFT according to one embodiment of the invention.

[0016] Figure 7 is a schematic view of an active-matrix LCD according to one embodiment of the invention.

[0017] Figure 8 is a schematic view of an active-matrix OLED according to one embodiment of the invention.

[0018] Figures 9A-9C show the Vth for various active channel lengths and widths.

[0019] Figures 10A-10C show a comparision of the Vth for active channels having a common length and width.

[0020] To facilitate understanding, identical reference numerals have been used, where possible, to designate identical elements that are common to the figures. It is contemplated that elements disclosed in one embodiment may be beneficially utilized on other embodiments without specific recitation.

DETAILED DESCRIPTION

[0021] The present invention generally comprises TFTs having semiconductor material comprising oxygen, nitrogen, and one or more element selected from the group consisting of zinc, tin, gallium, cadmium, and indium as the active channel. The semiconductor material may be used in bottom gate TFTs, top gate TFTs, and other types of TFTs. The TFTs may be patterned by etching to create both the channel and the metal electrodes. Then, the source-drain electrodes may be defined by dry etching using the semiconductor material as an etch stop layer. The active layer carrier concentration, mobility, and interface with other layers of the TFT can be tuned to predetermined values. The tuning may be accomplished by changing the nitrogen containing gas to oxygen containing gas flow ratio, annealing and/or plasma treating the deposited semiconductor film, or changing the concentration of aluminum doping.

[0022] The semiconductor film comprising nitrogen, oxygen, and one or more elements selected from zinc, indium, gallium, cadmium, and tin may be deposited by reactive sputtering. The reactive sputtering method is illustratively described and may be practiced in a PVD chamber for processing large area substrates, such as a 4300 PVD chamber, available from AKT America, Inc., a subsidiary of Applied Materials, Inc., Santa Clara, California. However, because the semiconductor film produced according to the method may be determined by the film structure and composition, it should be understood that the reactive sputtering method may have utility in other system configurations, including those systems configured to process large area round substrates and those systems produced by other manufacturers, including roll-to-roll process platforms. It is to be understood that while the invention is illustratively described below as deposited by PVD, other methods including chemical vapor deposition (CVD), atomic layer deposition (ALD), or spin-on processes may be utilized to deposit the inventive films.

[0023] Figure 1 is a cross-sectional schematic view of a PVD chamber 100 according to one embodiment of the invention. The chamber 100 may be evacuated by a vacuum pump 114. Within the chamber 100, a substrate 102 may be disposed opposite a target 104. The substrate may be disposed on a susceptor 106 within the chamber 100. The susceptor 106 may be elevated and lowered as shown by arrows "A" by an actuator 112. The susceptor 106 may be elevated to raise the substrate 102 to a processing position and lowered so that the substrate 102 may be removed from the chamber 100. Lift pins 108 elevate the substrate 102 above the susceptor 106 when the susceptor 106 is in the lowered position. Grounding straps 110 may ground the susceptor 106 during processing. The susceptor 106 may be raised during processing to aid in uniform deposition.

[0024] The target 104 may comprise one or more targets 104. In one embodiment, the target 104 may comprise a large area sputtering target 104. In another embodiment, the target 104 may comprise a plurality of tiles. In yet another embodiment, the target 104 may comprise a plurality of target strips. In still another embodiment, the target 104 may comprise one or more cylindrical, rotary targets.

The target 104 may be bonded to a backing plate 116 by a bonding layer (not shown). One or more magnetrons 118 may be disposed behind the backing plate 116. The magnetrons 118 may scan across the backing plate 116 in a linear movement or in a two dimensional path. The walls of the chamber may be shielded from deposition by a dark space shield 120 and a chamber shield 122.

[0025] To help provide uniform sputtering deposition across a substrate 102, an anode 124 may be placed between the target 104 and the substrate 102. In one embodiment, the anode 124 may be bead blasted stainless steel coated with arc sprayed aluminum. In one embodiment, one end of the anode 124 may be mounted to the chamber wall by a bracket 130. The anode 124 provides a charge in opposition to the target 104 so that charged ions will be attracted thereto rather than to the chamber walls which are typically at ground potential. By providing the anode 124 between the target 104 and the substrate 102, the plasma may be more uniform, which may aid in the deposition. To reduce flaking, a cooling fluid may be provided through the one or more anodes 124. By reducing the amount of expansion and contraction of the anodes 124, flaking of material from the anodes 124 may be reduced. For smaller substrates and hence, smaller processing chambers, the anodes 124 spanning the processing space may not be necessary as the chamber walls may be sufficient to provide a path to ground and a uniform plasma distribution.

[0026] For reactive sputtering, it may be beneficial to provide a reactive gas into the chamber 100. One or more gas introduction tubes 126 may also span the distance across the chamber 100 between the target 104 and the substrate 102. For smaller substrates and hence, smaller chambers, the gas introduction tubes 126 spanning the processing space may not be necessary as an even gas distribution may be possible through conventional gas introduction means. The gas introduction tubes 126 may introduce sputtering gases from a gas panel 132. The gas introduction tubes 126 may be coupled with the anodes 124 by one or more couplings 128. The coupling 128 may be made of thermally conductive material to permit the gas introduction tubes 126 to be conductively cooled. Additionally, the

coupling 128 may be electrically conductive as well so that the gas introduction tubes 126 are grounded and function as anodes.

[0027] The reactive sputtering process may comprise disposing a metallic sputtering target opposite a substrate in a sputtering chamber. The metallic sputtering target may substantially comprise one or more elements selected from the group consisting of zinc, gallium, indium, tin, and cadmium. In one embodiment, the sputtering target may comprise one or more elements having a filled s orbital and a filled d orbital. In another embodiment, the sputtering target may comprise one or more elements having a filled f orbital. In another embodiment, the sputtering target may comprise one or more divalent elements. In another embodiment, the sputtering target may comprise one or more trivalent elements. In still another embodiment, the sputtering target may comprise one or more tetravalent elements.

[0028] The sputtering target may also comprise a dopant. Suitable dopants that may be used include Al, Sn, Ga, Ca, Si, Ti, Cu, Ge, In, Ni, Mn, Cr, V, Mg, SixNy, AIxOy, and SiC. In one embodiment, the dopant comprises aluminum. In another embodiment, the dopant comprises tin. The substrate, on the other hand, may comprise plastic, paper, polymer, glass, stainless steel, and combinations thereof. When the substrate is plastic, the reactive sputtering may occur at temperatures below about 180 degrees Celsius. Examples of semiconductor films that may be deposited include ZnOxNy:AI, ZnOxNy:Sn, SnOxNy:AI, lnOxNy:AI, lnOxNy:Sn, CdOxNy:AI, CdOxNy:Sn, GaOxNy:AI, GaOxNy:Sn, ZnSnOxNy:AI ZnlnOxNy:AI, ZnlnOxNy:Sn, ZnCdOxNy:AI, ZnCdOxNy:Sn, ZnGaOxNy:AI, ZnGaOxNy:Sn, SnlnOxNy:AI, SnCdOxNy:AI, SnGaOxNy:AI, lnCdOxNy:AI, lnCdOxNy:Sn, lnGaOxNy:AI, lnGaOxNy:Sn, CdGaOxNy:AI, CdGaOxNy:Sn, ZnSnlnOxNy:AI, ZnSnCdOxNy:AI, ZnSnGaOxNy:AI, ZnlnCdOxNy:AI, ZnlnCdOxNy:Sn, ZnlnGaOxNy:AI, ZnlnGaOxNy:Sn, ZnCdGaOxNy:AI, ZnCdGaOxNy:Sn, SnlnCdOxNy:AI, SnlnGaOxNy:AI,

SnCdGaOxNy:AI, lnCdGaOxNy:AI, lnCdGaOxNy:Sn, ZnSnlnCdOxNy:AI, ZnSnlnGaOxNy:AI, ZnlnCdGaOxNy:AI, ZnlnCdGaOxNy:Sn, and SnlnCdGaOxNy:AI.

[0029] During the sputtering process, argon, a nitrogen containing gas, and an oxygen containing gas may be provided to the chamber for reactive sputtering the

metallic target. Additional additives such as B2H6, CO2, CO, CH4, and combinations thereof may also be provided to the chamber during the sputtering. In one embodiment, the nitrogen containing gas comprises N2. In another embodiment, the nitrogen containing gas comprises N2O, NH3, or combinations thereof. In one embodiment, the oxygen containing gas comprises O2. In another embodiment, the oxygen containing gas comprises N2O. The nitrogen of the nitrogen containing gas and the oxygen of the oxygen containing gas react with the metal from the sputtering target to form a semiconductor material comprising metal, oxygen, nitrogen, and optionally a dopant on the substrate. In one embodiment, the nitrogen containing gas and the oxygen containing gas are separate gases. In another embodiment, the nitrogen containing gas and the oxygen containing gas comprise the same gas.

[0030] The film deposited is a semiconductor film. Examples of semiconductor films that may be deposited include ZnOxNy, SnOxNy, InOxNy, CdOxNy, GaOxNy, ZnSnOxNy, ZnInOxNy, ZnCdOxNy, ZnGaOxNy, SnInOxNy, SnCdOxNy, SnGaOxNy, InCdOxNy, InGaOxNy, CdGaOxNy, ZnSnInOxNy, ZnSnCdOxNy, ZnSnGaOxNy, ZnInCdOxNy, ZnInGaOxNy, ZnCdGaOxNy, SnInCdOxNy, SnInGaOxNy, SnCdGaOxNx, InCdGaOxNy, ZnSnInCdOxNy, ZnSnInGaOxNy, ZnInCdGaOxNy, and SnInCdGaOxNy. Each of the aforementioned semiconductor films may be doped by a dopant.

[0031] The semiconductor film may comprise an oxynitride compound. In one embodiment, the semiconductor film comprises both a metal oxynitride compound as well as a metal nitride compound. In another embodiment, the semiconductor film may comprise a metal oxynitride compound, a metal nitride compound, and a metal oxide compound. In still another embodiment, the semiconductor film may comprise a metal oxynitride compound and a metal oxide compound. In another embodiment, the semiconductor film may comprise a metal nitride compound and a metal oxide compound.

[0032] The ratio of the nitrogen containing gas to the oxygen containing gas may affect the mobility, carrier concentration, and resistivity of the semiconductor film. Table I shows the effect of the nitrogen flow rate on the mobility, resistivity, and carrier concentration for a tin target sputtered in an atmosphere of argon and

nitrogen gas. Generally, Table I shows that when the nitrogen flow rate increases, the mobility also increases. The argon and oxygen flow rates may remain the same. In Table I, the argon flow rate is 60 seem and the oxygen flow rate is 5 seem. The higher substrate temperature also provides an increase in mobility. The carrier concentration is weakly correlated with the mobility. The deposited film is an n-type semiconductor material which may function as an electron carrier and hence, the carrier concentration is shown as a negative number.

Table I

[0033] The oxygen containing gas also affects the mobility, carrier concentration, and resistivity of the semiconductor film. Table Il shows the effect of the oxygen flow rate on the mobility, resistivity, and carrier concentration for a tin target sputtered in an atmosphere of argon, nitrogen gas, and oxygen gas. The argon flow rate may remain the same. In Table II, the argon flow rate is 60 seem. Generally, Table Il shows that for high nitrogen gas to oxygen gas ratios, the mobility may be higher than the mobility for amorphous silicon. Additionally, the higher the ratio of nitrogen to oxygen, the lower the carrier concentration. At a 200 seem nitrogen flow rate, the mobility increases as the oxygen flow rate increase, but then decreases at

higher oxygen flow rates. In one embodiment, the mobility may be between about 4 cm2/V-s and about 10 cm2/V-s at a temperature of 150 degrees Celsius. The increase in mobility is not correlated to the carrier concentration. Thus, the mobility improvement may be a result of less scattering of the carrier. The mobility may be very low if no nitrogen additives are used. In such a scenario, the carrier concentration drops significantly as the oxygen gas flow increases. The higher the substrate temperature for a tin target, the better the mobility. In one embodiment, the pressure may be between about 5 mTorr to about 20 mTorr.

Table Il

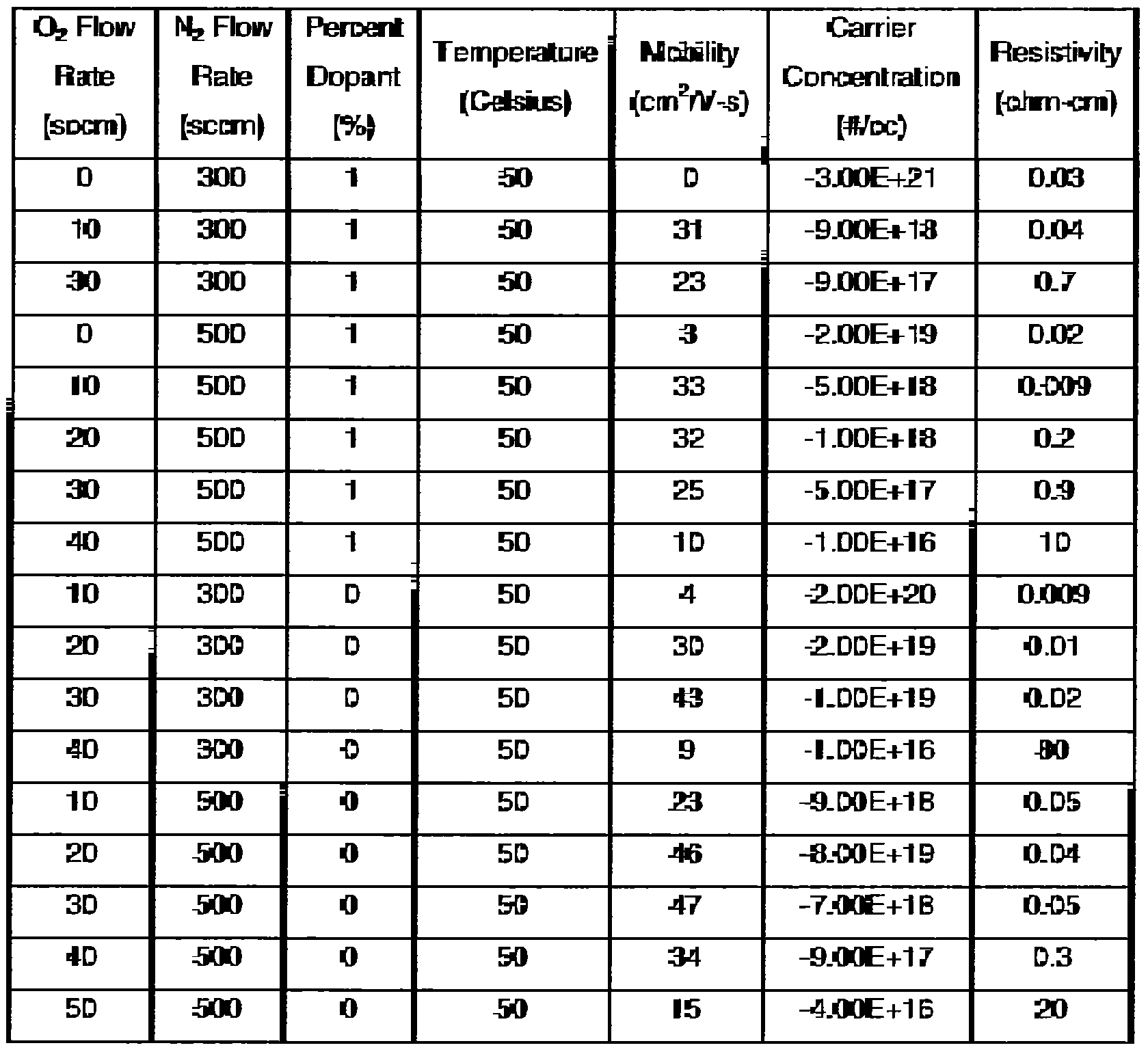

[0034] The amount of dopant may also affect the mobility of the deposited film. However, the mobility will still generally increase with an increase of nitrogen gas flow whether the target is doped or not. Table III shows the effect of dopant upon the mobility, carrier concentration, and resistivity. The dopant is shown in weight percentage. The argon flow rate may be the same for each deposited film. In Table III, the argon flow rate is 120 seem. The carrier concentration when utilizing a dopant may be lower than in the scenario where no dopant is used. Thus, the dopant may be used to tune the carrier concentration.

Table

[0035] Table IV discloses the effect of oxygen gas flow on the mobility, carrier concentration, and resistivity of the semiconductor film. Generally, under a fixed nitrogen gas flow, the mobility of the film will increase as the oxygen flow increases, but drop with a further increase in oxygen flow rate. The argon flow rate may be the same for each deposited film. In Table IV, the argon flow rate is 120 seem. In one embodiment, the mobility of the film will decrease once the nitrogen containing gas to oxygen containing gas ratio is less than about 10:1. The increase in mobility does not relate to an increase in carrier concentration as the oxygen flow rate increases. When a dopant is used, the mobility and carrier concentration may be lowered. Thus, the carrier concentration and mobility may be tuned with the amount of dopant present.

Table IV

[0036] Table V shows the affect of the power density applied on the mobility, carrier concentration, and resistivity of the semiconductor film. Generally, the power density does not greatly affect the mobility, but the higher the power density, the higher the carrier concentration and resistivity. In one embodiment, the power density applied to the sputtering target may be between about 0.3 W/cm2 and about l .O W/cm2.

Table V

[0037] Table Vl shows the effects of utilizing N2O as the oxygen containing gas in depositing the semiconductor film. The N2O gas is effective as an oxygen containing gas in raising the mobility of the semiconductor film and producing a reasonably low carrier concentration.

Table Vl

[0038] Table VII shows the chemical analysis for a semiconductor film that comprises tin, oxygen, and nitrogen and shows the effect of oxygen containing gas upon the film using X-ray photoelectron spectroscopy (XPS). Film 1 was deposited by sputtering a tin target for 360 seconds while a DC bias of 400 W was applied to the sputtering target. Argon was introduced to the processing chamber at a flow rate of 60 seem, nitrogen was introduced at a flow rate of 200 seem, and oxygen was introduced at a flow rate of 5 seem. The deposition occurred at a temperature of 250 degrees Celsius. Film 1 had a carbon content of Film 1 was 22.5 atomic percent, a nitrogen content of 19.4 atomic percent, an oxygen content of 29.4 atomic percent, a fluorine content of 0.7 atomic percent, and a tin content of 28.1 atomic percent. Most, if not all, of the carbon could arise from adventitious carbon (i.e., carbon compounds adsorbed onto the surface of any sample exposed to the atmosphere). Film 2 was deposited by sputtering a tin target for 360 seconds while

a DC bias of 400 W was applied to the sputtering target. Argon was introduced to the processing chamber at a flow rate of 60 seem, nitrogen was introduced at a flow rate of 200 seem, and oxygen was introduced at a flow rate of 20 seem. The deposition occurred at a temperature of 250 degrees Celsius. Film 2 had a carbon content of 17.3 atomic percent, a nitrogen content of 4.5 atomic percent, an oxygen content of 49.9 atomic percent, a fluorine content of 0.6 percent, and a tin content of 27.7 atomic percent. Most, if not all, of the carbon could arise from adventitious carbon (i.e., carbon compounds adsorbed onto the surface of any sample exposed to the atmosphere). As shown in Table VII, as the oxygen flow rate (and hence, the ratio of oxygen to nitrogen) increases, the oxynitride content increases as well as does the tin oxide content. However, the tin nitride content and silicon oxynitride content is reduced. In Table VII, R equals oxygen or nitrogen.

Table VII

[0039] Table VIII shows the results for several semiconductor films that were deposited by sputtering. The semiconductor films comprised zinc, tin, oxygen, and

nitrogen. The semiconductor films were sputter deposited from a sputtering target having a zinc content of 70 atomic percent and a tin content of 30 atomic percent. The deposition occurred at a temperature of 250 degrees Celsius with a power of 400 W applied to the sputtering target. The deposition occurred for 360 seconds under an argon flow rate of 60 seem and an oxygen flow rate of 20 seem. The data shows that the mobility of the semiconductor film increases as the nitrogen flow rate (and hence, the ratio of nitrogen gas to oxygen gas) increases.

Table VIII

Zinc, oxygen, and nitrogen compounds

[0040] In order to determine the desired oxygen flow rate for forming the semiconductor film comprising zinc, oxygen, and nitrogen, the amount of oxygen may be selected so that the amount of oxygen is not sufficient to completely oxidize the zinc to form zinc oxide. If the amount of oxygen containing gas supplied is too high, the mobility of the film may not be sufficient because the film may be too oxidized. The amount of oxidation of zinc may affect the transmittance. For example, completely oxidized zinc may have a transmittance of greater than about 80 percent. One manner of determining the desired oxygen flow is to run a reactive sputtering process using argon and oxygen gases without using nitrogen gas. Experiments may be performed at different oxygen flow rates and the optical transmittance in the visible wavelength may be measured. The desired oxygen flow may be just before the film has a maximum transparency that may be achieved.

Table IX shows the optical transmittance for zinc oxide reactively sputter deposited at various oxygen flow rates. In one embodiment, the maximum preferred transmittance may be 80 percent. In other embodiments, the maximum transmittance may not be 80 percent if the glass absorption or light interference is included. The experiments may be useful when using different DC target power, different substrate temperature, or even different oxygen containing gases such as N2O.

Table IX

[0041] Another method to determine the desired oxygen gas flow is to perform the reactive sputtering to form zinc oxide under the condition of providing no nitrogen or a low amount of nitrogen as discussed above and then measure the sheet resistance. An oxygen flow rate that produces a sheet resistance between about 100 ohm/sq and 1.0 x 107 ohm/sq may be the desired oxygen flow rate.

[0042] Yet another manner for determining the desired oxygen flow rate is to take an XRD film structure measurement. Figures 2A-2E are XRD graphs for films showing the formation of zinc and zinc oxide peaks as a function of oxygen gas flow. Each of the films shown in Figures 2A-2E were deposited at an argon flow rate of 600 sccm/m3 and 1 ,000W and various oxygen flow rates.

[0043] Figure 2A shows an XRD graph of a film formed when no oxygen gas is provided during the sputtering. Several zinc peaks were produced having various intensities. A zinc (002) peak is shown for 2 theta (i.e., the angle between the

incident x-ray and the detector of the diffractometer) between about 35.5 and 37 with an intensity of about 625 counts. A zinc (100) peak is shown between about 38 and 40 with an intensity of about 450 counts. A zinc (101) peak is shown between about 42.5 and 44 with an intensity of about 1050 counts. A zinc (102) peak is shown between about 53 and 55 with an intensity of about 325 counts. A zinc (103) peak is shown between about 69.5 and 70 with an intensity of about 300. A zinc peak (110) peak is shown between about 70 and 71 with an intensity of about 275 counts. The ratio of peak heights for the zinc (002) : zinc (100) : zinc (101) : zinc (102) : zinc (103) : zinc (110) is about 2.27:1.64:3.82:1.182:1.091 :1. All peaks are marked using the International Center for Diffraction Data (ICDD) PDF2 database (rev. 2004) for phase identification.

[0044] When oxygen gas is provided at a flow rate of 50 sccm/m3, the zinc peaks diminish in intensity as shown in Figure 2B. The zinc (002) peak diminishes to about 500 counts. The zinc (100) peak diminishes to about 375 counts. The zinc (101) peak diminishes to about 750 counts. The zinc (102) peak diminishes to about 250 counts. The zinc (110) peak diminishes to about 225 counts, and the zinc (103) peak is not present. The ratio of the peak heights for zinc (002) : zinc (100) : zinc (101) : zinc (102) : zinc (110) is about 2.22:1.67:3.33:1.11 :1.

[0045] When the oxygen gas is provided at a flow rate of 100 sccm/m3, all of the zinc peaks disappear except the zinc (101) peak which has diminished to about 375 counts as shown in Figure 2C. When the oxygen gas is provided at 150 sccm/m3, the zinc peaks are completely gone, but a zinc oxide (002) peak appears between about 33.5 and 35 with an intensity of about 950 counts as shown in Figure 2D. When the oxygen flow rate is increased to 200 sccm/m3, the zinc oxide (002) peak increases in intensity to about 1 ,000 counts as shown in Figure 2E.

[0046] The amount of oxygen supplied, according to the XRD data, should be less than about 150 sccm/m3 because at 150 sccm/m3 a strong zinc oxide peak appears. It is to be understood that the flow rate of oxygen is proportional to the chamber size. Thus, for as the size of the chamber increases, the oxygen flow rate

may also increase. Similarly, as the size of the chamber is reduced, the oxygen flow rate may decrease.

[0047] To determine the desired nitrogen flow rate, XRD film structure measurements may be taken. Figures 3A-3F are XRD graphs for showing the formation of a semiconductor film according at various nitrogen gas flow rates according to one embodiment of the invention. Each of the films shown in Figures 3A-3F were deposited at an argon flow rate of 600 sccm/m3, 2,00OW, an oxygen flow rate of 100 sccm/m3, and various nitrogen flow rates.

[0048] Figure 3A shows an XRD graph of a film deposited with no nitrogen. The graph reveals several strong peaks including a peak between about 35 and about 37 of zinc oxide (101) and zinc (002) having an intensity of about 575 counts, a peak between about 38 and 40 of zinc (100) having an intensity of about 380 counts, and a peak between about 42.5 and 44 of zinc (101) having an intensity of about 700 counts. Smaller peaks of zinc oxide (002) between about 35.5 and 37 with an intensity of about 390 counts, zinc (102) between about 53 and 55 with an intensity of about 275 counts, zinc (103) between about 69.5 and 70 with an intensity of about 225 counts, and a peak of zinc (110) between about 70 and 71 with an intensity of about 225 counts are also present. The ratio of the peak heights for zinc oxide (101 ) : zinc (002) : zinc (100) : zinc (101) : zinc oxide (002) : zinc (102) : zinc (103) : zinc (110) is about 2.55:2.55:1.24:3.11 :1.73:1.22:1 :1.

[0049] When nitrogen is provided during the reactive sputtering at a flow rate of 300 sccm/m3, the zinc and zinc oxide peaks have significantly diminished to the point where zinc oxide may no longer be present as shown in Figure 3B. When the nitrogen flow rate is increased to 500 sccm/m3, all of the zinc and zinc oxide peaks have diminished and the film has an amorphous structure as shown in Figure 3C.

[0050] When the nitrogen flow rate is increased to 1 ,000 sccm/m3, two new peaks appear as shown in Figure 3D. A first peak of Zn3N2 (222) has formed between about 31 and 33 with an intensity of about 2050 counts. A second peak of Zn3N2 (411 ) has formed between about 35 and 42 with an intensity of about 1850

counts. The ratio of peak heights for Zn3N2 (222) : Zn3N2 (411 ) is about 1.11 :1. When the nitrogen gas flow rate is increased to 1 ,250 sccm/m3, the Zn3N2 (222) peak intensifies to about 2500 counts and the Zn3N2 (411) peak intensifies to about 2600 counts as shown in Figure 3E. The ratio of peak heights for Zn3N2 (222) : Zn3N2 (411) is about 0.96:1. When the nitrogen flow rate is increased to 2,500 sccm/m3, the Zn3N2 (222) peak and the Zn3N2 (411 ) weaken to about 2350 and 2050 respectively, but a new peak of Zn3N2 (400) develops between about 36 and 37.5 with an intensity of about 1700 counts as shown in Figure 3F. The ratio of peak heights for Zn3N2 (222) : Zn3N2 (411 ) : Zn3N2 (400) is about 1.38:1.21 :1.

[0051] The amount of nitrogen supplied, according to the XRD data, should be greater than about 300 sccm/m3 because at 300 sccm/m3 the zinc oxide peaks diminish significantly such that essentially no zinc oxide is present in the film. It is to be understood that the flow rate of nitrogen is proportional to the chamber size. Thus, as the size of the chamber increases, the nitrogen flow rate may also increase. Similarly, as the size of the chamber is reduced, the nitrogen flow rate may decrease.

[0052] Therefore, combining the oxygen flow rates from above and the nitrogen flow rates from above, the new semiconductor film discussed herein may be deposited under a nitrogen to oxygen flow rate ratio of greater than about 2:1. In one embodiment, the flow ratio of nitrogen to oxygen may be 10:1 to about 50:1. In still another embodiment, the flow ratio of nitrogen to oxygen may be 20:1.

[0053] To produce the semiconductor material, the flow rate of the nitrogen containing gas may be much greater than the flow rate of the oxygen containing gas as discussed above. The deposited semiconductor material may have a mobility greater than amorphous silicon. Table X shows the mobility as a function of nitrogen gas flow rate according to one embodiment of the invention.

Table X

[0054] Films deposited under conditions of 0 seem oxygen had mobility of less than 5 cm2/V-s for all flow rates of nitrogen gas. Films deposited under conditions of 25 sccm/m3 oxygen had a mobility of about 8 cm2/V-s for a nitrogen flow rate of 1 ,500 sccm/m3 and about 15 cm2/V-s for a nitrogen flow rate of 2,500 sccm/m3. Films deposited under conditions of 200 sccm/m3 oxygen had a mobility of about 1 cm2/V-s for a nitrogen flow rate of 1 ,500 sccm/m3 and a mobility of about 10 cm2/V-s for a nitrogen flow rate of 2,500 sccm/m3. Films deposited under conditions of 250 sccm/m3 oxygen has a mobility of about 5 cm2/V-s for a nitrogen flow rate of 500 sccm/m3, about 2 cm2/V-s for a nitrogen flow rate of 1 ,500 sccm/m3, and about 12 cm2/V-s for a nitrogen flow rate of 2,500 sccm/m3.

[0055] For films deposited with an oxygen flow rate of between 50 sccm/m3 and 150 sccm/m3, the mobility of the films was markedly increased over the films

deposited at oxygen flow rates of 25 sccm/m3 and below and films deposited at oxygen flow rates of 200 sccm/m3 and above. Additionally, the films deposited with an oxygen flow rate of between 50 sccm/m3and 150 sccm/m3 have mobilities far greater than amorphous silicon. At nitrogen flow rates of between 1 ,000 sccm/m3 and 2,500 sccm/m3, the mobility of the films were, in most cases, higher than 22 cm2/V-s. When compared to amorphous silicon, which has a mobility of about 1 cm2/V-s, the semiconductor films containing zinc, oxygen, and nitrogen have a significant improvement in mobility. Hence, nitrogen to oxygen gas flow ratios of about 10:1 to about 50:1 may produce semiconductor films having mobility greater than 20 times the mobility of amorphous silicon and 2 times the mobility of polysilicon. It is to be understood that while the table shows specific flow rates of nitrogen gas and oxygen gas, the flow rates of the oxygen gas and nitrogen gas are relative to the chamber size and thus, are scalable to account for different chamber sizes.

[0056] Table Xl shows the sheet resistance, carrier concentration, and resistivity as a function of nitrogen gas flow rate according to one embodiment of the invention. For flow ratios of nitrogen gas to oxygen gas between about 10:1 to about 50:1 , the sheet resistance of the semiconductor layer comprising zinc, oxygen, and nitrogen may be between about 100 ohm/sq and about 10,000 ohm/sq. With an increase in both nitrogen flow rate and oxygen flow rate, the electron carrier concentration lowers. Consequently, the resistivity increases.

Table Xl

[0057] Annealing may also significantly raise the mobility of the semiconductor film containing zinc, oxygen, and nitrogen. Table XII shows the mobility as a function of nitrogen gas flow rate after annealing according to one embodiment of the invention. After annealing, the mobility may be greater than 50 cm2/V-s. In one embodiment, the mobility may be increased to greater than 90 cm2/V-s by annealing. The annealing may occur for about five minutes in a nitrogen atmosphere at a temperature of about 400 degrees Celsius.

Table XII

[0058] The amount of dopant may also affect the mobility of the semiconductor film containing zinc, nitrogen, and oxygen. Tables XIII and XIV show the mobility, sheet resistance, carrier concentration, and resistivity for various nitrogen and oxygen flow rates when reactively sputtering a zinc sputtering target that is doped with aluminum. Thus, the amount of dopant in the sputtering target may be tuned to ensure a predetermined mobility, sheet resistance, carrier concentration, and resistivity are achieved.

Table XIV

[0059] The temperature of the susceptor may also influence the mobility of the semiconductor film. Table XV shows the mobility, sheet resistance, carrier concentration, and resistivity for various nitrogen flow rates in sputtering a zinc sputtering target at temperatures of 30 degrees Celsius, 50 degrees Celsius, and 95 degrees Celsius. As may be seen from Table XV, the reactive sputtering may effectively form a semiconductor film having mobility higher than amorphous silicon and polysilicon at temperatures significantly below 400 degrees Celsius, including temperatures approaching room temperature. Thus, even without annealing, the semiconductor film may have a higher mobility than amorphous silicon.

Table XV

[0060J While the power may be described herein as specific values, it is to be understood that the power applied to the sputtering target is proportional to the area of the target. Hence, power values between about 10 W/cm2 to about 100 W/cm2 will generally achieve the desired results. Table XVI shows the affect of the applied DC power on the mobility, carrier concentration, and resistivity for nitrogen gas flows of 1 ,500 sccm/m3 and 2,500 sccm/m3. Power levels between about 1 ,000 W and 2,000 W produce semiconductor films having a mobility significantly higher than amorphous silicon.

Table XVI

[0061] The film deposited according to the above discussed deposition techniques may comprise a ternary compound semiconductor material having zinc, nitrogen, and oxygen such as ZnNxOy. In one embodiment, the ternary compound semiconductor material may be doped such as ZnNxOy:AI. The ternary semiconductor compound may have a high mobility and a low electron carrier density when deposited at room temperature in contrast to zinc oxide which has a high electron mobility and a high electron carrier density. In one embodiment, the ternary compound has a mobility higher than 30 cm2/V-cm and an electron carrier density lower than 1.0e+19 #/cc. When the film is annealed at about 400 degrees Celsius, the mobility may be increased to greater than 100 cm2/V-cm and the electron carrier density may be lower than 1.0e+18 #/cc without changing the film crystallographic orientation and composition. The high mobility and low electron density may be achieved for the ternary compound even when the film is an amorphous compound or poorly oriented crystallographic compound.

[0062] The optical band gap of the ternary compound may also be improved compared to zinc oxide. Zinc oxide typically has a band gap of about 3.2 eV. The ternary compound comprising zinc, nitrogen, and oxygen, on the other hand, may have a band gap from about 3.1 eV to about 1.2 eV. The band gap may be adjusted by altering the deposition parameters such as nitrogen to oxygen flow ratio, power density, pressure, annealing, and deposition temperature. Due to the lower band

gap, the ternary compound may be useful for photovoltaic devices and other electronic devices. At very high processing temperatures such as 600 degrees Celsius, the ternary film may be converted to p-type or n-type semiconductor material. The annealing or plasma treatment may be fine tuned without fundamentally changing the compound structure and chemical composition. The fine tuning permits the properties of the compound to be tailored to meet the performance requirements of devices in which the compound may be used.

[0063] The ternary compound may be useful as a transparent semiconductor layer in a TFT device, a compound layer in a photovoltaic device or solar panel, or as a compound layer in a sensor device. Figures 4A-4G show a process sequence for forming a bottom gate TFT 400 according to one embodiment of the invention. The TFT may comprise a substrate 402. In one embodiment, the substrate 402 may comprise glass. In another embodiment, the substrate 402 may comprise a polymer. In another embodiment, the substrate may comprise plastic. In still another embodiment, the substrate may comprise metal.

[0064] Over the substrate, a gate electrode 404 may be formed. The gate electrode 404 may comprise an electrically conductive layer that controls the movement of charge carriers within the TFT. The gate electrode 404 may comprise a metal such as aluminum, tungsten, chromium, tantalum, or combinations thereof. The gate electrode 404 may be formed using conventional deposition techniques including sputtering, lithography, and etching. Over the gate electrode 404, a gate dielectric layer 406 may be deposited. The gate dielectric layer 406 may comprise silicon dioxide, silicon oxynitride, silicon nitride, or combinations thereof. The gate dielectric layer 406 may be deposited by well known deposition techniques including plasma enhanced chemical vapor deposition (PECVD).

[0065] Over the gate dielectric layer 406, the active channel 408 (i.e., semiconductor layer) may be formed as shown in Figure 4B. In one embodiment, the active channel 408 is annealed. In another embodiment, the active channel 408 is exposed to a plasma treatment. The annealing and/or plasma treatment may increase the mobility of the active channel 408. The active channel 408 may

comprise the ternary compound having zinc, oxygen, and nitrogen as discussed above. In one embodiment, the ternary compound is doped with aluminum. Once the active channel 408 has been deposited, the source-drain layer 410 may be deposited over the active channel 408 as shown in Figure 4C. In one embodiment, the source-drain layer 410 may comprise a metal such as aluminum, tungsten, molybdenum, chromium, tantalum, and combinations thereof. In order to define the active channel 408 and the source-drain electrodes, both the source-drain layer 410 and the active channel 408 may be etched.

[0066] As shown in Figure 4D, a mask 412 may be disposed on the source-drain layer 410. The mask 412 may have a predetermined pattern. The mask 412 may be disposed on the source-drain layer 410 by conventional techniques including photoresist deposition followed by pattern development.

[0067] The active channel 408 and the source-drain layer 410 may be simultaneously etched as shown in Figure 4E. Figure 4F shows a top view of Figure 4E. As can be seen in Figures 4E and 4F, the active channel 408 may be exposed by the etching. In one embodiment, the active channel 408 may be exposed by wet etching both the source-drain layer 410 and a portion of the active channel 408. In another embodiment, the source-drain layer 410 may be dry etched followed by a wet etching of a portion of the active channel 408. In another embodiment, the source-drain layer 410 may be etched without etching the active channel 408. In one embodiment, the dry etching may be performed with a gas containing an element selected from chlorine, oxygen, fluorine, or combinations thereof.

[0068] Following the exposure of the active channel 408, source-drain electrodes may be defined by dry etching the source-drain layer 410 using the active channel 408 as an etch stop layer. Figure 4G shows a top view of the exposed active channel 408 and defined source electrode 414 and drain electrode 416. The active channel 408 may function as an etch stop layer during dry plasma etching because the ternary compound comprising zinc, oxygen, and nitrogen (and in certain embodiments, aluminum) may not be effectively etched by plasma.

[0069] Figure 5 is a schematic cross sectional view of an etch stop TFT 500 according to one embodiment of the invention. The etch stop TFT may comprise a substrate 502, a gate electrode 504, and a gate dielectric layer 506. The etch stop TFT 500 is similar to the bottom gate TFT shown above in Figures 4A-4G, but an etch stop 510 may be present over the active channel 508 between the source electrode 512 and the drain electrode 514. The materials for the substrate 502, gate electrode 504, gate dielectric 506, active channel 508, source electrode 512, and drain electrode 514 may be as described above in relation to the bottom gate TFT. The etch stop 510 may comprise a dielectric material comprising silicon and one or more of oxygen and nitrogen.

[0070] Figure 6 is a schematic cross sectional view of a top gate TFT 600 according to one embodiment of the invention. The top gate TFT 600 may comprise a substrate 602 having a light shielding layer 604 deposited thereon. A dielectric layer 606 may be deposited over the light shielding layer 604. A source electrode 608 and a drain electrode 610 may be deposited over the dielectric layer 606. The active channel layer 612 may be deposited over the source electrode 608 and the drain electrode 610. A gate dielectric layer 614 may be deposited over the active channel 612 and the gate electrode 616 may be deposited over the gate dielectric layer 614. The materials for the substrate 602, gate electrode 616, gate dielectric 614, active channel 612, source electrode 608, and drain electrode 610 may be as described above in relation to the bottom gate TFT. In forming the top gate TFT 600, the channel and electrode contact area may be formed by wet etching or dry etching followed by wet etching. Then, the contact area may be defined by dry etching using the active channel as an etch stop layer.

[0071] Figure 7 is a schematic view of an active-matrix LCD 700 according to one embodiment of the invention. Figure 7 shows a TFT substrate and a color filter substrate with a liquid crystal material sandwiched therebetween. The TFT controls a current to the pixel electrode creating an electric field to control the orientation of the liquid crystal material and thus the amount of light that is transmitted through the color filter. The TFTs are arranged in a matrix on a glass substrate. To address a

particular pixel, the proper row is switched on, and then a charge is sent down the correct column. Since all of the other rows that the column intersects are turned off, only the capacitor at the designated pixel receives a charge. The capacitor is able to hold the charge until the next refresh cycle. If the amount of voltage supplied to a crystal is controlled, the crystal may untwist only enough to allow some light through.

[0072] The active matrix LCD 700 shown in Figure 7 may be controlled by a TFT 714. The TFT 714 may turn pixels on or off. The LCD 700 may comprise a bonding pad 706, a pixel electrode 708, a storage capacitor 728, a polarizer 702, a substrate 704, an alignment layer 710, a spacer 712, a short 716, a seal 718, a black matrix 720, a color filter 724, and a common electrode 724.

[0073] Figure 8 is a schematic view of an active-matrix OLED 800 according to one embodiment of the invention. Figure 8 shows a TFT controlling the amount of current applied to the emissive organic layers of the OLED. Active-matrix OLEDs have full layers of cathode, organic molecules and anode, but the anode layer overlays a TFT array that forms a matrix. The TFT array itself is the circuitry that determines which pixels get turned on to form an image. Active-matrix OLEDs consume less power than passive-matrix OLEDs because the TFT array requires less power than external circuitry, so they are efficient for large displays. Active- matrix OLEDs also have faster refresh rates suitable for video. Active-matrix OLEDs may be used in computer monitors, large screen TVs, electronic signs, and electronic billboards.

[0074] The OLED 800 may be controlled by a TFT 802 that turns the pixels on or off. The OLED 800 comprises a TFT 802, an anode 804, a hole injection layer 806, an ionization layer 808, a buffer layer 810, a transparent cathode 812, an emissive layer 814, and an encapsulation layer 816.

[0075] Figures 9A-9C show the Vth for various active channel lengths and widths. Figure 9A shows the Vth for a active channel length of 40 μm and a width of

10 μm. Figure 9B shows the Vth for a active channel length of 80 μm and a width of

10 μm. Figure 9C shows the Vth for a active channel length of 80 μm and a width of

20 μm. In each of Figures 9A-9C, it is shown that the ternary compound active layer has a high on-off ratio and a high current.

[0076] Figures 10A-10C show a comparision of the Vth for active channels having a common length and width. The active channel width is 40 μm and the width is 10 μm. Figure 10A is the Vth for amorphous silicon. Figure 10B is the ternary compound without annealing. Figure 10C is the ternary compound after annealing. The ternary compound TFT of Figure 10B has a drain-source current at Vg = 1 that is higher than the drain-source current for amorphous silicon at 10 V. Therefore, the non-annealed film is about 10 times better than amorphous silicon.

[0077] The annealed film in Figure 10C is even better. The annealed film has a high saturation current as compared to the non-annealed film. The source-drain current for the annealed film at Vd = 0.1 V is close to the amorphous silicon TFT's current at Vd = 10V. Thus, the annealed film is about 100 times better than the amorphous silicon.

[0078] The performance of the TFTs described above can be adjusted or tuned by changing the active layer carrier concentration, the active layer mobility, and the characteristics of the active layer at the interface with other layers. The TFTs may be tuned by changing the nitrogen containing gas flow rate during the film deposition. As noted above, the ratio of the nitrogen containing gas to the oxygen containing gas used in sputter deposition of the active layer may affect the mobility, carrier concentration, and other factors. A user may set a predetermined value for the carrier concentration, the mobility, or other characteristic and then adjust the nitrogen to oxygen flow ratio accordingly to produce the desired film properties. The adjustment may even occur in response to an in situ measurement to permit real time control of the deposition process.

[0079] The TFTs may also be tuned by the amount of aluminum doping. The amount of aluminum doping may be predetermined so that a sputtering target of appropriate composition may be disposed within the processing chamber. Additionally, the TFTs may be tuned by annealing and/or plasma treating the active

layer after deposition or during integration with other films. As noted above, heat treating the ternary compound may increase the mobility of the film.

[0080] TFTs comprising oxygen, nitrogen, and one or more elements selected from the group consisting of zinc, tin, gallium, indium, and cadmium have increased mobility over TFTs made with amorphous silicon. The increased mobility of the TFTs permits the TFTs to be used not only for LCDs, but also for the next generation of displays, OLEDs.

[0081] While the foregoing is directed to embodiments of the present invention, other and further embodiments of the invention may be devised without departing from the basic scope thereof, and the scope thereof is determined by the claims that follow.