# SIEMENS

# **TELEPERM M**

AS 235 H Automation System

Description

C79000-T8076-C484-04

## SIEMENS

We have checked the contents of this manual for agreement with the hardware and software described. Since deviations cannot be precluded entirely, we cannot guarantee full agreement. However, the data in the manual are reviewed regularly and any necessary corrections included in subsequent editions. Suggestions for improvement are welcome.

Technical data subject to change.

Siemens Aktiengesellschaft

The reproduction, transmission or use of this document or its contents is not permitted without express written authority. Offenders will be liable for damages. All rights, including rights created by patent grant or registration of a utility model or design, are reserved.

Copyright © Siemens AG 1993–2002 All Rights Reserved

Order No.: C79000-T8076-C484 Printed in the Federal Republic of Germany

#### Contents

| Preface                                                             | 0                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Abbrevia                                                            | ntions 0-4                                                                                                                                                                                                                                   |

| 1                                                                   | System Summary 1–                                                                                                                                                                                                                            |

| 1.1                                                                 | Basic Structure of the AS 235 H System 1-                                                                                                                                                                                                    |

| 1.2<br>1.2.1<br>1.2.1.1<br>1.2.1.2<br>1.2.1.3<br>1.2.2<br>1.2.3     | AS 235 H Modes                                                                                                                                                                                                                               |

| 1.2.4                                                               | Operation as a Non–Redundant System 1–1                                                                                                                                                                                                      |

| 1.3<br>1.3.1<br>1.3.2<br>1.3.3<br>1.3.4                             | Mode Transition1–14Mode Transition during Start–up1–14Operator Controlled Mode Transition1–14Automatic Mode Transition1–14Mode Transition1–14Mode Transition after a Fault has Occurred1–14                                                  |

| 2                                                                   | Method of Operation 2-                                                                                                                                                                                                                       |

| 2.1                                                                 | Initial Loading of the System Software 2-                                                                                                                                                                                                    |

| 2.2                                                                 | Start-up Behavior                                                                                                                                                                                                                            |

| 2.3                                                                 | Loading and Filing 2-                                                                                                                                                                                                                        |

| 2.4                                                                 | Synchronization                                                                                                                                                                                                                              |

| 2.5<br>2.5.1<br>2.5.1.1<br>2.5.1.2<br>2.5.1.3<br>2.5.1.4<br>2.5.1.5 | Keyboard input2-4Additional operator input and help programs2-4H mode control2-4EAVU status display2-4Hardware flags after synchronization faults2-1EAVU flags after synchronization faults2-1Software flags after synchronization faults2-1 |

| 2.6<br>2.6.1<br>2.6.2<br>2.6.3                                      | H mode indication2–12LEDs on H–related modules in the central unit2–12Displays2–14H–related I&C alarms (LTM)2–14                                                                                                                             |

| 2.7                                                                 | Printout                                                                                                                                                                                                                                     |

| 3                              | Configuration                                                                                                                              | 3–1        |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 3.1                            | Difference between the AS 235 H and AS 235 standard system software                                                                        | 3–1        |

| 3.2<br>3.2.1<br>3.2.2<br>3.2.3 | Additional functions<br>Function flags in GB.ORPA<br>Indication of a failure in the I/O system (EAVU driver block)<br>Interrupt processing | 3–2<br>3–3 |

| 4                              | Fault handling                                                                                                                             | 4–1        |

| 4.1                            | Specific system software test routines                                                                                                     | 4–1        |

| 4.2                            | Fault reaction                                                                                                                             | 4–2        |

| 4.3                            | Fault indications                                                                                                                          | 4–4        |

| 4.4                            | Fault analysis                                                                                                                             | 4–4        |

| 4.5                            | Fault elimination                                                                                                                          | 4–5        |

| 5                              | Function blocks                                                                                                                            | 5–1        |

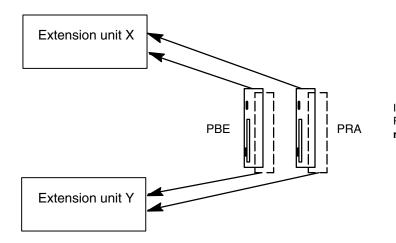

| 5.1                            | Testable binary input module (PBE) 6DS1618-8CA                                                                                             |            |

|                                |                                                                                                                                            |            |

| 5.2                            | Testable relay output module (PRA) 6DS1606-8BA                                                                                             | 5–3        |

| 5.3                            | Redundant utilization of the modules                                                                                                       | 5–4        |

### Appendix

| Upgrading instructions for memory module 6DS1844–8FA and system software version G | A–1 |

|------------------------------------------------------------------------------------|-----|

| Index                                                                              | A–3 |

## Preface

This description deals with the system software and method of operation of the fault–tolerant AS 235 H automation system.

Method of operation, configuration, bus communication, function block processing, etc. of the AS 235 standard automation system are discussed in the Description "AS 235 Variant G" (Order No. C79000-T8076-C416).

The hardware configuration is described in the AS 235 H System Manual (Order No. C79000-G8076-C293).

#### Abbreviations

| I, II                                            | Identification numbers (Roman numerals) of the redundant subsystems (redundancies) within a multi-redundant system.                                                                                                                                                                                 |

|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AA                                               | Analog output module                                                                                                                                                                                                                                                                                |

| AE                                               | Analog input module                                                                                                                                                                                                                                                                                 |

| AF                                               | Remote bus connector board                                                                                                                                                                                                                                                                          |

| AS                                               | Automation system                                                                                                                                                                                                                                                                                   |

| AZR                                              | Flag register of the CPU 235                                                                                                                                                                                                                                                                        |

| B                                                | Backup (CPU status = synchronization and updating)                                                                                                                                                                                                                                                  |

| BA                                               | Binary output module                                                                                                                                                                                                                                                                                |

| B&B                                              | Operator control and monitoring                                                                                                                                                                                                                                                                     |

| BE                                               | Binary input module                                                                                                                                                                                                                                                                                 |

| BGF                                              | Module fault                                                                                                                                                                                                                                                                                        |

| BGNR                                             | Module number                                                                                                                                                                                                                                                                                       |

| BGT                                              | Subrack                                                                                                                                                                                                                                                                                             |

| BKA                                              | Operator input channel interface module                                                                                                                                                                                                                                                             |

| BKU                                              | Operator input channel switchover (video relay and adapter cable)                                                                                                                                                                                                                                   |

| BL                                               | Blinking clock–pulse generator module                                                                                                                                                                                                                                                               |

| CPU 235 H                                        | Central processing unit 235 H                                                                                                                                                                                                                                                                       |

| CS275                                            | LAN for linking TELEPERM M systems (coupling systems)                                                                                                                                                                                                                                               |

| DG                                               | Diagnostic unit                                                                                                                                                                                                                                                                                     |

| DGA                                              | Diagnostic unit interface module                                                                                                                                                                                                                                                                    |

| DMA                                              | Direct memory access                                                                                                                                                                                                                                                                                |

| E/A<br>EABA<br>EANK<br>EAVU<br>EE<br>ES<br>EPROM | Input and output (I/O)<br>I/O bus interface module<br>One–out–of–n code; TELEPERM M procedure for detecting I/O addres-<br>ses with no or multiple assignments<br>I/O comparator and switchover module<br>Extension unit<br>Extension cabinet<br>Ultraviolet erasable programmable read–only memory |

| F                                                | Fail–safe (by redundancy) or mode: failure                                                                                                                                                                                                                                                          |

| FDC                                              | Floppy–disk controller                                                                                                                                                                                                                                                                              |

| FIFO                                             | First in first out (queuing or handling hierarchy)                                                                                                                                                                                                                                                  |

| FTSP                                             | Error when testing the coil voltage                                                                                                                                                                                                                                                                 |

| GE                                               | Basic unit                                                                                                                                                                                                                                                                                          |

| GS                                               | Basic cabinet                                                                                                                                                                                                                                                                                       |

| H                                                | Fault–tolerant (by redundancy)                                                                                                                                                                                                                                                                      |

| HF                                               | H and F in compatible combination                                                                                                                                                                                                                                                                   |

| KF                                               | Channel fault                                                                                                                                                                                                                                                                                       |

| L+                                               | Positive supply voltage, 24 V rated value                                                                                                                                                                                                                                                           |

| LAN                                              | Local area network; mid–range communications bus                                                                                                                                                                                                                                                    |

| LED                                              | Light emitting diode                                                                                                                                                                                                                                                                                |

| LOES                                             | Clearing the user memory by entering the keyboard command "LOES;"                                                                                                                                                                                                                                   |

| LTM                                              | I&C alarm                                                                                                                                                                                                                                                                                           |

| Μ    | Master (CPU mode)                                                          |

|------|----------------------------------------------------------------------------|

| Μ    | Earth, negative pole                                                       |

| MDA  | Mini floppy disk interface module                                          |

| MDE  | Mini floppy disk unit                                                      |

| MDT  | Mean downtime (mean time between the occurrence of a failure and ope-      |

|      | ration restart)                                                            |

| ML   | Alarm logic module                                                         |

| MTBF | Mean time between failures (mean time between two failure occurrences,     |

|      | i.e. faultless interval)                                                   |

| MZ   | Off-load earth, reference potential for analog inputs                      |

| N–AS | Local bus interface module for automation systems                          |

| NAU  | Power failure                                                              |

| N8   | TELEPERM M local bus interface, 8 bits on CS 275 bus system                |

| N8–H | N8 in a fault tolerant 1–out–of–2 master/reserve configuration of a redun- |

|      | dant automation system                                                     |

| NV   | Local bus distributor                                                      |

| INV  | Local bus distributor                                                      |

| OS   | Operator control and monitoring system                                     |

| Р    | Passive (asynchronous CPU status; no N8–H accesses etc.)                   |

| PBE  | Testable binary input module                                               |

| PBT  | Process communication keyboard (TELEPERM M AS accessory)                   |

| PE   | Protective earth, cabinet potential                                        |

| PESP | Peripheral memory area                                                     |

| PM   | L+ for alarm purposes                                                      |

| PRA  | Testable relay output module                                               |

| PROM | Programmable read-only memory                                              |

| PS   | L+ for logic "1" with 24-V inputs                                          |

| ΡÜ   | L+ for monitoring purposes                                                 |

| PU   | Process interrupt                                                          |

| PU5  | Standard: unassigned process interrupt No. 5 (PU5) which is exclusively    |

|      | used for redundancy-related purposes                                       |

| PUM  | Buffer module                                                              |

| QVZ  | Time-out during memory or peripheral access                                |

| R    | Standby (CPU mode)                                                         |

| RAM  | Random access memory                                                       |

| RDY  | Ready                                                                      |

| ROM  | Read–only memory                                                           |

| RSOF | Software reset                                                             |

| SAE  | Cabinet connection element                                                 |

| SB   | Synchronization module                                                     |

| SED  | Cabinet power supply diode                                                 |

| SEP  | Standard plug–in station in a subrack, 15.24 mm wide                       |

| SES  | Cabinet power supply unit                                                  |

| SF   | Signal interface module                                                    |

| SF61 | Signal interface module in slot address 61 (mnemonic name for a group      |

| 0101 | interrupt module in this slot; 48–binary input module)                     |

| SP   | Memory module                                                              |

| STA  | Starting block processing                                                  |

| STO  | Halting block processing                                                   |

| SV   | Power supply module                                                        |

| SVE  | Power supply unit                                                          |

| SVME | Power supply unit for extension unit                                       |

| SW   | Software                                                                   |

|      |                                                                            |

| ТМ    | TELEPERM M                                         |

|-------|----------------------------------------------------|

| UI    | Inductive bus converter unit for CS275             |

| VD 11 | Logic diode module for messages                    |

| VKB   | Comparator coupler module                          |

| VR    | Video relay                                        |

| ZE    | Central processing unit                            |

| ZEP   | Central earthing point                             |

| ZRS   | Central reset                                      |

| ZT    | Central unit (subrack containing CPU I and CPU II) |

## 1 System Summary

## 1.1 Basic Structure of the AS 235 H System

The AS 235 H automation system is the fault–tolerant version of the AS 235 automation system. Fault–tolerance is achieved by redundant <sup>1)</sup> use of two central processing units. The second CPU continues operation if the first unit fails. Redundancy can only be maintained if **all** resources are monitored, serviced and repaired.

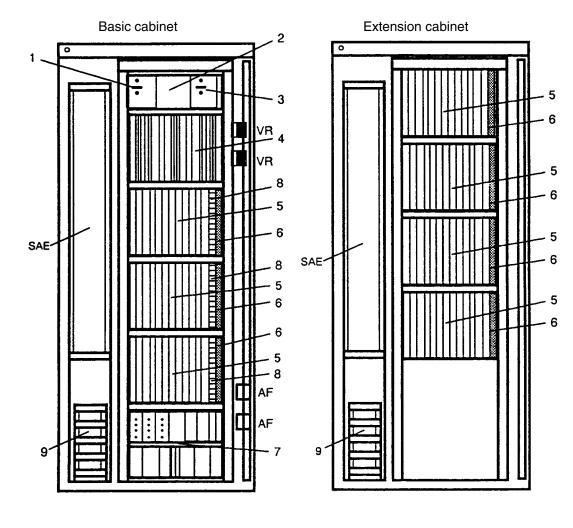

This description only contains a general layout plan of the AS 235 H system (see Fig. 1.1). Please refer to the AS 235 H Manual (Section 1) for detailed hardware descriptions.

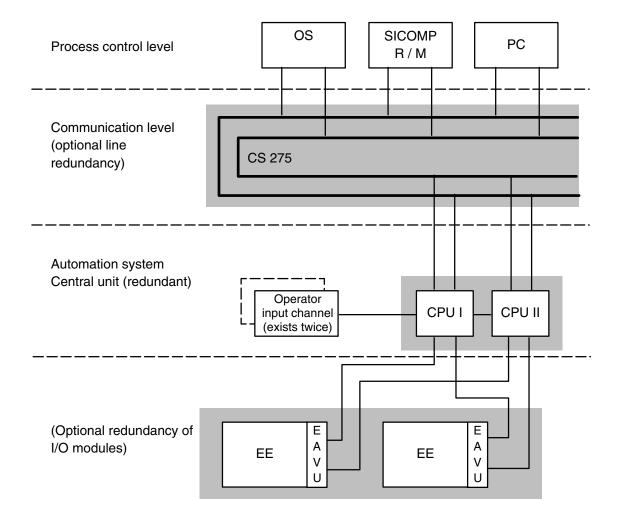

Fig. 1.2 shows the redundant structure of the AS 235 H system. The central unit consists of two central processing units with synchronous clock and command execution which operate as a 1–out–of–2 system. The second, faultless CPU of a redundant system continues process execution if the master CPU fails or contains a hardware fault.

The I/O system may also be configured in a redundant manner (see Chapter 3). This is indicated by the two hatched extension units in Fig. 1.2. Fig. 1.2. shows a typical configuration, other structures are possible.

Redundancy (to DIN 4001) means that more resources per unit are available than are actually required for performing the specified task.

- AF Remote bus connector board

- SAE Cabinet connecting elements

- VR Video relay

- 1

- Power supply unit I (5 V) Buffer module (24 V) 2

- Power supply unit II (5 V) Basic unit (ZE I + ZE II) 3

- 4

- Extension unit (EE)

- 5 6 I/O comparator and switchover module

- 7 Cabinet power supply unit with:

- Circuit breakers

- Socket outlets

- Alarm logic modules

- Logic diode modules

- Cabinet power supply diode

- Inductive bus converter unit

- Blinking clock-pulse generator module

- Group interrupt module (option) 8

- 9 Process cable clamping bar

Fig. 1.1 AS 235 H cabinet layout

| OS<br>SICOMP<br>PC |   | Operator control and monitoring system<br>SICOMP computer system<br>Personal computer |

|--------------------|---|---------------------------------------------------------------------------------------|

| CS 275             | = | Bus system                                                                            |

| ZE I               | = | Central processing unit I                                                             |

| ZE II              | = | Central processing unit II                                                            |

| EE                 | = | Extension unit                                                                        |

| EAVU               | = | I/O comparator and switchover module                                                  |

|                    |   |                                                                                       |

## 1.2 AS 235 H Modes

The following modes can be assumed by either central processing unit. Various combinations are possible.

| Master (M)  | The CPU has access to all its locally assigned modules. It is thus able to execute the application program in the same manner as a standard automation system.<br>The mode of the second CPU may be: standby, backup, passive or failure.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reserve (R) | CPU and master CPU execute all programs in synchronous operation<br>(clock and instructions). The comparators on the comparator coupler<br>module (VKB) and the I/O comparator and switchover modules (EAVU)<br>monitor the data, address, and control signals for discrepancies. The<br>standby CPU continues process execution in the event of a master CPU<br>failure.<br>The second CPU is in master mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Passive (P) | The CPU executes its program independently of the other CPU. Access to the CS 275 bus system and the I/O system are disabled by the hardware. The CPU has access to its local MDA and the BKAs. Monitors and printers are connected to the master CPU via an operator input channel switchover unit. Since the keyboards are connected to both CPUs, keyboard inputs are processed simultaneously by both CPUs. Keyboard inputs to the passive CPU, however, are not displayed. The connecting cables of configuring keyboard (not PBT) and monitor may temporarily be connected directly (without switchover function) to the passive CPU (for special tasks or maintenance purposes). Application program execution is halted when a CPU enters passive mode. The CPU assumes STO mode (block execution is halted). The mode of the second CPU may be: master, passive or failure. |

| Backup (B)  | This mode indicates a transition from passive to standby mode. The pas-<br>sive CPU is first synchronized with the master CPU. Subsequently, the<br>content of the user memory is transferred from the master CPU to the<br>backup CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|             | Application program execution is continued synchronously in both CPUs.<br>The mode of the second CPU is, and remains, master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

Fault (F)A CPU that has been identified as the cause of asynchronous operation<br/>between the two CPUs will assume failure mode. The CPU also assumes<br/>failure mode if a fault has been detected during start-up.

Although the CPU may still be operational it is not possible to establish synchronous operation between the CPUs (in contrast to passive mode). The CPU is also in failure mode after a power failure or a breakdown of a central module. The CPU is then no longer operational.

The cause of the failure can be determined by means of an information program (see Chapter 2.5.1.3). User program execution is stopped and the CPU assumes STO mode if a CPU enters failure mode after a malfunction has been located.

Once the fault has been repaired and the start–up selftest routine passed, failure mode can only be left by a restart (either central reset = ZRS or software reset = RSOF).

The mode of the second CPU may be: master, passive or failure.

The modes (except passive and failure) are independent of the STO (block execution halt) or STA (block execution start) modes. These modes only refer to **user program** execution.

STO mode is set when a CPU transitions to passive or failure mode. Since user program execution is not performed in this CPU, I/O access is not performed either. The latter would cause QVZ (time–out) and a corresponding I&C fault alarm.

Brief summary of the modes:

|     | Explanations                                                                                                     |

|-----|------------------------------------------------------------------------------------------------------------------|

| MR  | Synchronous program execution                                                                                    |

| R M | Synchronous program execution                                                                                    |

| МВ  | Synchronization of CPU II,<br>User program transfer to CPU II                                                    |

| ВМ  | Synchronization of CPU I,<br>User program transfer to CPU I                                                      |

| MP  | Asynchronous operation<br>User program is not executed in CPU II                                                 |

| P M | Asynchronous operation<br>User program is not executed in CPU I                                                  |

| MF  | Asynchronous operation: CPU II cannot be synchronized, start-up fault or power failure of module fault in CPU II |

| F M | Asynchronous operation: CPU I cannot be synchronized , start-up fault or power failure or module faut in CPU I   |

| P F | User program is not executed in CPU I, start-up fault or power fai-<br>lure or module fault in CPU II            |

| F P | User program not executed in CPU II, start-up fault or power fai-<br>lure or module fault in CPU I               |

| P P | User program is not executed in CPU I and CPU II                                                                 |

| FF  | Start-up fault or power failure or module fault in CPU I and CPU I                                               |

Table 1.1 Modes

#### 1.2.1 Redundant Mode

Both CPUs operate synchronously (clock and instruction execution) in redundancy mode (M/R, R/M). The other CPU continues process execution if one CPU fails.

Synchronous operation also includes the M/B and B/M modes which are no redundant modes, however (see Chapter 1.2.2).

The comparator coupler module (VKB) in the central unit and the I/O comparator and switchover modules (EAVU) in th extension units monitor whether the bus signals to and from both CPUs are identical.

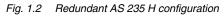

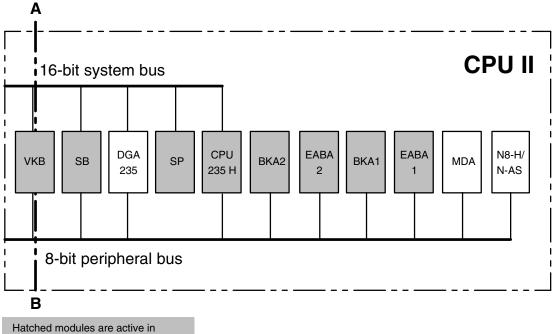

Fig. 1.3 shows the modules that are active in synchronous operation. It is assumed that CPU I is the master (see Chapter 1.2).

The clock pulse signals for the CPU modules are generated on the synchronization modules. The incoming control signals and clock pulses are synchronized on this module too.

The comparator coupler module monitors whether the control, data and address signals are identical in synchronous operation, and provides cross coupling of the N8–H and MDA access operations.

An interrupt signal is sent to each CPU if the modules detect a discrepancy between the bus signals in synchronous operation. The subsequent fault reaction is discussed in Chapter 4.2.

Hatched modules are active in synchronous operation (CPU I is master here)

N-AS Local bus interface module for automation systems N8-H Local bus interface module MDA Mini floppy disk interface module BKA Operator input channel interface module I/O bus interface module EABA CPU Central processing unit module DGA 235 Diagnostic unit interface module SB Synchronization module SP Memory module VKB Comparator coupler module ZE I Central processing unit I

ZE I Central processing unit I ZE II Central processing unit II

ZE II Central processing unit II

Fig. 1.3 Synchronous operation of the AS 235 H central unit

#### 1.2.1.1 Redundant Operator Input Channels

The following allocation is always valid in synchronous operation irrespective of the currently active master CPU. The necessary signal routing is performed by the comparator coupler module.

Keyboard inputs are entered in parallel into both CPUs.

The image output of an operator input channel is performed via the respective operator input channel interface module of both CPUs.

A switchover unit displays the BKA1 display contents of CPU I on the monitor of operator input channel 1.

Printer output of operator input channel is disabled by CPU II in BKA 1. Printer output of operator input channel is disabled by CPU I in BKA 2.

#### 1.2.1.2 Redundant I/O System

Two redundant I/O buses provide the connection to the extension units (EE) via the I/O comparator and switchover modules (EAVU) (see Fig. 1.2).

One redundant I/O bus is allocated to the extension units in the basic cabinet, the second I/O bus to the extension units in the extension cabinet.

The I/O bus **within** an extension unit is **not** redundant. Redundant configuration of the I/O system requires each redundant group of I/O modules to be accommodated in a different extension unit (see Chapter 3).

The I/O comparator and switchover modules guarantee that the connection between the master CPU and the extension units is maintained when one CPU or one I/O bus line fails.

In synchronous operation, read data is transferred to both CPUs simultaneously, whereas write command signals are transferred to the I/O modules from one CPU only. The signals are compared during read and write operations. An interrupt signal is sent to each CPU if the I/O comparator and switchover modules detect a discrepancy between the signals. The subsequent fault reaction is discussed in Chapter 4.2.

#### 1.2.1.3 Redundant N8-H/N-AS Bus Interface Unit and Mini Floppy Disk Interface Module (MDA)

The following rules apply for synchronous operation:

Access to the CS 275 bus system and to the mini floppy disk unit (MDE) is performed via the respective N8–H/N–AS and MDA modules of the master CPU. The necessary signals for synchronous operation of the standby CPU are cross–coupled via the comparator coupler module (VKB).

The system recognizes a failure of the N8-H/N-AS module and transfers mastership to the other CPU (e.g. from M/R to R/M). This transfer selects the other N8-H/N-AS and MDA modules and initiates an I&C fault alarm (see Chapter 2.6.3). A malfunction of the N8-H/N-AS module is indicated by the I&C alarm S 374. The I&C alarm S 315 (DAUERDMA) signals a fault during N8–H/N–AS or MDA direct memory access.

The N8-H/N-AS module in the standby CPU processes selftest routines, and is parameterized by the CPU once mastership has been transferred to the second CPU.

The optional line redundancy of the CS 275 bus system is independent of the interface redundancy. This means that the line redundancy is retained after a CPU failure, and vice versa.

#### 1.2.2 Synchronous Operation

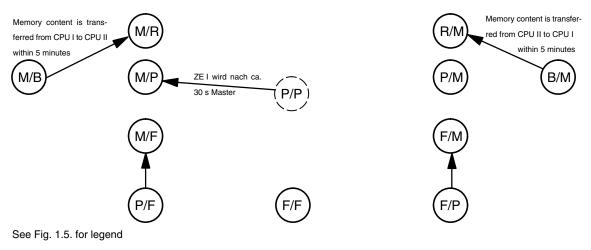

Synchronous operation includes redundancy mode (M/R and R/M) and the two temporary modes M/B and B/M. These two modes only differ from redundant mode in that the memory contents of the master CPU has not yet been transferred to the memory of the backup CPU.

The two CPUs are already synchronous with regard to clock pulse and instruction sequence; the backup CPU, however, is not yet in a position to accept mastership in the event of a master CPU failure. Monitoring synchronous operation (i.e. monitoring the identity of the bus signals from and to both CPUs) is already performed by the VKB and EAVU modules during backup operation.

#### 1.2.3 Asynchronous Operation

Both CPUs operate independently of each other in asynchronous mode. This means that they execute different instructions.

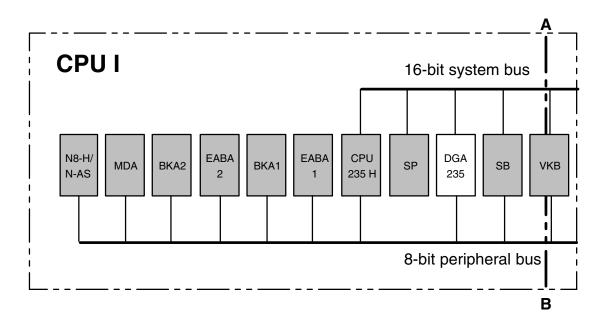

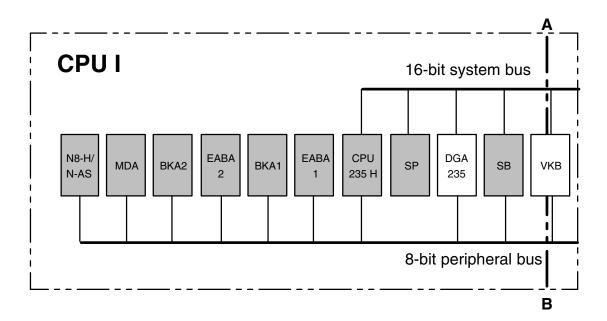

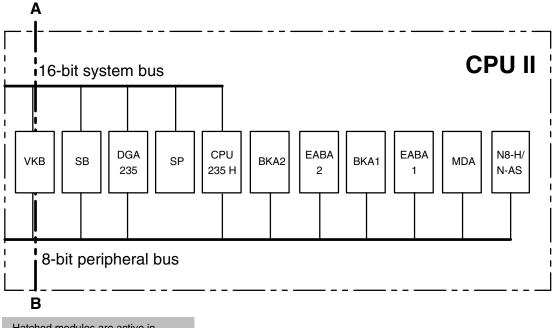

Asynchronous operation includes the M/P, P/M, M/F, F/M, P/F, F/P, P/P, and F/F modes. Fig. 1.4 shows the active modules of CPU I in asynchronous mode; CPU I is master. The master CPU operates in the same manner as the central unit of a standard automation system. The synchronization module is solely used for generating the system clock pulse for the CPU. The comparator coupler module (VKB) is not required for asynchronous operation. The other CPU cannot influence the master CPU.

In order to restore the fault-tolerant features of the automation system, asynchronous operation should be terminated as soon as possible by synchronizing the passive CPU.

Hatched modules are active in asynchronous operation (CPU I is master here)

N-AS Local bus interface module for automation systems N8-H Local bus interface module Mini floppy disk interface module MDA BKA Operator input channel interface module I/O bus interface module EABA CPU Central processing unit module DGA 235 Diagnostic unit interface module SB Synchronization module SP Memory module VKB Comparator coupler module ZE I Central processing unit I

ZE I Central processing unit I ZE II Central processing unit II

ZE II Central processing unit II

Fig. 1.4 Asynchronous operation of the AS 235 H central unit

#### 1.2.4 Operation as a Non–Redundant System

With a single central unit, the AS 235 H can be used as a non-redundant system. Compared with AS 235 Standard, such a system can easily be upgraded to a redundant system. Merely the missing modules in the central unit and the signalling logic module in the power supply tier need to be installed.

As a non-redundant system, the AS 235 H may be used with CPU I or CPU II. The mode after startup is either M/F or F/M. The missing central processing unit (CPU II or CPU I) is thus treated as if it were defective or without power. The master CPU works in the same manner as the central unit of the standard AS. The statements made in this description for M/F or F/M mode and asynchronous mode apply.

## 1.3 Mode Transition

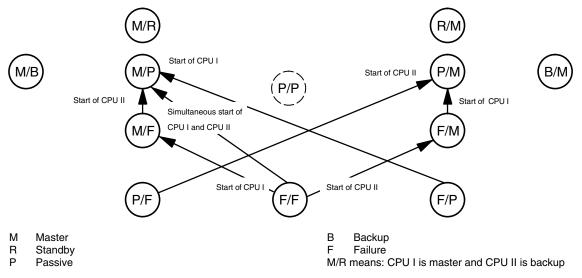

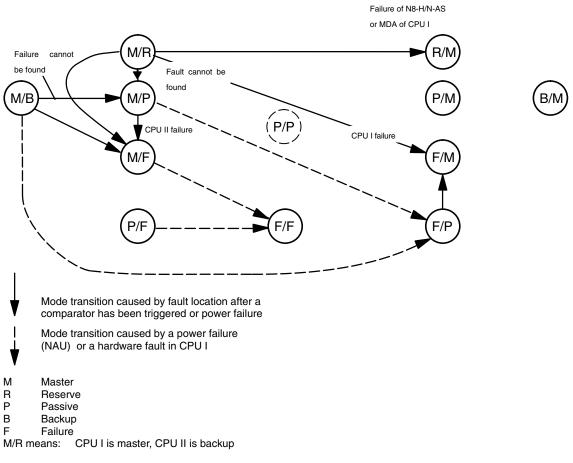

Figs. 1.5 to 1.8 show all possible mode transitions of an AS 235 H system. For clarity reasons they are illustrated in four different figures.

The operating state of both CPUs is always marked by a circle.

for instance, means that CPU I is master and CPU II is passive

An arrow marks a status transition; the text next to the arrow indicates the cause of status transition.

The interim state P/P is represented as a dotted circle.

#### **1.3.1** Mode Transition during Start–up (Fig. 1.5)

The start–up response is the same after a voltage recovery or after a central reset (ZRS). The starting CPU assumes mastership, unless the other CPU is master. In this case, the starting CPU becomes "passive".

The starting CPU assumes failure mode if the selftest routine detects a malfunction during start–up. (This possibility is not depicted in Fig. 1.5)

CPU I becomes master if both CPUs are started simultaneously even if CPU II has a "lead" of less than one second. A lead of more than one second is no longer considered as a simultaneous start.

The mode is only changed after an RSOF or LOES keyboard command if the CPU mode was previously in failure mode. The mode is changed to "master" after the selftest routine has been passed if the other CPU was in passive mode (otherwise to "passive").

Note

Power supply must be redundant. Mains failure in both CPUs is thus considered as a double fault. When both CPUs start up simultaneously, CPU I becomes master, not the CPU that was master before the mains failure.

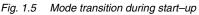

#### 1.3.2 Operator–Controlled Mode Transition (Fig. 1.6)

Apart from inputs that are required for synchronization, inputs are only permitted in STO mode. The transition from M/P to M/B or from P/M to B/M indicates the transition from asynchronous to synchronous mode. The mode changes from M/R to R/M once the user memory contents has been transferred from the master CPU to the backup CPU.

P/P mode is assumed briefly (for approximatel one second) as an interim state when the system transitions from M/P to P/M or vice versa. The reason is that the master CPU becomes passive first before the other CPU becomes master.

Possible operator inputs are discussed in Chapter 2.5.

Fig. 1.6 Operator–controlled mode transition

#### **1.3.3 Automatic Mode Transition** (Fig. 1.7)

The system transitions from M/B or B/M to M/R or R/M once the complete user memory contents has been transferred from the master CPU to the backup CPU. A memory size of 3 MB takes approximately five minutes in STA mode or 40 seconds in STO mode. In STA mode, the user program execution is continued without interruption.

CPU I automatically assumes mastership if, due to a malfunction, the automation system remains longer than 30 seconds in P/P mode. User program execution is stopped for safety reasons; CPU I assumes STO mode.

Fig. 1.7 Automatic mode transition

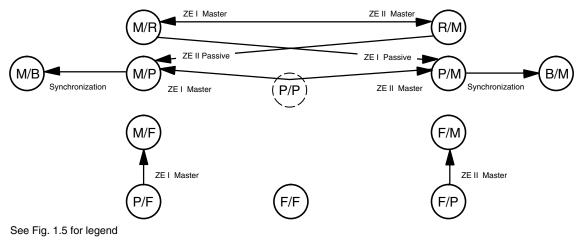

#### **1.3.4** Mode Transition after a Fault has Occurred (Fig. 1.8)

The fault can be a power failure, hardware failure or an actuated ZRS pushbutton.

Such a fault triggers the comparators on the comparator coupler module (VKB) or the I/O comparator and switchover modules (EAVU) which release an interrupt signal. Subsequently, both CPUs start executing diagnostics routines.

After the fault has been located, the CPU which caused the fault assumes "Failure" mode and the other CPU continues user program execution. The defective module must be replaced if the fault is a hardware fault.

The standby CPU assumes passive mode if the fault cannot be located, and the master CPU continues user program execution.

Subsequent automatic synchronization can be selected by parameterization. Mode transitions are indicated by I&C alarms.

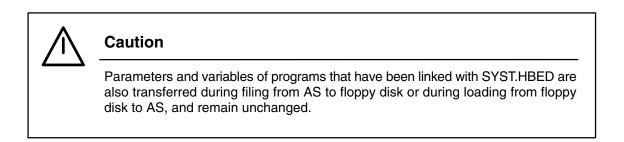

### Caution

If a fault occurs during loading in synchronous mode (M/R, R/M, M/B or B/M), loading is aborted and a restart performed by the central processing unit which is not the master. In so doing, this central processing unit clears its user memory contents.

An exception are faults on N8-H/N-AS or MDA modules which do not trigger a comparator. Mastership changes if the N8–H/N–AS cannot be parameterized in M/R or R/M mode or if a DMA fault caused a permanently present DMA signal. Mastership is **not** changed again if the same fault also occurs in the other CPU.

One of the three I&C alarms S 315 (timing error, DAUERDMA), S 374 (N8–H/N–AS cannot be parameterized) or S 386 (N8–H/N–AS faulty) identifies the defect. Redundancy is maintained since process input/output can still be performed by both CPUs. In order to preserve clarity, Fig. 1.8 only shows mode transitions that start from the left-hand side of the figure.

Corresponding mode transitions are also possible on the right-hand side of the figure, with the right and the left sides of the original reserved.

Fig. 1.8 Mode transition after a fault has occurred

## 2 Method of Operation

## 2.1 Initial Loading of the System Software

Chapter 5 of the AS 235 H Operating Instructions (C79000-B8076-C293) describes the initial loading of the system.

The loading process is not displayed on the master CPU monitor during initial loading of a CPU: It may be displayed, however, if the monitor cable is connected to the BKA 1 of the CPU which is loaded. If no CPU is master, loading of CPU II can be monitored without changing cable connections. It is therefore recommended to start with CPU II if both CPUs are initially loaded from a floppy disk.

• On-line change of the system software

Chapter 2.5.1.1 describes how the system software can be changed without interrupting process execution.

User program execution, however, will be interrupted for approximately eight seconds (depends on the size of the user program structure).

Caution

Only the AS 235 H system software may be loaded.

### 2.2 Start–up Behavior (cf. 1.3.1)

A CPU first executes the RESTART blocks and then the user program if it becomes master during start-up and is in STA mode.

Cf. Chapter 2.3.8 of the AS 235 Variant G Description (C79000-T8076-C416).

## 2.3 Loading and Filing

Loading and filing of user programs takes place as described in the AS 235 Variant G Description (C79000-T8076-C416).

In asynchronous mode, each CPU loads and files only the memory contents of its own local memory module via its MDA. In synchronous mode, the contents of both memory modules (which are identical) are loaded and filed via the master CPU MDA (Cf. Chapter 2.5).

## 2.4 Synchronization

Synchronization of a passive CPU can either be started by pressing a pushbutton on the comparator coupler module (VKB) or by entering commands via the keyboard (see Chapter 2.5.1.1). The pushbutton must be pressed for approximately one second. (Unless the comparator coupler module (VKB) has been switched on there will be no reaction when the pushbutton is pressed). Provided that loading from the mini–diskette unit is not in progress, the two CPUs can only be synchronized if they are in M/P or P/M mode, and have the same module structure.

Both CPUs normally have the same memory size and software revision level (see Chapter 2.5.1.1). Synchronization is aborted and the cause indicated by an I&C alarm (LTM) if these requirements are not met (see Chapter 2.6.3, LTM 820 to 828). The mode transitions to M/B or B/M when synchronization is started. It changes to M/R or R/M once the user memory contents has been transferred from the master CPU to the backup CPU. Both CPUs operate in redundant mode, and have the same memory contents. The second CPU is able to continue user program execution and to assume mastership if the first CPU fails.

The backup process in STA mode takes approximately 1 minute and 40 seconds for 1 MB or approximately 5 minutes for 3 MB. In STO mode, 3 MB takes approximately 40 seconds. The back–up process in STA mode takes approximately 6 minutes and 20 seconds, and in STO approximately one minute if the memory module 6DS1844–8xy is used.

User memory transfer to the backup CPU requires additional execution time. Synchronization should therefore be omitted if cycle overload has occurred or is likely to occur.

See Chapter 2.6 for mode transition indication.

## Caution

The following handling will delete the main memory contents in both central procesing units:

CPU I becomes master and CPU II becomes passive if both CPUs are reset by ZRS in B/M mode. As CPU I was previously in backup mode, its main memory content will be deleted during start–up. At this point in time, CPU II still contains its previous main memory content. If synchronization is now started in M/P mode, CPU II will absorb the blank memory content of CPU I. This means that the main memory content of CPU II will be deleted too.

## 2.5 Keyboard Input

Operator inputs in synchronous mode act upon both CPUs simultaneously.

Operator inputs in asynchronous mode also act upon both CPUs; they are executed by both CPUs but not at the same time. This can be achieved by connecting the keyboards via special cables (with three connectors) to both CPUs.

A switchover unit guarantees that, in asynchronous mode, the monitor always shows the master CPU display. In asynchronous mode, any actions of the passive CPU remain without effect to the master CPU and process execution.

Keyboard and monitor cables may be connected directly to the modules of a CPU (as with an AS 235 system) if the user wishes to utilize only one CPU for operator inputs and to have the screen contents of the CPU displayed, irrespective of the mode selected. This feature may be used for configuration changes during commissioning.

All operator inputs permitted for an AS 235 system are also possible for an AS 235 H system, and have the same effect.

Operator input to the AS 235 H system from a central configuration terminal via the CS 275 bus system is possible provided that one of the two CPUs is master and an N8–H/N–AS can thus be active.

#### 2.5.1 Additional Operator Input and Help Programs

The SYST.HBED program enables H-related operator input and display programs to be started.

A program is called by the following input via the configuring keyboard:

```

SYST, HBED;

BE;

MP=no;

```

(no is the number of one of the subsequently displayed programs)

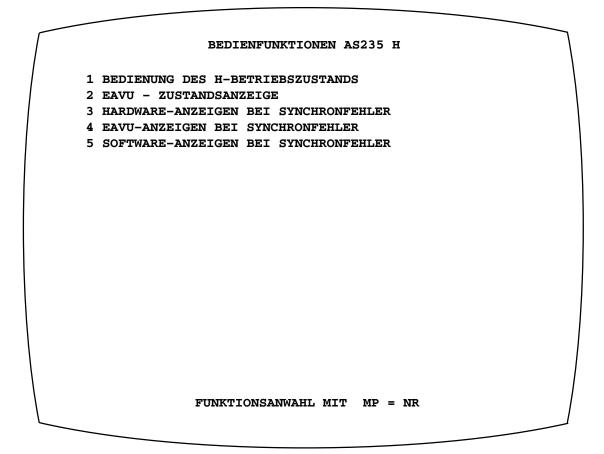

The following menu is displayed on the screen:

Fig. 2.1 Operator input function screen display

#### 2.5.1.1 H Mode Control

Enter MP=1 in SYST.HBED to select this screen form. The program is used for mode selection and parameterizing various system characteristics.

|      | BEDIENUNG DES H-BETRIEBSZUSTANDS                       | ST |

|------|--------------------------------------------------------|----|

| 1M=1 | ZENTRALEINHEIT I WIRD MASTER BEREITS AUFGE-            | 1) |

| 1P=1 | ZENTRALEINHEIT I WIRD PASSIV DATETES ANWEN-<br>DER RAM |    |

| 2M=1 | ZENTRALEINHEIT II WIRD MASTER                          | J  |

| 2P=1 | ZENTRALEINHEIT II WIRD PASSIV                          |    |

| AE=0 | AUTOMATISCH EINSYNCHRONISIEREN IN M/P ODER P/M         |    |

| EE=0 | EINMALIGES EINSYNCHRONISIEREN IN M/P ODER P/M          |    |

| RA=0 | EINSYNCHRONISIEREN, FALLS PASSIV-RAM >= MASTER-RAM     |    |

| SA=0 | WECHSEL DER SYSTEMSOFTWARE ONLINE                      |    |

| VT=1 | TEST VON VKB UND SB IM REDUNDANZBETRIEB M/R BZW. R     | ′м |

|      | UEBERSICHT : MP = 0                                    |    |

$^{1)}\,$  This window which displays the current updating level of the user RAM (and the system RAM after a system software change) is only displayed in the H modes M/B and B/M.

Fig. 2.2 Screen display containing the population of all possible indications in MP=1

• Mode selection

The parameters 1M, 1P, 2M and 2P are used for mode selection. Only such parameters are displayed which may be controlled in the currently selected mode. The related comments are always displayed for all parameters, irrespective of the mode selected.

This parameter may only be altered in STO mode, and may only be set to the value 1.

| 1M=1 | CPU I becomes master                                                                                                                                             |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 1M=1 is only permitted in STO mode and the states:                                                                                                               |

|      | R/M (transition to M/R)<br>P/M (transition to M/P)<br>P/F (transition to M/F).                                                                                   |

|      | Transition in P/M operating state can only be controlled via the master CPU.<br>The AS briefly selects P/P (for up to one second) if input is made in P/M state. |

| 1P=1 | CPU I becomes passive.                                                                                                                                           |

|      | <b>1P=1</b> is only permitted in STO mode and the states:                                                                                                        |

|      | M/R (transition to P/M)<br>R/M (transition to P/M).                                                                                                              |

| 2M=1 | CPU II becomes master                                                                                                                                            |

|      | 2M=1 is only permitted in STO mode and the states:                                                                                                               |

|      | M/R (transition to R/M)<br>M/P (transition to P/M)<br>F/P (transition to F/M).                                                                                   |

|      | Transition in M/P operating state can only be controlled via the master CPU.<br>The AS briefly selects P/P (for up to one second) if input is made in M/P state. |

| 2P=1 | CPU II becomes passive                                                                                                                                           |

|      | 2P=1 is only permitted in STO mode and the states:                                                                                                               |

|      | M/R (transition to M/P)<br>R/M (transition to M/P).                                                                                                              |

|      |                                                                                                                                                                  |

Alterations of the parameters 1M, 1P, 2M and 2P that are not rejected are indicated by I&C alarms (see Chapter 2.6.3, LTM 812 to 817).

An illegal entry is rejected and the error message F 460 is issued. An I&C alarm is not issued.

- Automatic/one-time synchronization

- AE Automatic synchronization <sup>1)</sup>

If **AE=1** (in the master CPU) synchronization always takes place in M/P or P/M mode, even after start–up of one or both CPUs. AE is set to zero if a fault occurs during synchronization. AE is also set to zero if **1P=1** or **2P=1** has been entered and the initial state was M/P or R/M.

The initialization value after a first-time run is **AE=1**, after memory clearing **AE=0**.

EE One-time synchronization <sup>1)</sup>

EE can only be altered in M/P or P/M state. If  $\mathbf{EE=1}$  (in the master CPU) synchronization always takes place in M/P or P/M mode. EE is set to zero during synchronization (or when synchronization is aborted) or during start–up.

The initialization value after a first-time run or memory clearing is zero.

• Uprating the memory configuration in online mode

**RA=0** Synchronization is not to be performed with different memory configurations.

Normally both central processing units have the same memory configurations, i.e. **RA=0** (no uprating)

#### **RA=1** Synchronization is to be performed if the memory configurations differ

Using this parameter, the AS memory configuration can be uprated online. During synchronization with **RA=1** it has to be noted, however, that the memory size of the passive CPU **must** be larger than that of the master CPU.

Proceed as follows:

Switch off one CPU and uprate the memory module of this CPU to the memory capacity requested.

Switch on this CPU and bootstrap the system software.

Set **RA=1** to synchronize the CPU. Then switch off the second CPU and uprate its memory card as well. Switch on the second CPU and bootstrap the system software. Set **RA=1** to synchronize the CPU.

Uprating is finished now – both CPUs have been uprated – the uprate memory configuration is available now.

RA may only be altered in M/P or P/M states.

RA is set to zero during synchronization and when synchronization is aborted. Synchronization is aborted and an I&C alarm issued if the memory size of the passive CPU is smaller than the memory size of the master CPU (see Chapter 2.6.3).

The initialization value after a first-time run or memory clearing is zero.

<sup>&</sup>lt;sup>1)</sup> There will be no reaction to the AE and EE parameters unless the comparator coupler module (VKB) has been switched on.

- Upgrading the system software

- **SA=0** Synchronization is not to be performed with different system software versions.

- **SA=1** Synchronization is to be performed with different system software versions. The software version of the passive CPU is to be adopted in both CPUs.

SA is set to zero during synchronization and when synchronization is aborted. SA may not be altered in M/B or B/M state. The initialization value after a first-time run or memory clearing is zero. How to proceed during a system software change is described in the below examples.

A bumpless change (with regard to the process variables) from one system software version to another is possible if the process tolerates a dead time of approximately 8 seconds during execution level stop and subsequent restart. (The restart which is always necessary after a new system software version has been loaded is performed automatically).

The watchdogs of the I/O bus interface units are triggered during start–up. The outputs of the output modules (analog/binary) are not reset. The control module watchdogs, however, are not triggered during start–up. The cycle–time of the control module watchdogs must be set to its maximum value (16 seconds) before the system software is changed. A shorter cycle time may be selected once the system software has been changed. RESTART blocks are not processed during this special start–up.

The time is reset after start–up (as after ZRS). Bus messages may be lost as the N8–H/N–AS is parameterized during start–up. The specified duration of 8 seconds is an average value which depends on the size of the user structures.

### Caution

Proper program continuation is not guaranteed if a system software change is interrupted by NAU, ZRS, RSOF, LOES, or loading from floppy disk or bus. • Examples of a system software change:

CPU I executes the user program with system software version X (CPU II: standby or passive).

1) CPU II is to be booted with system software version Y:

Set the switch on the memory module front panel to BOOT and press the ZRS push–button on the CPU front panel at the same time.

CPU II performs loading and assumes passive mode

2) The following inputs enable synchronization:

```

SYST,HBED;

BE;

MP=1;

SA=1;

```

The CPU status has not yet changed.

3) Synchronization via keyboard

Input: **EE=1;** or **AE=1;**

Synchronization is also possible by pressing the BU pushbutton on the VKB front panel.

The subsequent transfer of the user memory contents from CPU I to CPU II is performed while CPU I and CPU II execute the user program in synchronous operation (using system software version X).

Sequence list execution is stopped at the end of the lists when this process is terminated. The user program assumes a defined state. Both units briefly transition to STO mode. The watchdogs of the I/O interface modules are triggered during this process (see above).

CPU I automatically assumes passive mode now. CPU II, the new master, uses the new system software Y for performing a restart, and transitions to STA mode (provided that STA was the mode before the change).

From now on, system software version Y is used for executing the user program.

CPU I is now synchronized automatically. The system software (version Y) and the user memory contents are the transferred from CPU II to CPU I. Both CPUs utilize the new system software Y.

If there is a restart due to a change in master while the operator is entering configuration data via the bus system, the bus connection will be interrupted. The bus connection can be set up again by signing off and then on again.

The appendix contains the upgrading instructions for the memory module 6DS1844–8xy and system software version G.

- Testing the comparator

- VT=1 The comparator coupler module (VKB) and the synchronization module are tested in redundant mode (M/R or R/M). This parameter is only required by system specialists who use logic analysers for performing certain hardware tests while VT=0. This parameter should be 1 in normal operation.

All possible operator inputs are displayed on the process communication keyboard (PBT). Dynamic PBT annotation is not performed.

### 2.5.1.2 EAVU Status Display

This SYST.HBED screen form is selected by MP=2. This program displays the EAVU functions, the allocation of the EAVU modules to the slot addresses of the I/O modules, and to the words 0 to 2 (alarms 1 to 48) of the 6DS1601–8BA interrupt module.

#### Example:

|                   |                                          | EAVU-ZUSTANDSANZEIGE                                        |    |    | _     |   |

|-------------------|------------------------------------------|-------------------------------------------------------------|----|----|-------|---|

|                   | EA                                       | VU - ZUSTAND IM GRUNDSCHRANK                                |    |    |       |   |

| EAVU              | EIN/AUS                                  | STECKPLATZADRESSEN                                          | IN | т- | ADR . | • |

| 0                 | EIN                                      | 0-11                                                        | 0  |    | D     |   |

| 1                 | EIN                                      | 16-27                                                       |    | 1  | F     | I |

| 2                 | EIN                                      | 32-43                                                       |    |    | 2     | S |

|                   |                                          | USTAND IM ERWEITERUNGSSCHRANK                               |    |    |       |   |

|                   | EIN/AUS                                  | STECKPLATZADRESSEN                                          |    |    |       |   |

| 100               | EIN/AUS<br>EIN                           | STECKPLATZADRESSEN                                          |    |    |       |   |

| 100<br>101        | EIN/AUS<br>EIN<br>AUS*                   | STECKPLATZADRESSEN<br>100-111<br>132-143                    |    |    |       |   |

| 100               | EIN/AUS<br>EIN<br>AUS*<br>AUS            | STECKPLATZADRESSEN                                          |    |    |       |   |

| 100<br>101<br>102 | EIN/AUS<br>EIN<br>AUS*<br>AUS<br>IS=2 SW | STECKPLATZADRESSEN<br>100-111<br>132-143<br>100-111 116-131 |    | (G | :S)   |   |

#### Interpretation:

- EAVU 0 This module is installed in the basic cabinet; has been switched on; is responsible for slot addresses 0 to 11 and primarily responsible for word 0 (alarms 1 to 16) of the group interrupt module; one interrupt is pending for a too long time.

- EAVU 1 This module is installed in the basic cabinet; has been switched on; is responsible for slot addresses 16 to 27 and primarily responsible for word 1 (alarms 17 to 32) of the group interrupt module: too many interrupts have occurred.

- EAVU 2 This module is installed in the basic cabinet; has been switched on; is responsible for slot addresses 32 to 43 and primarily responsible for word 2 (alarms 33 to 48) of the group interrupt module; the interrupts were inhibited via keyboard operation.

- EAVU 100 This module is installed in the extension cabinet; has been switched on; is responsible for slot addresses 100 to 111.

- EAVU 101 This module is installed in the extension cabinet; has been switched off by an EAVU driver block (PRS signal of the EAVU driver is 1); is responsible for slot address 132 to 143 when it is switched on.

- EAVU 102 This module is installed in the extension cabinet; has been switched off by the system software as the slot address responsibility was overlapping with EAVU 100 (slot addresses 100 to 111 have been selected again).

- EAVU 103 This module is installed in the extension cabinet; has been switched off by the system software as jumper register I (value 08H) and jumper register II (value 09H) are not identical (jumper register I states that the EAVU is responsible for slot addresses 148 to160; jumper register II implies additional responsibility for slot addresses 100 to 111)

- Fig. 2.3 EAVU screen display

The system software performs a check in order to be able to create the EAVU status display. This check is performed for all EAVU modules after each master CPU start–up (power ON, ZRS or RSOF); it is only locally performed if the power is switched on for an extension unit only.

The check is performed as follows:

The QVZ signal that results from an EAVU access is used for creating the information whether or not the I/O comparator and switchover module (EAVU) has been installed. Subsequently the jumper settings I and II on the EAVU are checked for identity. These settings, which should be redundant, specify the slot addresses of the I/O modules and the group interrupt module the EAVU is responsible for. The checked EAVU is switched off and the I/O modules of the extension unit containing the EAVU are reset if the jumper settings are not identical or if they overlap with the setting on a previously checked EAVU. EAVU 102 of the example on the previous page was switched off since its responsibility for slot addresses 100 to 111 was overlapping with the responsibility of EAVU 100. The exact reaction with regard to the I/O module is as follows:

- The outputs of the output modules (binary/analog) are reset (depending on the ARS jumper)

- The closed–loop control modules change from mode C (compute) to mode A (automatic)

- 2-channel closed-loop control modules, backplane connector 2, CB signal to 0

The EAVU is switched on and the reset signal for the I/O modules de–activated if the jumper settings are identical and do not overlap with a previously checked EAVU.

The check of the EAVU jumper settings follows the ascending EAVU numbers.

It takes the system software approximately 8 seconds to detect that the power supply of an extension unit has been switched off.

The EAVU driver block offers further display and control functions for the EAVU (see Chapter 3.2.2). The EAVU is switched off if the peripheral reset signal has been issued via the EAVU driver (PRS input of the EAVU block is 1). This is marked by an asterisk (\*) next to "AUS" [OFF] in the above table. The EAVU remains de–activated (even after power off, ZRS, or RSOF) in this case until it is re–activated by an EAVU driver (PRS input of the EAVU block is 0; cf. Chapter 3.2.2).

### Caution

An EAVU remains de-activated if the EAVU driver which has issued the peripheral reset signal for this EAVU is cleared. It can only be re-activated by an EAVU driver which cancels the reset signal for this EAVU.

### 2.5.1.3 Hardware Flags after Synchronization Faults

Selecting MP=3 in SYST.HBED activates this screen display. This program displays the fault states of CPU I and CPU II. The last 10 events, together with date and time, are retained in a table. The values determined by the hardware can be displayed for both CPUs (see Fig. 2.4).

The fault type (F–TYP) specifies during which type of access the fault has occurred. The contents of VKB register 1 is displayed as a hexadecimal value (e.g. 01(H)S means "asynchronous memory bus during write operation"). An L or S at the end indicates whether the fault has occurred during a read (L) or a write (S) operation; an N at the end indicates an N8–H/N–AS fault. The following table summarizes the meanings of the individual bits of this value:

| Address | Bit<br>(1-active) | Meaning                         |

|---------|-------------------|---------------------------------|

|         | 0                 | Asynchronous memory bus         |

|         | 1                 | Asynchronous peripheral bus     |

|         | 2                 | Fault on memory data bus        |

| 4FD0H   | 3                 | Fault on peripheral address bus |

|         | 4                 | Fault on peripheral data bus    |

|         | 5                 | Fault in I/O area 1             |

|         | 6                 | Fault in I/O area 2             |

Reading (MEMR) the fault type

Table 2.1 VKB register 1

| HARDWARE-ANZEIGEN BEI SYNCHRONFEHLER                      |                                                 |                                          |                                       |                                       |                                           |  |  |  |

|-----------------------------------------------------------|-------------------------------------------------|------------------------------------------|---------------------------------------|---------------------------------------|-------------------------------------------|--|--|--|

| datum <sup>1</sup>                                        | UHRZEIT <sup>1</sup>                            | F-TYP<br>Ze I                            | BGR<br>ZE I                           | F-TYP<br>ZE II                        | BGR<br>ZE II                              |  |  |  |

| <pre>→ 5.12.90/ 5.12.90/ 5.12.90/ 5.12.90/ 5.12.90/</pre> | 00.00.17.<br>06.07.54<br>03.01.50.<br>03.00.22. | 01(H)S<br>01(H)L<br>01(H)<br>01(H)L<br>2 | 00(D)<br>00(D)<br>01(D)<br>00(D)<br>3 | 00(H)<br>00(H)<br>00(H)<br>00(H)<br>2 | 00 (D)<br>00 (D)<br>00 (D)<br>00 (D)<br>3 |  |  |  |